## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2017/0261949 A1 HOFFMANN et al.

#### Sep. 14, 2017 (43) **Pub. Date:**

#### (54) APPARATUS AND METHOD FOR **OPTIMIZING QUANTIFIABLE BEHAVIOR** IN CONFIGURABLE DEVICES AND **SYSTEMS**

- (71) Applicant: University of Chicago, Chicago, IL

- (72) Inventors: Henry HOFFMANN, Chicago, IL (US); John LAFFERTY, Evanston, IL (US); Nikita MISHRA, Chicago, IL (US)

- (73) Assignee: University of Chicago, Chicago, IL (US)

- Appl. No.: 15/457,743

- (22) Filed: Mar. 13, 2017

#### Related U.S. Application Data

(60) Provisional application No. 62/307,210, filed on Mar. 11, 2016.

#### **Publication Classification**

(51)Int. Cl. G05B 13/04 (2006.01)G05B 13/02 (2006.01)G06N 99/00 (2006.01)

U.S. Cl. CPC ...... G05B 13/041 (2013.01); G06N 99/005 (2013.01); **G05B** 13/0265 (2013.01)

#### (57)ABSTRACT

An apparatus and method are provided to perform constrained optimization of a constrained property of an apparatus, which is complex due to having several components, and these components are configurable in real-time. The optimization is achieved by detecting values of the constrained property and a plurality of other properties of the apparatus when the apparatus is configured in a first subset of the plurality of configurations. A model is learned using the detected values of the constrained property. The model represents the constrained property and can also represent other properties as a function of the configurations. The model can also include estimated uncertainties of the constrained property in the model. Then, using the d model and the estimated uncertainties, the optimal configuration can be selected to minimize an error value (e.g., the difference between a desired value and an observed value of the at least one constrained property).

FIG. 1A

FIG. 1B

FIG. 2A

FIG. 2B

#### 210

FIG. 2C

220

Retrieve a database of performance data, the database can include, e.g., the device using various computational configurations to execute other applications and/or other devices using various computational configurations to execute various applications

222

Compare the performance-data table with the retrieved database to find combinations of devices and applications having similar computational performance and power consumption as a function of computational configuration

224

Estimate a performance model of the device when executing the application, the performance model including the computational performance and power consumption for all computational configuration of the device when executing the application based on the performance-data table and similar performance data from the database

226

FIG. 2D

FIG. 2E

### <u>230'</u>

Determine, using the performance model, an optimal-efficiency configuration corresponding to maximum ratio between computational performance and power consumption of the device when executing the application, and set the device in the optimal-efficiency configuration

232'

Determine a speedup factor for the optimal-efficiency configuration to complete computational tasks within a desired time period

234'

Accelerate completion of the computational tasks using approximate computing to trade-off accuracy for increased speed

236'

Update the performance model according to continued measurements of the computational performance and power consumption of the device when executing the application

Is the application complete?

238'

Yes

FIG. 3 Small data set of performance data

| \       | Loop<br>/ariable | Normalized performance | Normalized consumption | , | Loop<br>Variable | Clock<br>rate | # of additional cores |  |

|---------|------------------|------------------------|------------------------|---|------------------|---------------|-----------------------|--|

| \$<br>X | #id              | speedup                | powerup                | * | #id              | frequency     | cores                 |  |

| 2       | 0                | 1                      | 1                      | 2 | 0                | 250000        | 0                     |  |

| 3       | 1                | 1.20                   | 1.09                   | 3 | 1                | 300000        | 0                     |  |

| 4       | 2                | 1.40                   | 1.16                   | 4 | 2                | 350000        | 0                     |  |

| S       | 3                | 1.60                   | 1.30                   | 5 | 3                | 400000        | 0                     |  |

| 6       | 4                | 2.12                   | 1.35                   | ó | 4                | 250000        | 1                     |  |

| 7       | 5                | 2.53                   | 1.50                   | 7 | 5                | 300000        | 1                     |  |

| 8       | 6                | 2.88                   | 1.64                   | 8 | 6                | 350000        | 1                     |  |

| 9       | 7                | 3.18                   | 1.69                   | 9 | 7                | 250000        | 2                     |  |

|         |                  |                        |                        |   |                  |               |                       |  |

FIG. 4A

FIG. 4B

# FIG. 5

$y_i$ : Vector of power consumption by the  $i^{th}$  application for different configurations.

FIG. (

FIG. 7

FIG. 9

FIG. 12A

FIG. 12B

FIG. 14C

FIG. 16A

FIG. 16B

FIG. 17

FIG. 18

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27A

FIG. 27C

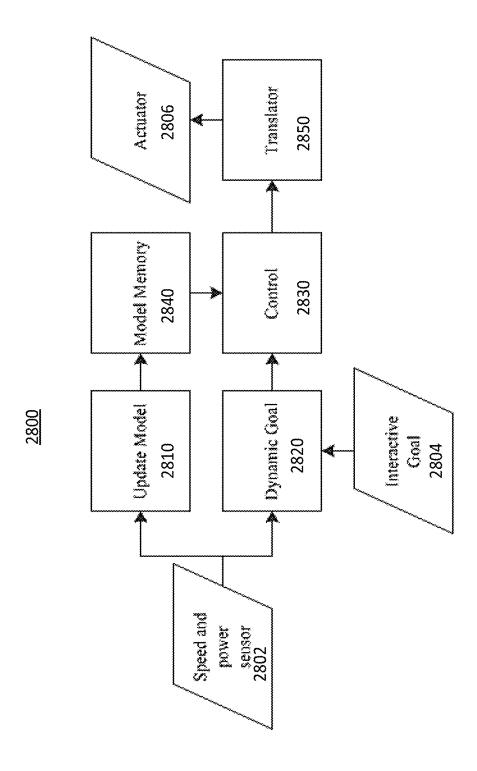

FIG. 28

FIG. 2

FIG. 30

550 cycles Control calculation -Action frequencyr K 500 cycles Frequency overhead Sensor sampling and Update model

FIG. 31

FIG. 32

FIG. 33

## APPARATUS AND METHOD FOR OPTIMIZING QUANTIFIABLE BEHAVIOR IN CONFIGURABLE DEVICES AND SYSTEMS

## CROSS REFERENCE TO RELATED PAPERS

[0001] This application is based upon and claims the benefit of priority to provisional U.S. Application No. 62/307,210, filed Mar. 11, 2016, the entire contents of which are incorporated herein by reference.

## **FIELD**

[0002] This disclosure relates to a method and apparatus for selecting a computational configuration of an electronic device executing an application in order to improve energy consumption and computational production, and, more particularly to optimizing energy consumption and computational production using a performance model that is based on similarities between a small number of computational configurations of the device executing the application using and a database of other devices, applications, and computational configurations.

## **BACKGROUND**

[0003] The background description provided herein is for the purpose of generally presenting the context of the disclosure. Work of the presently named inventors, to the extent the work is described in this background section, as well as aspects of the description that may not otherwise qualify as prior art at the time of filing, are neither expressly nor impliedly admitted as prior art against the present disclosure

[0004] Energy consumption plays an important role for the full range of computing systems spectrum from small mobile computing devices such as smartphones and wearable technology, in which energy consumption determines the battery life of the mobile device, and extending to the other end of the spectrum including supercomputers, in which energy consumption affects costs and cooling requirements. Power management is especially important in mobile computing and personal wireless devices such as smartphones and smart wearable technology. As processors have become smaller and more powerful and as computer memory has increased in density and capacity, battery technology has not kept pace. For example, from 1990 to 2000 disk capacity increased by a factor of 1000, CPU speed increased by a factor of 400, available RAM increased by a factor of 100, wireless bandwidth increased by a factor of twelve, but the energy density of battery increased by only a factor of three.

[0005] The absence of large improvements in battery technology increases the importance of efficiently using energy from the batteries. Even fixed computing devices benefit significantly from improved efficiency. Thus, energy conservation and power management have become two of the most important challenges in modern computing systems, including general purpose computers and mobile devices.

[0006] In 2015, data centers consume approximately 2% of all US electricity, and data centers increase consumption at a rate of 15% annually. Thus, data centers are projected to consume 8% of U.S. power by 2020. Improved operation techniques in data center are needed to make it more

economically and ecologically sustainable and scalable. High power also means high temperature, which has many other adverse side effects such as decrease of system reliability,

[0007] Energy conservation is also important to battery operated mobile computing devices such as smartphones. Insufficient battery life has is a primary factor in consumer dissatisfaction with modem mobile devices. While mobile computing have become increasing integrated and indispensable in everyday lives for communication, sensing, controlling and entertainment, the increasing complexity of hardware and applications in the mobile devices greatly outpaces the development of battery technology. For example, the improvements from Samsung Galaxy S to Samsung Galaxy S3 correspond to a 5.9 factor increase in CPU performance increases, but the battery capacity only increased by a factor of 1.4.

[0008] In certain situations, a goal of power management for a battery powered mobile computing device is to minimize the likelihood that the battery depletes before the device can be recharged while simultaneously providing a high quality of service. Various aspects of the computational configuration can be adjusted and tuned to achieve these competing objectives. Further, the optimal configuration for one combination of mobile device and application being executed on the mobile device may not be optimal for another combination of device and application.

[0009] Thus, the optimal computational configuration can depend on the architecture of the mobile device and the application being executed on the mobile device. Generally, a computational device will be configurable over a configuration space, including: the number and combination of cores, clockspeed, hyperthreading, and memory controllers, for example. Thus, optimizing the computational configuration can be represented as a constrained optimization problem, with the exact form of the optimization depending on the specified goals of the optimization. For example, the goal may be to guarantee the battery is not exhausted within a predefined window while maintaining a minimum quality of service. Alternatively, the goal may be to complete the most computational tasks before the battery is exhausted.

[0010] Generally, finding the optimal computational configuration depends on applying an accurate model of the computational performance and energy consumption of the device executing the application. However, obtaining a model can be challenging because, generally, the model will be device dependent, with different devices having different performance and consumption characteristics. Further, the model will be application dependent. For example, some applications will being more conducive to parallel execution on multiple cores, while others will require significant communication overhead and become less efficient when executed on multiple cores.

[0011] Certain rules of thumb or heuristics have been developed as being nearly optimally efficient for a limited number of device-application combinations. Two such heuristics are the race-to-idle and never-idle heuristics. The computational task can be defined as executing an application within a predefined time window. According to the race-to-idle heuristic, all of the computational resources are allocated to the application and once the application is finished the system goes to idle for the remaining duration of the predefined time window. This strategy incurs almost no runtime overhead, but may be suboptimal in terms of

energy, since maximum resource allocation is not always the best solution to the energy minimization equation. In the never-idle heuristic the device is configured to work at a constant rate while allocating only enough resources to complete the application coincidently with the end of the predefined time window. Depending on the device a never-idle computational configuration might be closer to optimal than a race-to-idle configuration, whereas another device might be the opposite.

[0012] Thus, on the one hand, these heuristics cannot be consistently relied on for the optimal configuration. However, on the other hand, measuring the performance and consumption of a device-application combination for each possible computational configuration to develop a comprehensive model can be a time and energy consuming process. Ideally, a reliable model of computational performance and power consumption could be obtained for a device-application combination without comprehensive testing every time a new application or combination of applications is run on the device. To this end, described herein is a method and apparatus for simultaneously optimizing computational performance and energy consumption by using a model of the device performance based on less than comprehensive testing of computational configurations of the device.

## DESCRIPTION OF THE DRAWINGS

[0013] A more complete understanding of this disclosure is provided by reference to the following detailed description when considered in connection with the accompanying drawings, wherein:

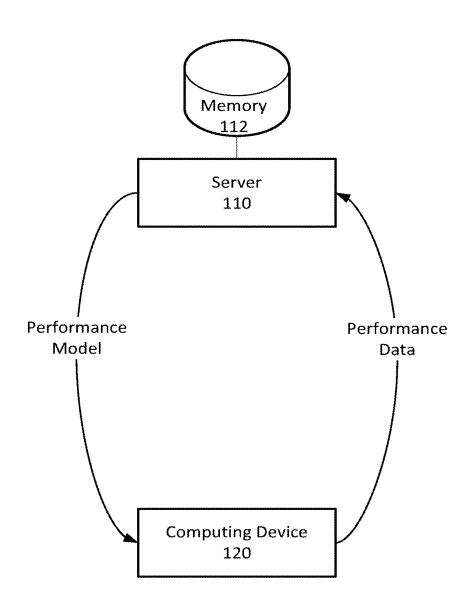

[0014] FIG. 1A shows a schematic diagram of a server communicating with a device, according to one implementation:

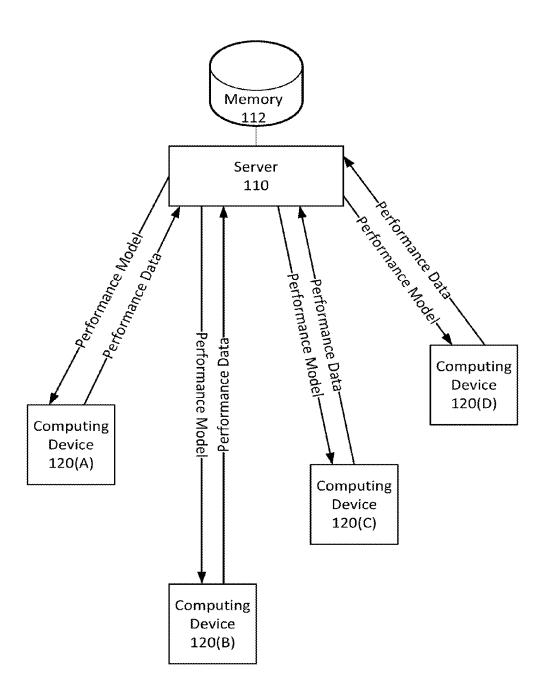

[0015] FIG. 1B shows a schematic diagram of a server communicating with several mobile devices, according to one implementation;

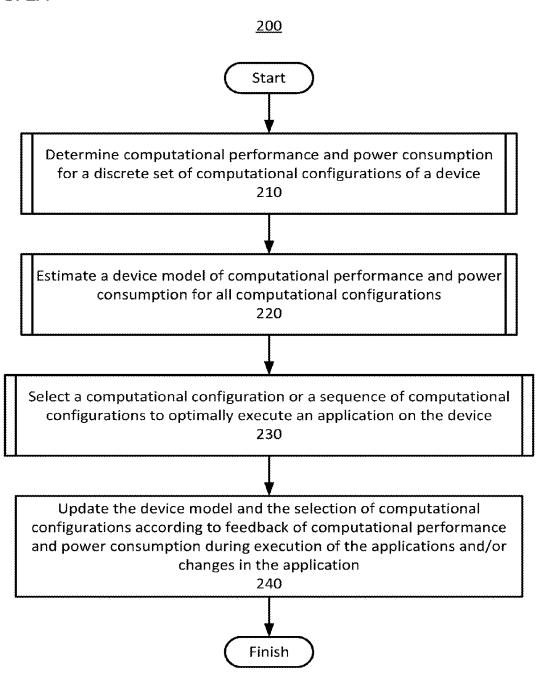

[0016] FIG. 2A shows a flow diagram of an example of a method to determine an energy efficient configuration of a device when executing an application, according to one implementation;

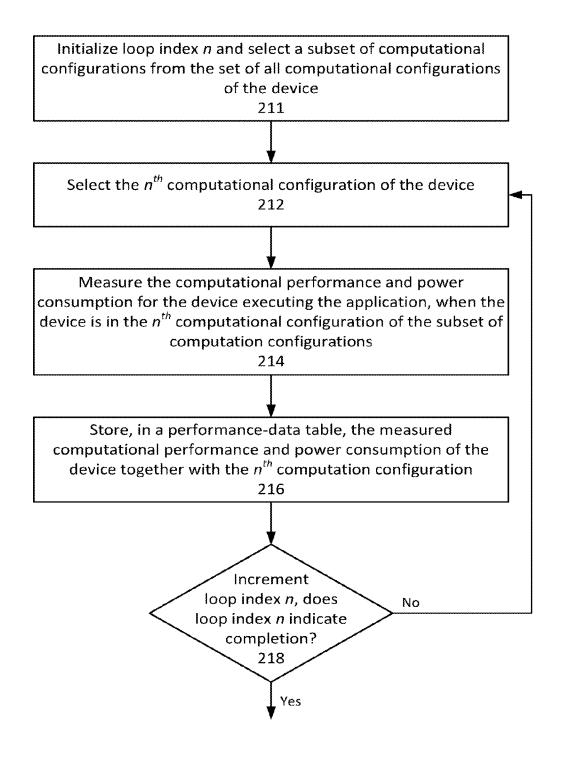

[0017] FIG. 2B shows a flow diagram of an example of a process to generate performance characteristics corresponding to some configurations of the device when executing the application, according to one implementation;

[0018] FIG. 2C shows a flow diagram of an example of a process to determine performance model of the configurations of the device when executing the application, the performance model being generated using a comparison between the generated performance characteristics and a database of performance characteristics of various other devices executing various other applications, according to one implementation;

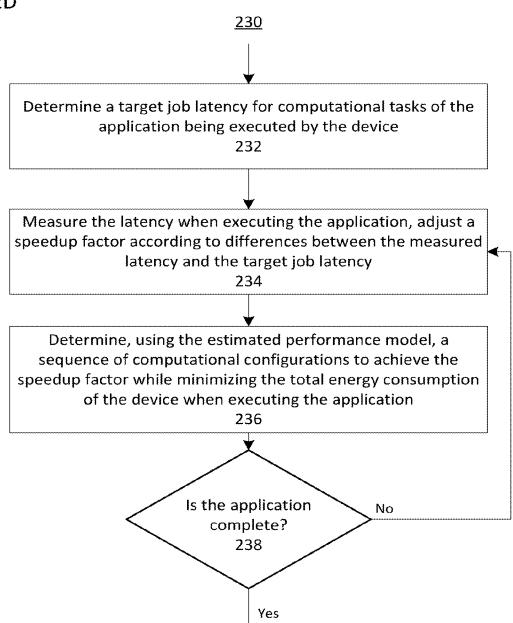

[0019] FIG. 2D shows a flow diagram of an example of a control process to control the configuration of the device using the performance model of the device when executing the application, according to one implementation;

[0020] FIG. 2E shows a flow diagram of another example of a control process to control the configuration of the device using the performance model of the device when executing the application, according to one implementation;

[0021] FIG. 3 shows a schematic diagram of a performance model the device when executing the application, according to one implementation;

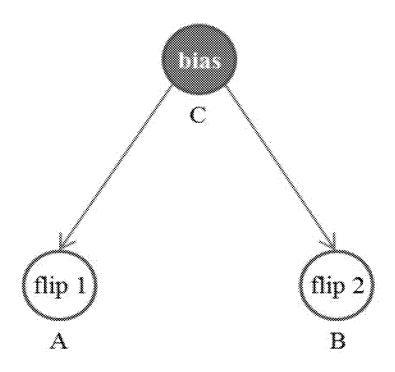

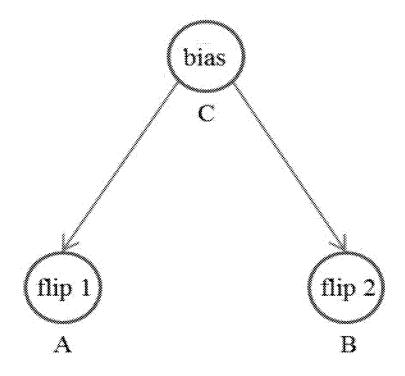

[0022] FIG. 4A shows a schematic diagram of an example of a simple directed graph with nodes A and B depending from an observed node C;

[0023] FIG. 4B shows a schematic diagram of an example of a simple directed graph with nodes A and B depending from an unobserved node C;

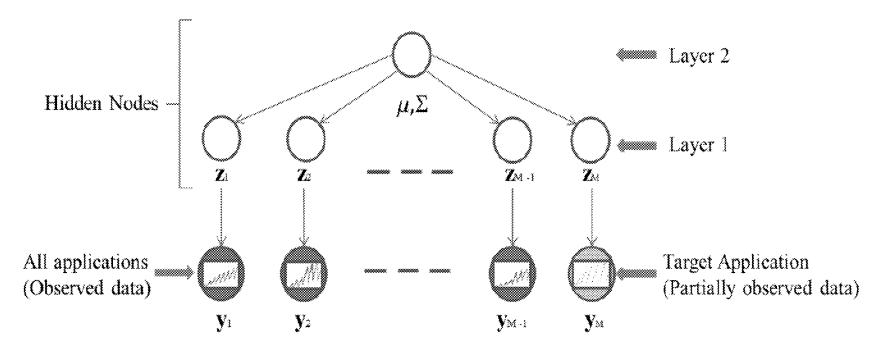

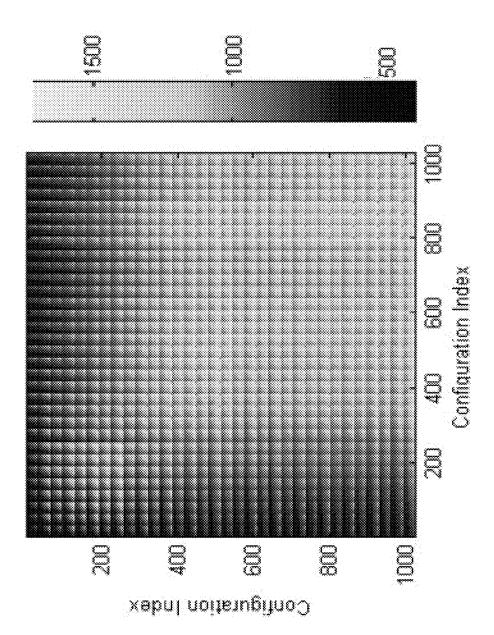

[0024] FIG. 5 shows a schematic diagram of a hierarchical Bayesian model (HBM), according to one implementation; [0025] FIG. 6 shows an example of a plot of correlations among computational configurations;

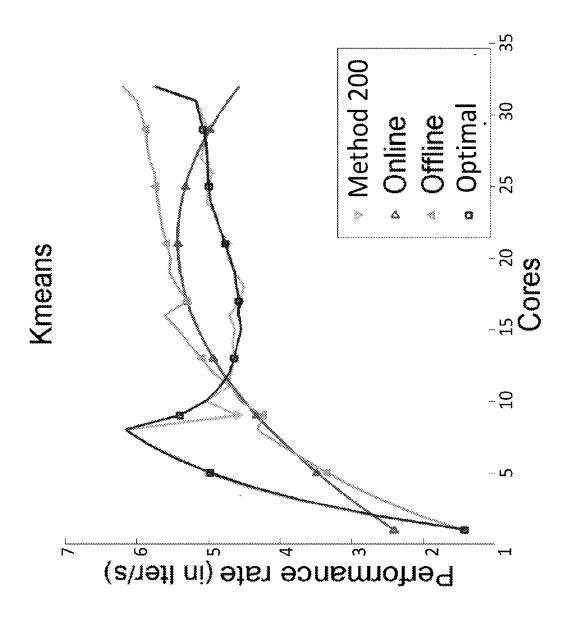

[0026] FIG. 7 shows an example of a plot of performance estimates for configuration-optimization methods as a function of the number of cores according to one implementation:

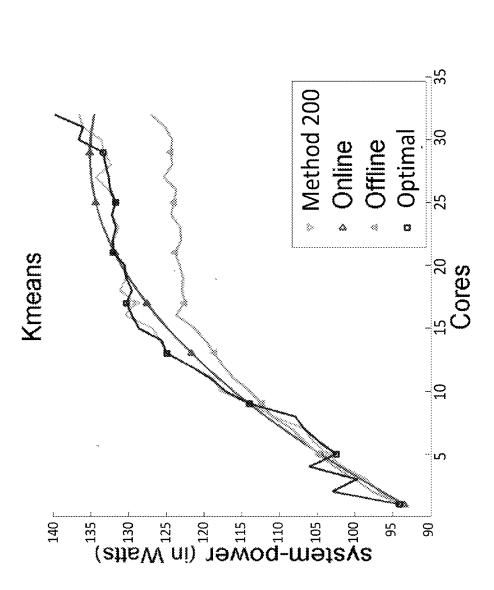

[0027] FIG. 8 shows an example of a plot of estimates of power consumption for the respective configuration-optimization methods as a function of the number of cores, according to one implementation;

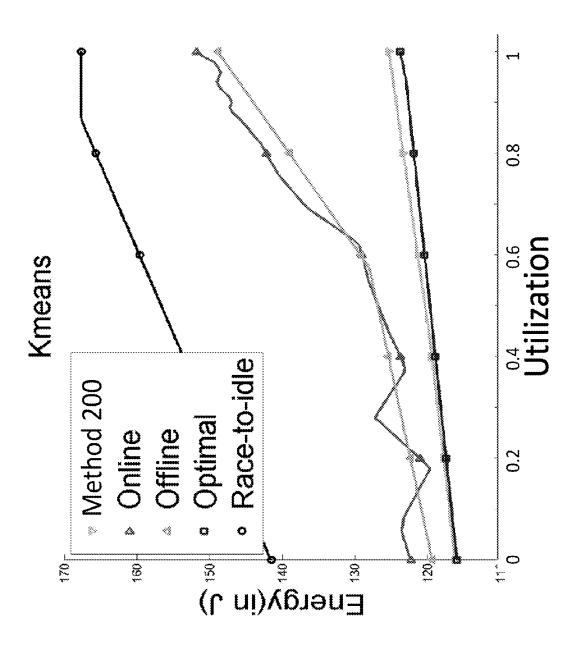

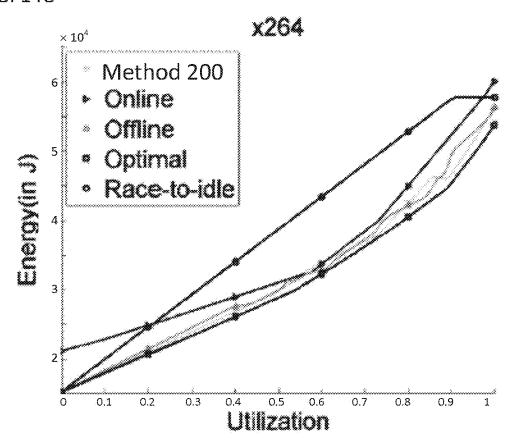

[0028] FIG. 9 shows an example of a plot of the energy of the minimal energy configuration for various system utilizations, according to one implementation;

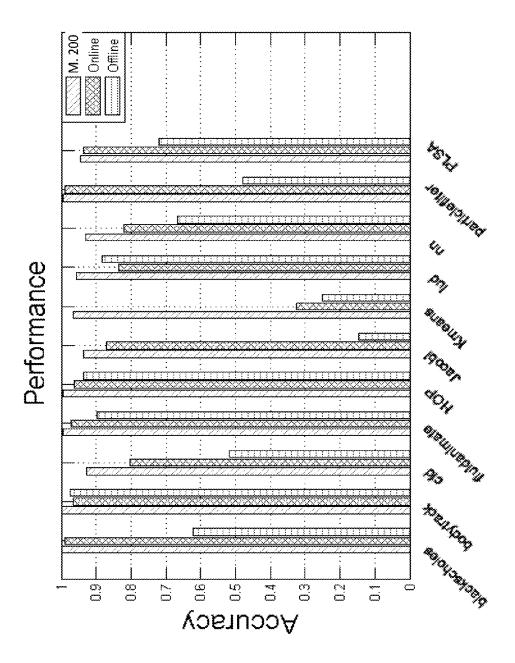

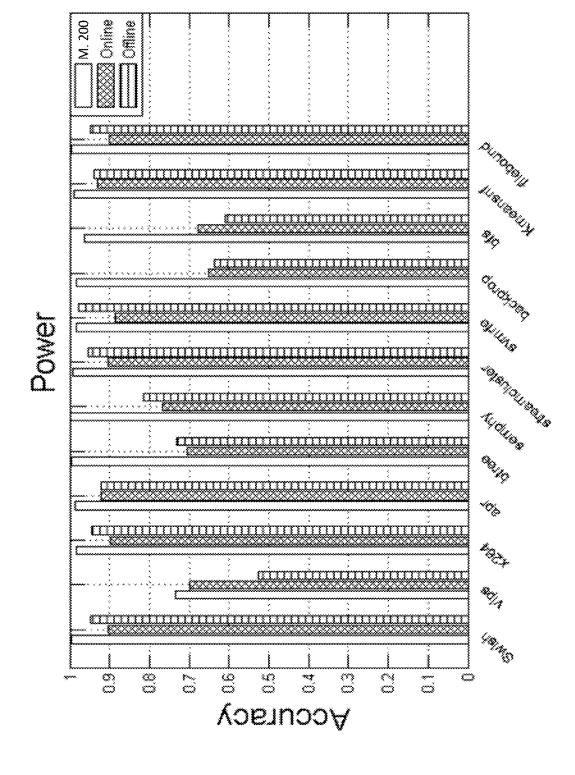

[0029] FIG. 10A shows a bar plot comparing the accuracy of performance estimates by three different optimization techniques for 11 different benchmark applications, according to one implementation;

[0030] FIG. 10B shows a bar plot comparing the accuracy of performance estimates by three different optimization techniques for 14 other benchmark applications, according to one implementation;

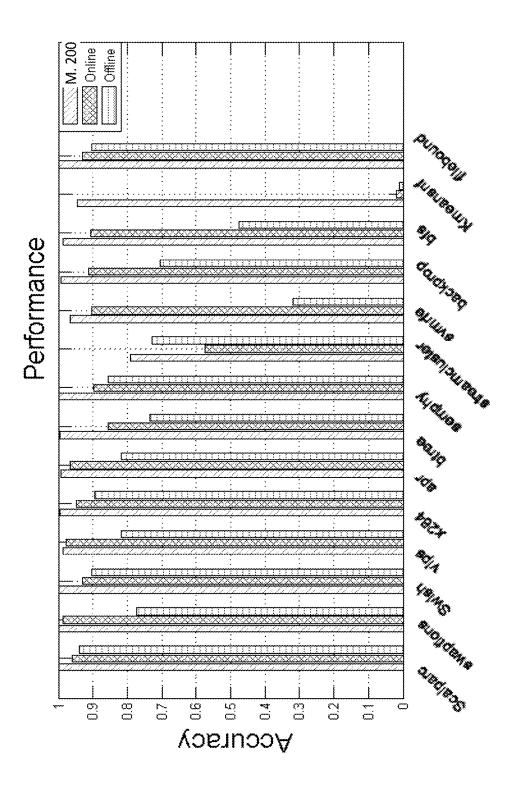

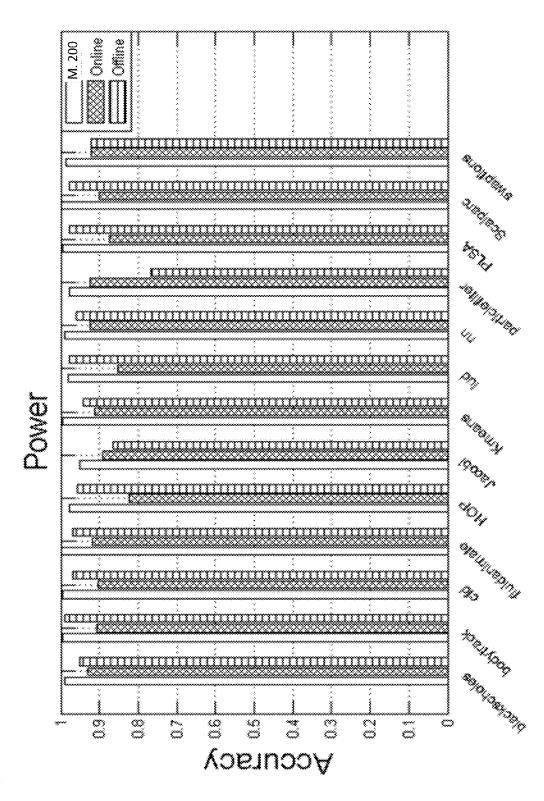

[0031] FIG. 11A shows a bar plot comparing the accuracy of power estimates by three different optimization techniques for 13 different benchmark applications, according to one implementation;

[0032] FIG. 11B shows a bar plot comparing the accuracy of power estimates by three different optimization techniques for 12 other benchmark applications, according to one implementation;

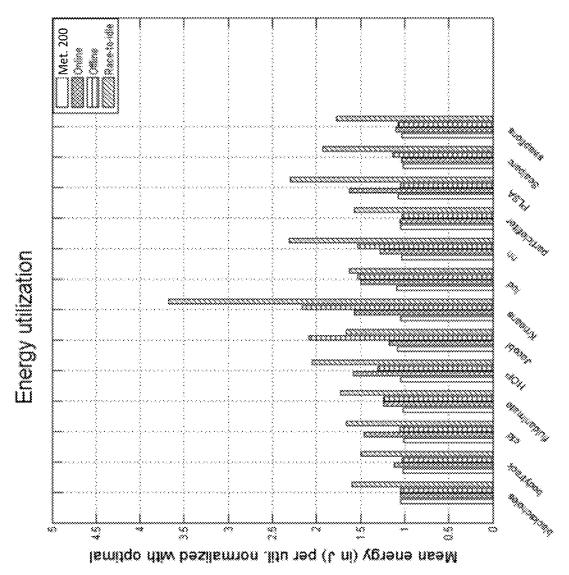

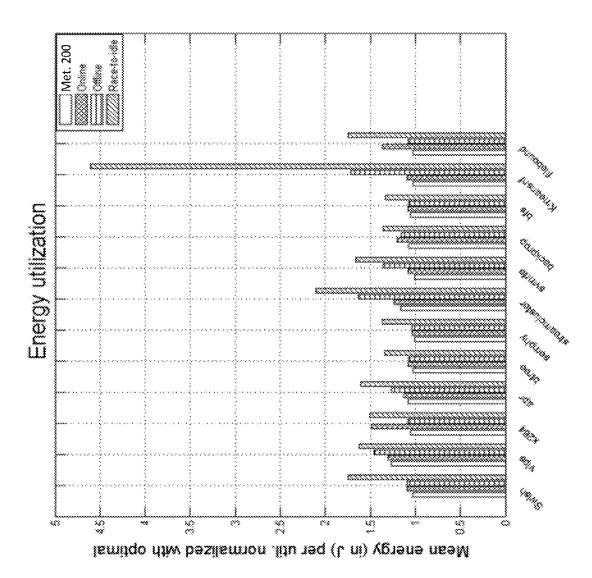

[0033] FIG. 12A shows a bar plot comparing the mean energy of optimal configurations determined according to four different optimization techniques for 13 different benchmark applications, according to one implementation;

[0034] FIG. 12B shows a bar plot comparing the mean energy of optimal configurations determined according to four different optimization techniques for 12 other benchmark applications, according to one implementation;

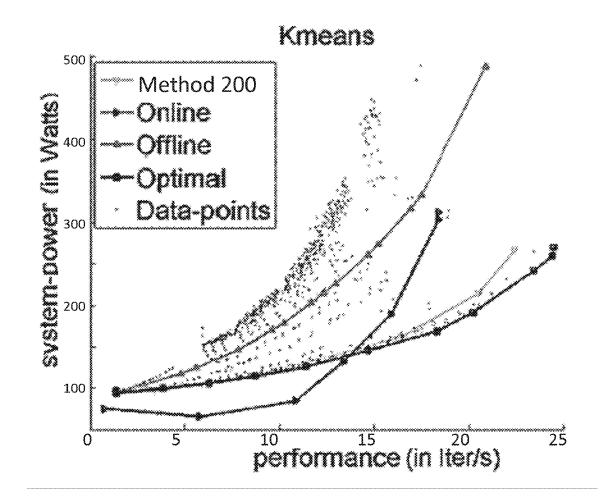

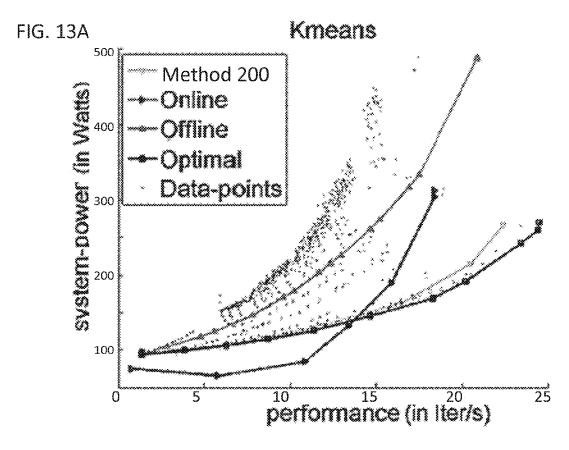

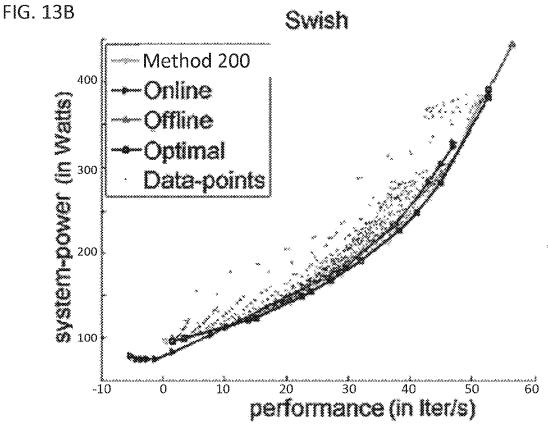

[0035] FIG. 13A shows a plot of a convex hull of the power-performance tradeoff space for the device executing a Kmeans application for various optimization techniques; [0036] FIG. 13B shows a plot of a convex hull of the power-performance tradeoff space for the device executing a swish application for various optimization techniques;

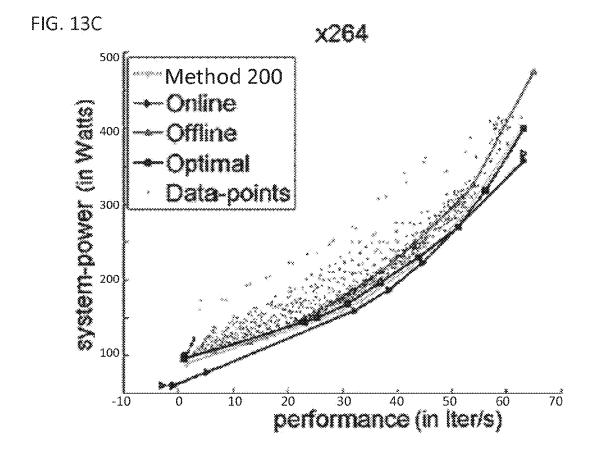

[0037] FIG. 13C shows a plot of a convex hull of the power-performance tradeoff space for the device executing an x264 application for various optimization techniques;

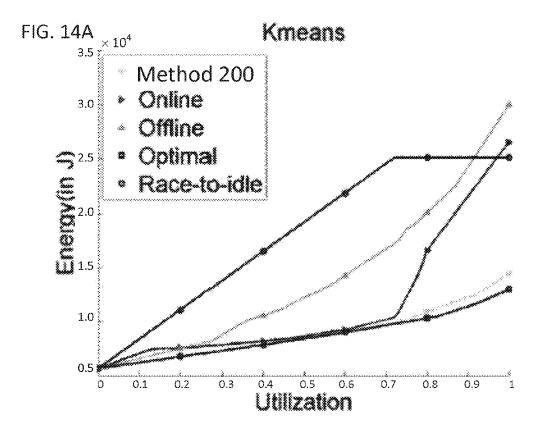

[0038] FIG. 14A shows a plot of the energy consumed as a function of utilization for the device executing a Kmeans application for various optimization techniques;

[0039] FIG. 14B shows a plot of the energy consumed as a function of utilization for the device executing the Kmeans application for various optimization techniques;

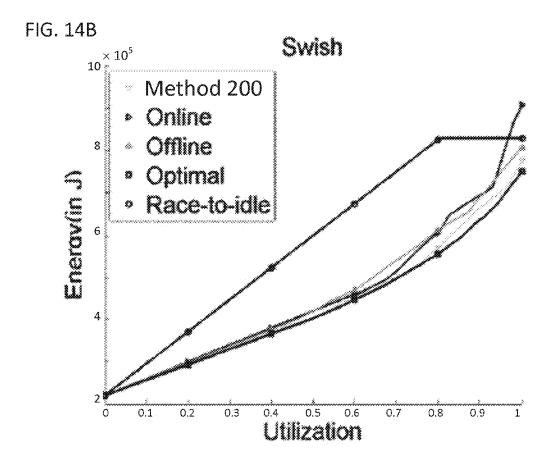

[0040] FIG. 14C shows a plot of the energy consumed as a function of utilization for the device executing the swish application for various optimization techniques;

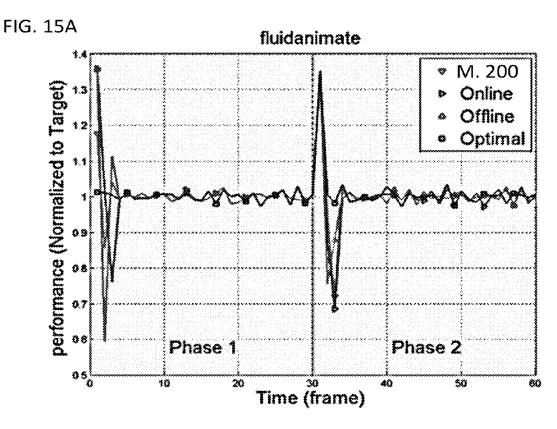

[0041] FIG. 15A shows a plot of performance of the device as a function of time for a transition from phase 1 to phase 2 of the application fluidanimate;

[0042] FIG. 15B shows a plot of power consumption of the device as a function of time for a transition from phase 1 to phase 2 of the application fluidanimate;

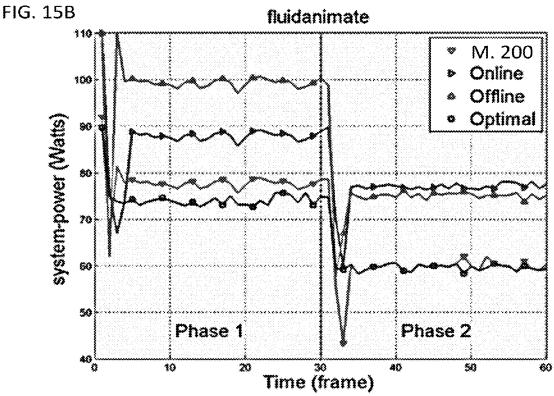

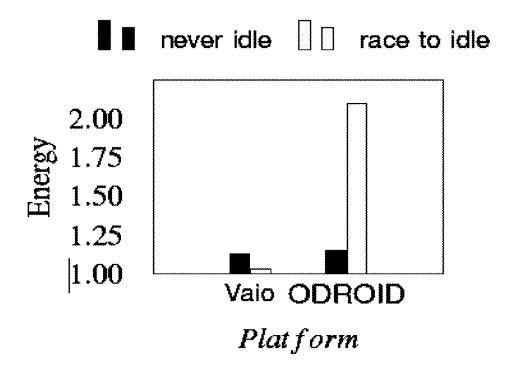

[0043] FIG. 16A shows a plot comparing energy and latency tradeoffs for the Vaio and the ODROID systems;

[0044] FIG. 16B shows a bar plot comparing energy consumption for the Vaio and the ODROID systems when the never-idle and race-to-idle heuristics are applied;

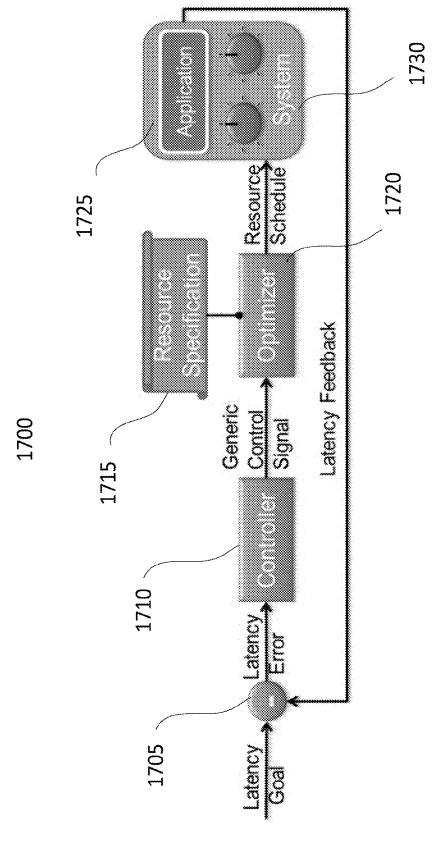

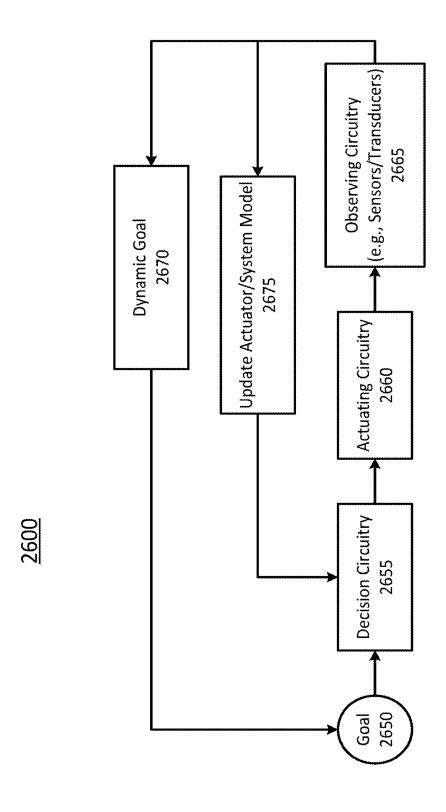

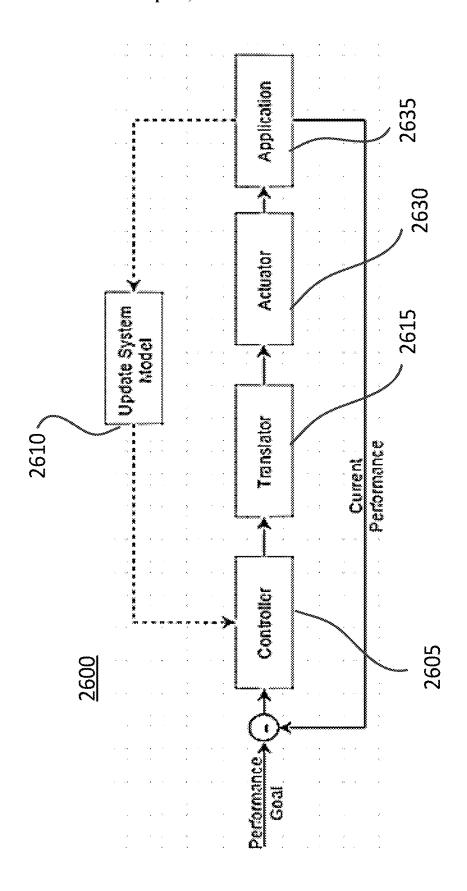

[0045] FIG. 17 shows a schematic diagram of a POET architecture, according to one implementation;

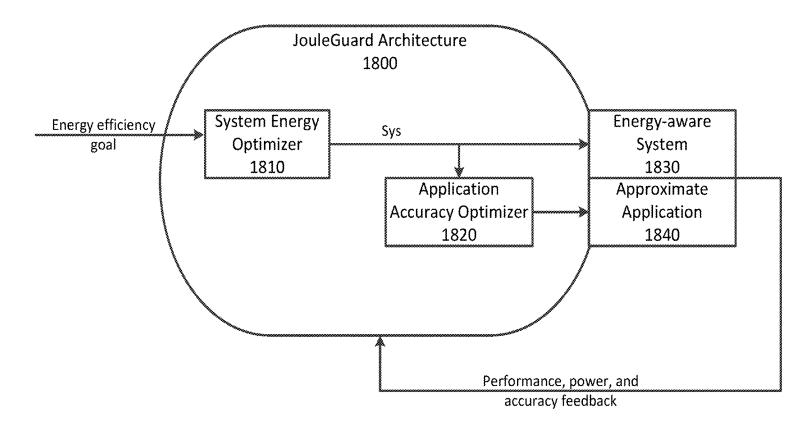

[0046] FIG. 18 shows a schematic diagram of a Joule-Guard architecture, according to one implementation;

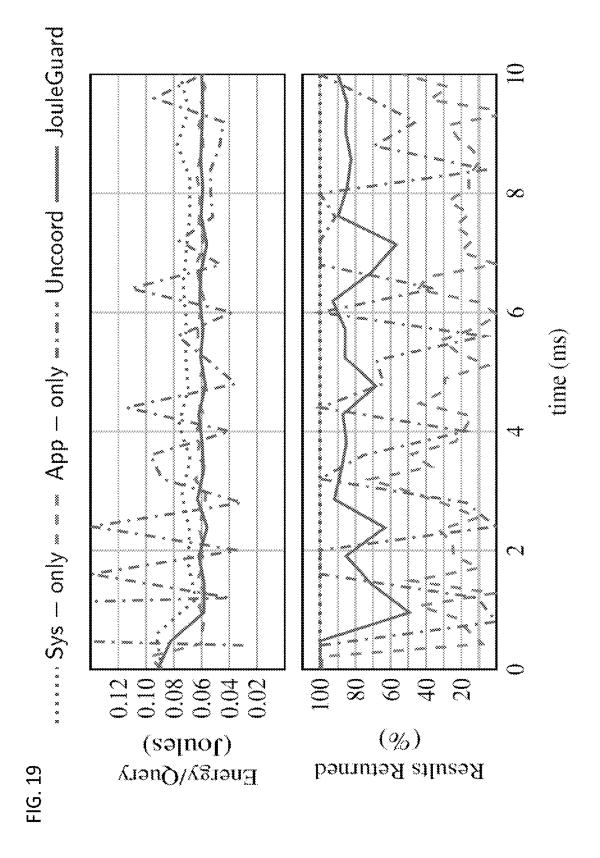

[0047] FIG. 19 shows a plot of simulation results for energy and percentage of returned results using various control methods compared to the JouleGuard architecture, according to one implementation;

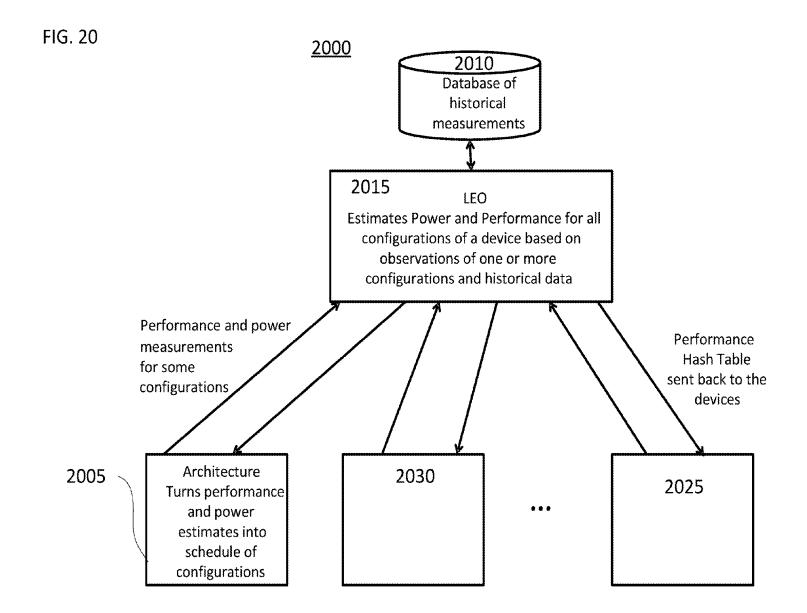

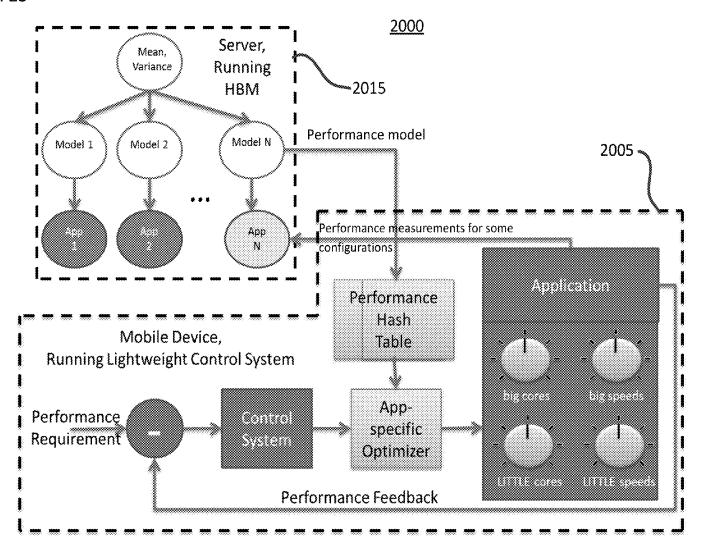

[0048] FIG. 20 shows a schematic diagram of a CALOREE system, according to one implementation;

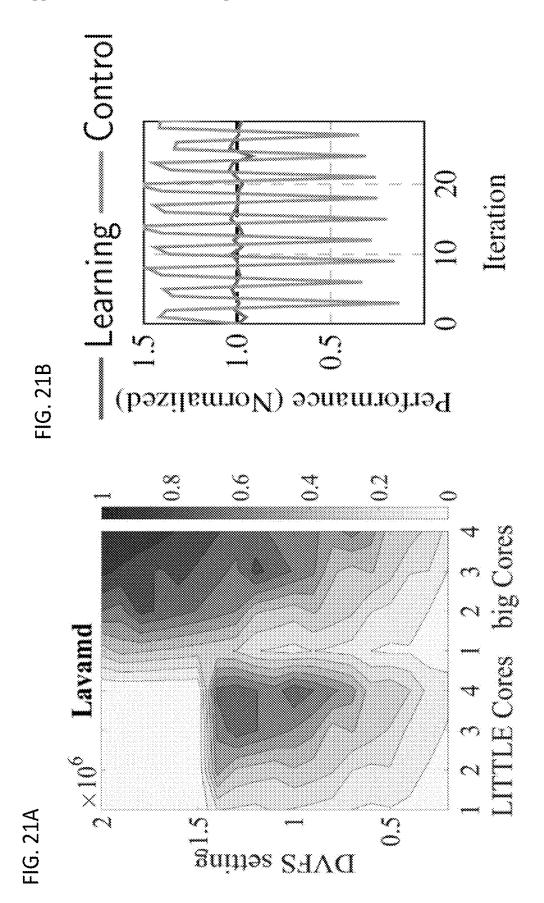

[0049] FIG. 21A shows plot of performance as a function of configuration for a device having an ARM big.LITTLE architecture that is executing a Lavamd application;

[0050] FIG. 21B shows plot of performance as a function of time for a device having an ARM big.LITTLE architecture that is executing the Lavamd application and that is selecting the configuration on the basis of a learning method or a control method;

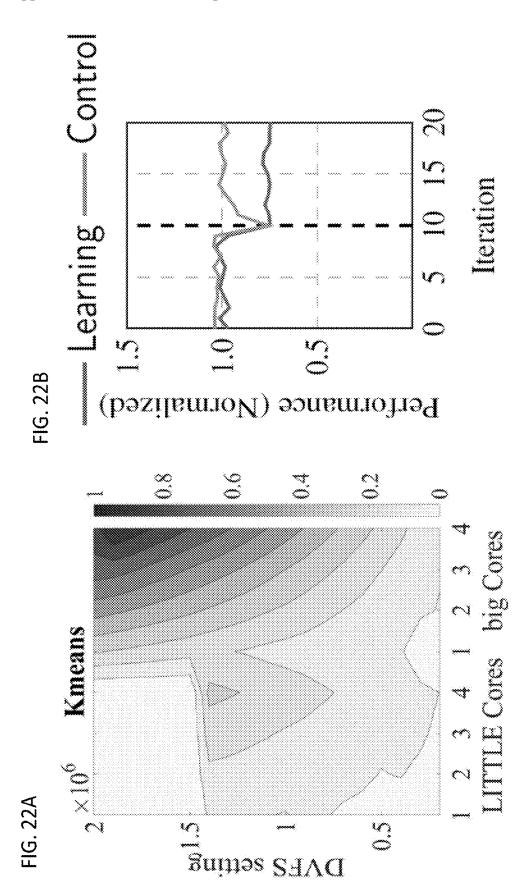

[0051] FIG. 22A shows plot of performance as a function of configuration for a device having an ARM big.LITTLE architecture that is executing a Kmeans application;

[0052] FIG. 22B shows plot of performance as a function of time for a device having an ARM big.LITTLE architecture that is executing a Kmeans application and that is selecting the configuration on the basis of a learning method or a control method;

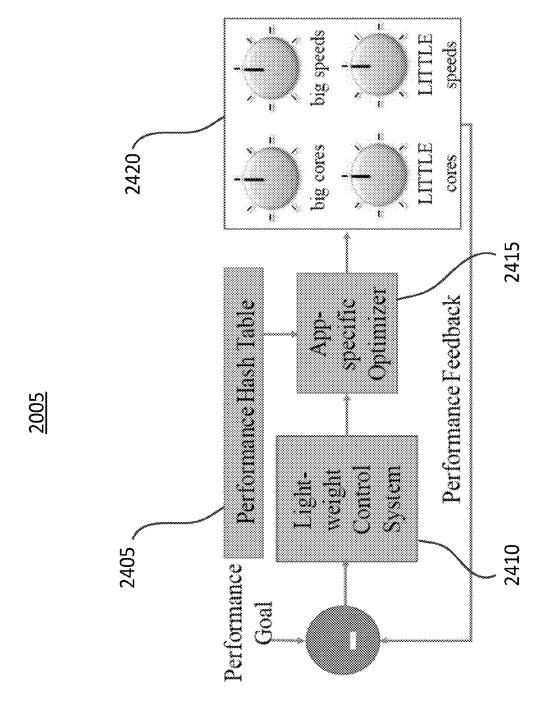

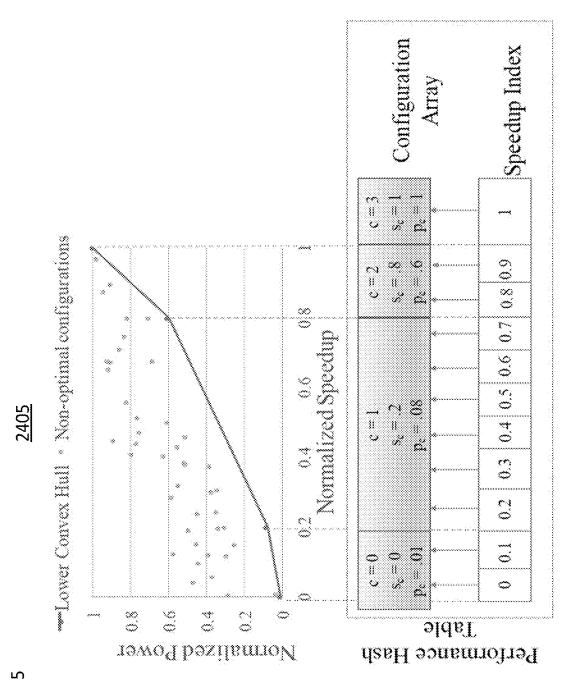

[0053] FIG. 23 shows a schematic diagram of a CALOREE system using an HBM to generate the performance model at the server and a lightweight control system in the device to implement configuration control using the performance model, according to one implementation;

[0054] FIG. 24 shows a schematic diagram of the device, according to one implementation;

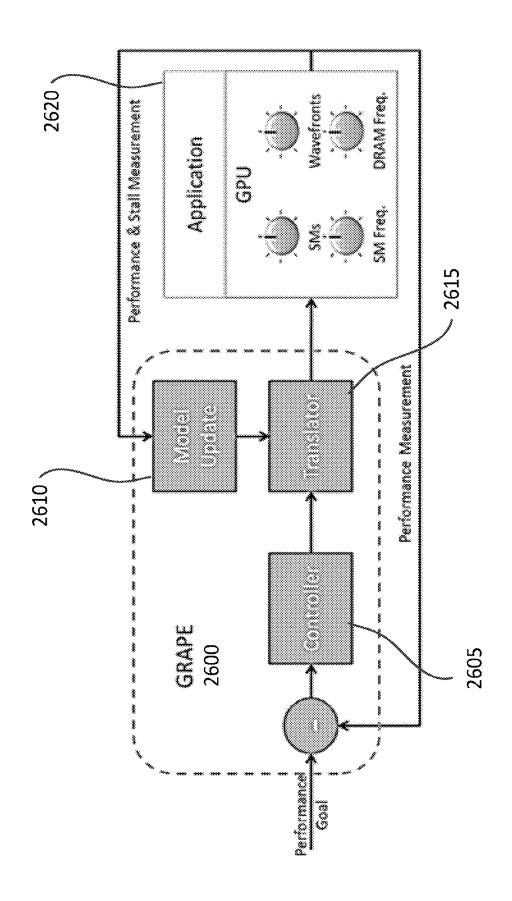

[0055] FIG. 25 shows a schematic diagram of the performance hash table (PHT), according to one implementation; [0056] FIG. 26 shows a schematic diagram of a GPU Resource Adaptation for Performance and Energy (GRAPE) architecture, according to a first implementation;

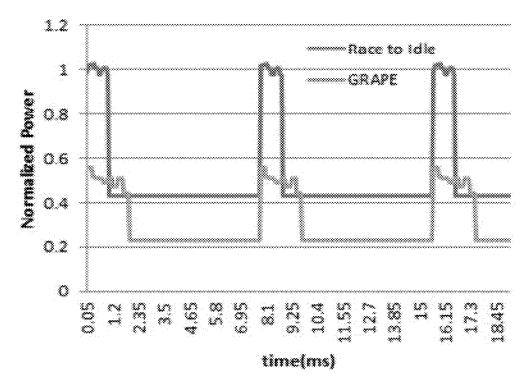

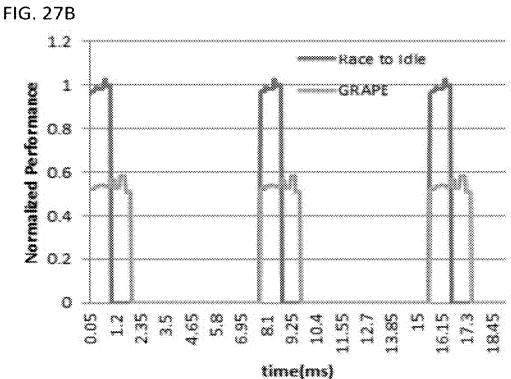

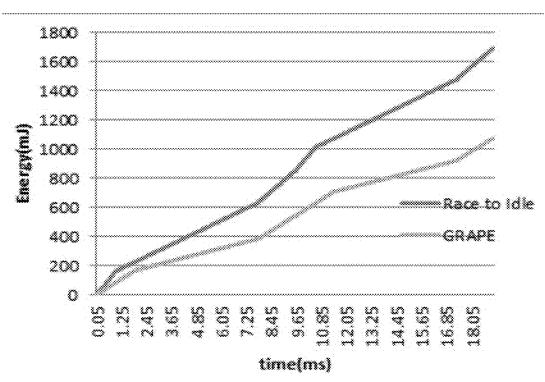

[0057] FIG. 27A shows a plot of normalized power as a function of time to compare a race-to-idle implementation with a GRAPE implementation;

[0058] FIG. 27B shows a plot of normalized performance as a function of time to compare the race-to-idle implementation with the GRAPE implementation;

[0059] FIG. 27C shows a plot of integrated energy consumed as a function of time to compare the race-to-idle implementation with the GRAPE implementation;

[0060] FIG. 28 shows a schematic diagram of a GPU Resource Adaptation for Performance and Energy (GRAPE) architecture, according to a second implementation;

[0061] FIG. 29 shows a schematic diagram of a GPU Resource Adaptation for Performance and Energy (GRAPE) architecture, according to a third implementation;

[0062] FIG. 30 shows a schematic diagram of a GRAPE datapath, according to one implementation;

[0063] FIG. 31 shows a timing diagram of an overhead count according to one implementation of a GRAPE architecture using VHDL;

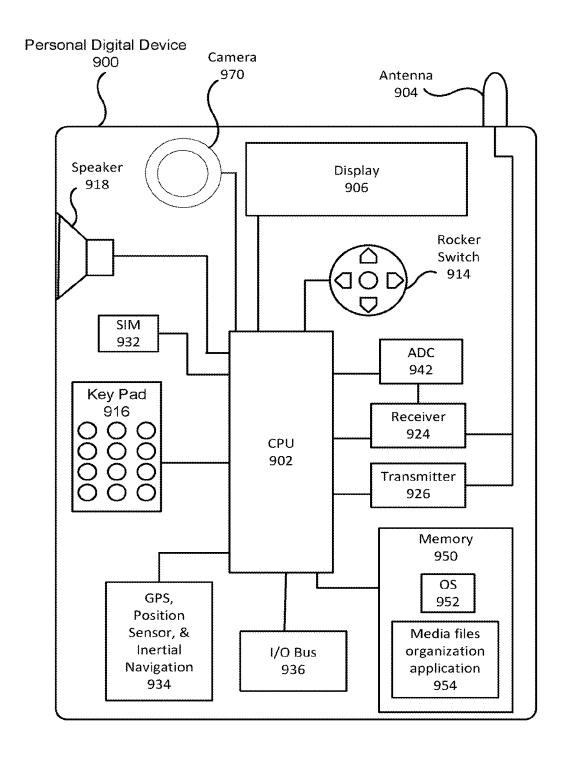

[0064] FIG. 32 shows a schematic diagram of a personal digital device, according to one implementation;

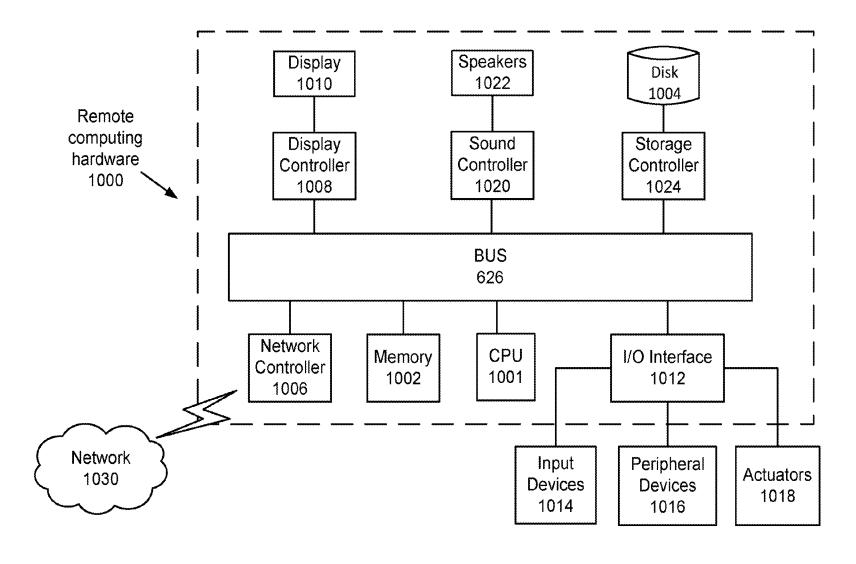

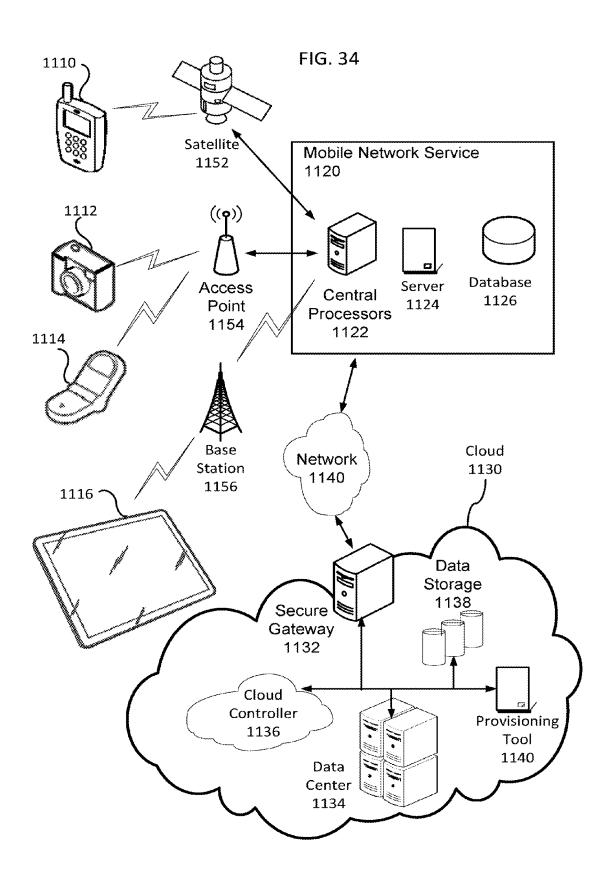

[0065] FIG. 33 shows a schematic diagram of remote computing hardware, according to one implementation; and [0066] FIG. 34 shows a schematic diagram of a networked cloud computing system, according to one implementation.

# SUMMARY OF THE INVENTION

[0067] In one aspect, the present disclosure provides:

[0068] (1) a server, including (i) a receiver configured to receive performance data of a device configured to execute an application in a plurality of computational configurations, the performance data including a first plurality of computational configurations with corresponding power-consumption rates and corresponding performance measures of the device when executing the application; (ii) a memory to store other performance data that includes a second plurality of computational configurations, power-consumption rates, and performance measures of a plurality of other devices when executing a plurality of applications; and (iii) processing circuitry configured to (a) compare the received performance data of the device to the stored other performance data, (b) determine a performance model of the device based on the comparison between the received performance data of the device and the stored other performance data, the performance model including an estimate of respective powerconsumption rates and respective performance measures of the device when executing the application for a third plurality of computational configurations of the device; and (c) a transmitter configured to transmit to the device the determined performance model of the device, wherein (d) the transmitted performance model of the device enables the device to optimize a combination of a performance measure and power consumption according to predefined optimization criteria.

[0069] (2) The server according to (1), wherein the processing circuitry is further configured to determine the performance model, wherein the performance measures of the received performance data are computational-performance rates, the performance measures of the stored other performance data are computational-performance rates, and the performance measures of the performance model are computational-performance rates.

[0070] (3) The server according to (1) or (2), wherein the processing circuitry is further configured to determine the performance model, wherein the performance model represents hash table of a power-consumption rates and performance measures of an energy-frontier plurality of computational configurations corresponding to a convex hull of a power-consumption/performance tradeoff space.

**[0071]** (4) The server according to any of (1)-(3), wherein the processing circuitry is further configured to compare the received performance data of the device to the stored other performance data, wherein the device is one of a mobile communication device, a wireless user equipment, a smart phone, wearable technology, and a tablet computer, an embedded processor.

[0072] (5) The server according to any of (1)-(4), wherein the processing circuitry is further configured to compare the

received performance data of the device to the stored other performance data, wherein the device is one of an aircraft motor, an embedded processor in heavy machinery, and a controller of a dynamic system.

[0073] (6) The server according to any of (1)-(5), wherein the processing circuitry is further configured to (i) compare the received performance data of the device to the stored other performance data to generate an estimate of the respective power-consumption rates and the respective performance measures corresponding to all computational configurations of the device, wherein (ii) the estimate of respective power-consumption rates and respective performance measures corresponding to all computational configurations of the device represents a mean and a measure of variance for each power-consumption rate and each performance measure of each computational configuration of all computational configurations of the device, and (iii) the performance model includes a subset of all computational configurations of the device corresponding to a convex hull of a tradeoff space between the power-consumption rates and the performance measures determined using the estimate of the respective power-consumption rates and the respective performance measures corresponding to all computational configurations of the device.

[0074] (7) The server according to any of (1)-(6), wherein the memory is further configured to store the received performance data of the device.

**[0075]** (8) The server according to any of (1)-(7), wherein the processing circuitry is further configured to compare the performance data of the device to the other performance data using a Bayesian network.

[0076] (9) The server according to any of (1)-(8), wherein the processing circuitry is further configured to (i) compare the received performance data of the device to the stored other performance data using an expectation maximization method to determine a combination of the plurality of other devices and the plurality of applications that is similar, in terms of performance and power use, to the device when executing the application, and (ii) determine the performance model of the device, using the expectation maximization method.

[0077] (10) The server according to any of (1)-(9), wherein the processing circuitry is further configured to (i) compare the received performance data of the device to the stored other performance data using an hierarchical Bayesian model to determine a combination of the plurality of other devices and the plurality of applications that is similar, in terms of performance and power use, to the device when executing the application, and (ii) determine the performance model of the device, using the hierarchical Bayesian model.

[0078] (11) The server according to any of (1)-(10), wherein the processing circuitry is further configured to compare the received performance data of the device to the stored other performance data using one of a support vector machine, a principal component analysis based method, a probabilistic graph method, an artificial neural network, a machine learning method, a pattern recognition method, a deep learning method, a clustering method, a genetic algorithm, and a classifier learning method to determine the performance model of the device.

[0079] (12) A device configured to execute an application in a plurality of computational configurations, the device including (i) an interface configured to (a) transmit, to a

server, performance data of the device, the performance data including, for a first plurality of computational configuration of the plurality of computational configurations, corresponding power-consumption rates and corresponding performance measures of the device when executing the application, (b) receive, from the server, a performance model that includes an estimate of respective power-consumption rates and respective performance measures of the device when executing the application for a second plurality of computational configurations of the device; and (ii) processing circuitry configured to (a) determine, using the performance model, a sequence of computational configurations of the device to perform predefined computational tasks of the application to optimize a combination of a performance measure and power consumption of the device according to predefined optimization criteria, and (b) execute the application according to the determined sequence.

**[0080]** (13) The device according to (12), wherein the processing circuitry is further configured to determine the sequence of computational configurations of the device to perform the predefined computational tasks of the application, wherein the predefined optimization criteria to be optimized to complete the predefined computational tasks within a predefined time period while minimizing power consumption of the device during the predefined time period.

[0081] (14) The device according to 12 or 13, wherein the processing circuitry is further configured to determine the sequence of computational configurations of the device to perform the predefined computational tasks of the application, wherein the predefined optimization criteria to be optimized is to maximize a ratio between the performance measure and the power consumption of the device, wherein the performance measure is a computational performance rate, and when an estimate of a completion time of the application indicates that the application will not be executed within a predefined time, using an approximate computing method to accelerate completion of the application in order to complete the application by a predefined time.

[0082] (15) The device according to any of (12)-(14), wherein the processing circuitry is further configured to determine the sequence of computational configurations of the device to perform the predefined computational tasks of the application, wherein the predefined optimization criteria to be optimized is to maximize a ratio between the performance measure and the power consumption of the device, wherein the performance measure is a computational-performance rate, and when a calculation indicates that a maximum of ratio of the computational-performance rate to the power-consumption rate is less than a predefined threshold, using an approximate computing method to increase the ratio of the computational-performance rate to the power-consumption rate.

[0083] (16) The device according to any of (12)-(15), wherein the processing circuitry is further configured to (i) determine the predefined time period to be inversely proportional to a speedup factor, and (ii) adjust the speedup factor to minimize a difference between a desired latency of the respective computational tasks and a measured latency of the respective computational tasks.

[0084] (17) The device according to any of (12)-(15), wherein the processing circuitry is further configured to (i) update the performance model of the device executing the

application according to repeated measurements of the power consumption rate and the computational performance rate using various computational configurations, (ii) update the selection of the computational configuration of the device according to the updated performance model, (iii) update the estimate of a completion time of the application according to the updated performance model and the updated computational configuration of the device, and (iv) update the approximate computing method according to an updated estimate of the completion time of the application, the updated computational configuration, and the updated the performance model.

[0085] (18) The device according to any of (12)-(17), wherein the processing circuitry is further configured to adjust the sequence of computational configurations of the device to perform predefined computational tasks of the application, using one of a control method including proportional, integral, and derivative feedback, a state-space control method, a multiple-input multiple-output control method, and a single-input single-output control method.

[0086] (19) A system, including (i) a device that includes (a) processing circuitry configured to: execute an application, change a computational configuration of the processing circuitry, measure power-consumption rates of the processing circuitry executing the application, and measure performance measures of the processing circuitry when executing the application, (b) a transmitter configured to transmit performance data of the device executing the application, the performance data including respective computational configurations of a first plurality of computational configurations of the device with the corresponding power-consumption rates and the corresponding performance measures of the device when executing the application, and (c) a receiver configured to receive a performance model that estimates respective power-consumption rates and the performance measures of the device executing the application, for a second plurality of computational configurations of the device, and (ii) a server that includes (a) a memory to store other performance data that includes computational configurations, power-consumption rates, and performance measures of a plurality of other devices when executing a plurality of applications, (b) a receiver configured to receive the transmitted performance data of the device, (c) a transmitter configured to transmit the performance model of the device, and (d) processing circuitry configured to: compare the received performance data of the device to the stored other performance data, and determine a performance model of the device based on the comparison between the received performance data of the device and the stored other performance data, the performance model including an estimate of the respective power-consumption rates and the respective performance measures of the device when executing the application for the second plurality of computational configurations of the device.

[0087] (20) The system according to claim 19, wherein the performance measures measured by the device includes a computational-performance rates that include a ratio of a number of computational tasks performed by the processing circuitry executing the application within a predefined time interval.

[0088] (21) A system, including: (i) an apparatus having at least one constrained property and a plurality of other properties to be optimized, the apparatus including (a) a plurality of components, which are configurable in real-time,

such that the apparatus can be configured in a plurality of configurations, and (b) circuitry configured to detect the at least one constrained property when the apparatus is configured in a first subset of the plurality of configurations; (ii) learning circuitry configured to (a) determine, using the detected at least one constrained property, a model representing the at least one constrained property when the apparatus is in the plurality of configurations, and (b) estimate an uncertainty of the determined at least one constrained property; and (iii) control circuitry configured to (a) select a configuration of the plurality of configurations to minimize an error value that is a difference between a desired value of the at least one constrained property and an observed value of the at least one constrained property by using the determined model and the estimated uncertainty. [0089] (22) The system according to (21), wherein the learning circuitry is further configured to encode the determined model as a hash table to provide rapid lookup of optimal configurations of the apparatus corresponding to respective values of the at least one constrained property, according to the determined model.

[0090] (23) The system according to (21) or (22), wherein the learning circuitry is further configured to determine the model using a hierarchical Bayesian method to compare the detected values of the at least one constrained property corresponding to the first subset of the plurality of configurations to a database of other apparatuses also having the at least one constrained property.

[0091] (24) The system according to any of (21)-(23), wherein the apparatus is a mobile computing device executing an application, the plurality of configurations include computational configurations of the mobile computing device, and the learning circuitry is included on a server, which is remotely accessed by the mobile computing device.

[0092] (25) An apparatus having at least one constrained property, the apparatus comprising: (i) a plurality of components, which are configurable in real-time to configure the apparatus in respective configurations of a plurality of configurations; (ii) detection circuitry configured to detect values of the at least one constrained property when the apparatus is configured in a first subset of the plurality of configurations; (iii) transmitting circuitry configured to transmit the detected values of the at least one constrained property and the corresponding first subset of the plurality of configurations to a model learning apparatus; (iv) receiving circuitry configured to (a) receive a model representing respective values of the at least one constrained property corresponding to the plurality of configurations, and (b) receive an uncertainty of the model; and (v) control circuitry configured to select, using the received model and the uncertainty of the model, a configuration of the plurality of configurations to minimize an error value that is a difference between a desired value of the at least one constrained property and an observed value of the at least one constrained property by using the determined model and the estimated uncertainty.

[0093] (26) A method of optimizing at least one constrained property of an apparatus having a plurality of components, which are configurable in real-time, the method comprising: (i) detecting values of the at least one constrained property and a plurality of other properties of the apparatus when the apparatus is configured in a first subset of the plurality of configurations; (ii) learning, using the detected values of the at least one constrained property, a

model representing the at least one constrained property and the plurality of other properties when the apparatus is in the plurality of configurations; (iii) estimating an uncertainty of the determined at least one constrained property value of the model; and (iv) selecting, using the determined model and the estimated uncertainty, a configuration of the plurality of configurations to minimize an error value that is a difference between a desired value of the at least one constrained property and an observed value of the at least one constrained property.

[0094] (27) A non-transitory computer readable storage medium including executable instruction, wherein the instructions, when executed by circuitry, cause the circuitry to perform the method according to (26).

## DETAILED DESCRIPTION

[0095] Optimizing a computational configuration of a computational device to achieve desired power-consumption and computational-performance goals can depend on having a reliable model of the performance and consumption of the device. Relying on a poor model could result in predicting a theoretically optimal configuration that is actually far from optimal. However, extensive empirical testing to measure the performance and consumption of the device configured in multiple computational configurations while executing the desired application also has drawbacks due to the significant resources in time and energy devoted to developing a comprehensive model for each combination of device and application. The model of performance and consumption can be different for each combination of device and application because different devices can have different performance and consumption characteristics and different applications can also have different performance and consumption characteristics. In many situations, measuring performance and consumption for all computational configurations is impracticable every time a device executes a new application or a new combination of applications. Accordingly, it is desirable to derive a reliable model of the performance and consumption for the device when executing an application while performing empirical testing using less than all of the computational configurations of the device when executing the application. Herein, the word performance is used as a short hand for "computational performance," and the word consumption is used as a short hand for "power consumption."

[0096] The methods described herein are more general than the primary example provided herein, which optimizes the computational configuration for computational performance subject to constraints on energy and/or power consumption. This primary example is non-limiting, and the methods described herein apply generally to constrained optimization problems in complex and dynamic environments.

[0097] As would be understood by a person of ordinary skill in the art, "constraints" refer to quantifiable goals that must be met for correct operation. Examples include, but are not limited to: performance, throughput, latency, energy, power, accuracy, security, reliability, resilience, cost, space, size, weight. Further, "optimization" subject to constraints refers to the fact that although some goals are non-negotiable, i.e. they absolutely must be respected, while other goals should be minimized or maximized. For example, computer servers must meet power constraints while maximizing throughput. As another example, self-driving cars

must meet speed constraints while minimizing energy (or fuel). The term "complexity" refers to the fact that in many systems there are multiple mechanisms that can be tuned to meet the constraints and the optimization goals. The interaction of these mechanisms can be difficult to model—often leading to non-linear, non-convex optimization spaces and/ or tradeoff spaces having multiple local minima—making it extremely difficult to ensure constraints are respected while other behavior is optimized. For example, the interaction between the number of active cores in a multicore and the speed of those cores creates non-linear, non-convex optimization problems. The term "dynamic" refers to the fact that unpredictable changes occur during system operation, yet the constraints must still be satisfied while other behavior is optimized. For example, when using a mobile device for a video call, the software must handle transitions from low motion (e.g. sitting still) to high motion (e.g. walking around a house or waving to the other party).

[0098] Many problems exhibit the combination of challenges presented by constrained optimization problems in complex and dynamic environments that are addressed by the methods described herein. The methods described herein use the general approach of combining machine learning (ML) and control theory (CT) to meet constraints optimally in complex and dynamic environments. In general, machine learning models the complex interactions of the available mechanisms, while control theory ensures the constraints are met despite dynamic changes. Machine learning enables the generation of a reasonably accurate model of the system without exhaustively exploring the parameter space. Having generating a model of the system, control theory can be applied to account for errors in the model and to adapt to dynamic changes of the system and/or changing goals. The methods described herein allow practical implementations in addition to formal analytical guarantees. ML and CT are broad fields that encompass a number of different individual techniques.

[0099] The exemplary implementations described herein use a non-limiting ML technique called hierarchical Bayesian models, but other ML techniques can also be used, as would be understood by a person of ordinary skill in the art. For example, the ML techniques that can be used in the methods described herein include: matrix completion methods, multi-tasking algorithms, transfer learning based algorithms, regression algorithms, Bandit-based learning methods, and genetic and evolutionary algorithms, for example. Matrix completion methods can include: low rank matrix completion with noise, high rank matrix completion, collaborative filtering, recommender systems (e.g., the Netflix<sup>TM</sup> algorithm), matrix completion with side information, Bayesian matrix completion, and nonparametric matrix completion, for example. Regression algorithms can include: random forest algorithms, polynomial regression, and gradient boosting, for example. Bandit-based learning can include: multiarmed bandit learners, and multiarmed bandit learners with correlated arms, for example.

[0100] The exemplary implementations described herein use the non-limiting CT example of a proportional-integral (PI) control. However, other classes of controllers can be used, as would be understood by a person of ordinary skill in the art. For example, the controller can use: proportional control, integral control, proportional integral control, proportional integral derivative control, state-space control, stochastic control, adaptive control, optimal control, model

predictive control, switching control, gain scheduling, selftuning regulators, minimum variance control, and fuzzy control.

[0101] The non-limiting exemplary implementations described herein focus primarily on combinations of hierarchical Bayesian learning with adaptive proportional integral control with an independent optimization module. However, these non-limiting exemplary implementations are instantiations of the more general concept contemplated herein, which is sufficiently general to apply to many more combinations of the above approaches. For example, the methods described herein can be applied to: maximizing throughput for compute servers while respecting constraints on power consumption; ensuring that a mobile device can last for the duration of a plane trip; balancing tradeoffs between quality, energy, and security for mobile video calls; minimizing cost while providing reliable performance for cloud customers; minimizing energy while ensuring user satisfaction for mobile applications; managing tradeoffs between sensor usage and reliability in self-driving cars; maximizing throughput for minimal cost in industrial assembly lines; and automatic configuration of high-end televisions to minimize energy consumption while meeting user quality requirements.

[0102] More particularly, the methods described herein can be applied to many devices and systems in addition to the exemplary networked mobile communication devices (e.g., smartphones and tablet PCs) described herein. For example, the methods can be used to optimize any system which has one or more constraints, and the may be particularly beneficial when it is used to optimize a system comprising dynamics or time-dependent variables that are unpredictable or difficult to model. Moreover, the methods described herein may be particularly beneficial for optimizing systems that are too complicated for linear regressions or other analytical models to capture the dependence on the system's parameters. Exemplary systems include jet airplane turbines for which it may be desirable to minimize fuel consumption while maintaining power output by varying some or all of the turbine's control parameters in the face of unpredictably varying inputs such as humidity, pressure, and other environmental conditions, for example. Other exemplary systems include building HVAC systems for which it may be desirable to minimize power consumption, while maintaining temperature and humidity conditions throughout many different regions of the building or buildings by varying air handling controls, such as air flow rates, temperatures, cooling/heating power, and other parameters while occupants of the building are opening or closing windows and/or entering and entering rooms in unpredictable ways, for example. Additionally, network bandwidth optimization can be another exemplary system applying the methods described herein. For example, in network bandwidth optimization, data throughput from multiple sources to multiple destinations across a network can be maximized while latency is constrained and in which data packets can take any one of multiple routes across the network and the arrival of the new data packets into the network is unpredictable. A further exemplary system in which the methods described herein can be applied is internal combustion engines for which fuel consumption is minimized while, for example, power output is held constant and the valve timing and other engine parameters are varied as engine inputs such as air and fuel quality vary. Additional constrained optimization problems to which the present invention may be applied arise in power generation systems, warehouse distribution systems, and manufacturing facilities, for example. [0103] Now an exemplary implementation of a smart home is provided, illustrating the methods described herein. The methods described herein combining machine learning together with feedback and control can be used to manage a "smart home." For example, a home could be configured with shades that automatically adjust and light fixtures that adjust brightness. A homeowner might have a constraint on brightness and would like to meet this constraint while minimizing electricity cost.

[0104] This example has all the requisite properties described above. That is, (1) there is a quantifiable constraint in terms of light, (2) there is an objective function to be optimized (i.e., electricity cost), and (3) there are multiple configurable parameters (i.e., shades and lights). The combination of shades and lights give us a complex tradeoff space. Raising and lowering the shades have one-time costs. The lights continuously consume electricity. In addition, there are system dynamics as changes in weather and time of day create different conditions.

[0105] Such a smart home could learn from other smart homes to build models of the relationship between shades, electric lights, and brightness. That learned model could then be passed to a controller that operates within the home to adjust the relative usage of shades and electric lights to ensure the homeowner is always in a sufficiently bright room while the use of electric lights is minimized. This example maps directly into the example of meeting a performance constraint used throughout the document. Here the configurable parameters are the shades and lights (analogous to cores and clockspeeds in a computer). The constraint is brightness (analogous to computer performance). The objective to be optimized is cost (analogous to energy). The learner would measure the brightness and cost of different configurations, perhaps combine those measurements with other measurements from other smart homes, and produce a model that maps configuration to brightness and cost. This same model could be stored in a brightness hash table (analogous to the performance hash table). The controller computes the error between the current brightness and the desired brightness, computes a brightup (analogous to speedup) and then uses the brightness hash table to select a minimal cost configuration that delivers the desired brigh-

[0106] Altering the example slightly, the homeowner may be more concerned about electricity costs. In this case, the constraint is the amount of money the home owner is willing to spend on lighting. The objective is to achieve the brightest conditions. The learner would produce almost the same model as the previous paragraph, but now it would store it in a cost hash table-because it is controlling costs. In this example the controller measures the rate of spending on lighting and computes an error between the desired spending rate and the budget (monthly budgets are trivially converted to rates by dividing by time) to compute a costup (analogous, again, to speedup). The controller then looks in the cost hash table to find the brightest configuration that meets the desired budget, adjusting to maintain the correct power consumption despite weather and time changes. Such a system could even adapt to changing prices in electricity.

[0107] As would be understood by a person of ordinary skill in the art, the applicable mathematical formulation is

almost identical to the example provided hereafter of meeting a computer program's latency constraint with minimal energy. Similar to the computational latency example to be discussed, the learner maps configurations into quantifiable behavior. Tradeoffs are stored in a hash table using a similar scheme to FIG. 25. The controller similarly measures a difference between a constraint and the actual behavior and then selects the configuration that optimizes the constraint.

[0108] Returning to the example of optimizing computational performance under energy and/or power constraints, there is a tension between gathering sufficient empirical data to estimate a reliable model whereby an optimal computational configuration can be approximated and limiting the resources devoted to gathering empirical data. Machine learning techniques represent a promising approach to addressing this estimation problem. Offline learning approaches collect profiling data for known applications and use that to predict optimal behavior for unseen applications. Online learning approaches use information collected while an application is running to quickly estimate the optimal configuration. Offline methods require minimal runtime overhead, but suffer because they estimate only trends and cannot adapt to particulars of the current application being executed on the device. Online methods customize to the current application, but cannot leverage experience from other applications. In a sense, offline methods are dependent on a rich training set that represents all possible behavior, while the online methods can be data limited and generate a statistically weak and less accurate model due to the small sample size.

[0109] In contrast to the offline and online methods, a hybrid method of estimating the performance-consumption model is described herein. The hybrid method is a machine learning method that combines the best of the offline and online methods (e.g., the hybrid method combines the statistical properties of both offline and online estimation). The hybrid method begins with a set of applications for which the consumption and performance have been measured previously (e.g., offline).

[0110] The hybrid method can use a graphical model to integrate a small number of measurements of the current application with knowledge of the previously observed applications to produce accurate estimations of the consumption and performance tradeoffs for the current application in all configurations. The hybrid method's strength is that it quickly matches the behavior of the current application to a subset of the previously observed applications. For example, if the hybrid method has previously seen an application that only scales to eight cores, it can use that information to quickly determine if the current application will be limited in its scaling.

[0111] The hybrid method can be performed on a computing device including a computer readable memory, such as a hard disk, that stores a database of consumption and performance data for the device when executing various applications. This standalone implementation of the hybrid method is then performed by the device comparing a small data set of consumption and performance measurements with the database of previously recorded measurements for other applications to estimate a model of the device when executing the current application. Using the estimated model, the device then determines the optimal computational configuration for executing the current application.

[0112] Alternatively, the hybrid method can be performed by a combination of a device and a server communicating with the device. The device can generate data for a small number of configurations for the device when executing the application, and send this small data set to the server. The server can compare the received small data set for the device with a database of the consumption and performance data stored on the server, and estimate the model of the device when executing the application. After receiving the estimated model from the server, the device can then apply the model to determining the optimal computational configuration for executing the application on the device. Thus, the hybrid method can be separated into subtasks that can be performed on either the device or on the server in communication with the device. One advantage of using a server to perform some of the subtasks is that the server might not be subject to the same size, memory and power constraints of the device. For example, the device can be a smartphone or wearable technology that has a small size with a limited battery and memory, whereas the server could be a large data center with access to significantly more power and memory. Further, the database of the server could include performance and consumption data collected from many different devices when executing many different applications. Accordingly, the comparison between the small data set and the database can be statistically richer due to the large sample size of data provided by the larger database contributed to by a large number of computational devices. Thus, each device accessing the server to obtain a model also can contribute to grow the database to the benefit of future users.

[0113] Referring now to the drawings, wherein like reference numerals designate identical or corresponding parts throughout the several views, FIG. 1 shows a schematic drawing of a device-server system. A computing device 120 executes a current application and sends performance data of the consumption and performance for a small set of computational configurations of the computing device 120 when executing the current application. The performance data is received by a server 110. The server 110 compares the small data set receiving from the computing device 120 with a database of performance data corresponding to various combinations of devices and other applications. Using these comparisons between the small data set and the database the server estimates a performance model, and sends the performance model to the computing device 120. The computing device 120 then applies the estimated performance model to optimizing the computational configuration of the computing device 120 for executing the current application. The computing device can update the performance data sent to the server 110 by measurements of the continued execution of the current application, and the server can update the performance model based on the updated performance data.

[0114] FIG. 2A shows a flow diagram of a method 200. In process 210 of method 200, the computational performance and power consumption of the computing device 120 are obtained for a discrete set of computational configurations of the computing device 120 when executing the current application

[0115] In process 220 of method 200, the small data set representing performance and consumption measurements is used to estimate a performance model representing the computational performance and power consumption for all computational configurations of the computing device 120 when executing the current application. In certain imple-

mentations, the estimation is performed by the server 110. In certain other implementations, the estimation is performed by the computing device 120.

[0116] In process 230 of method 200, an optimal computational configuration is selected using the estimated performance model from process 120. The optimal computational configuration can be a single computational configuration of a sequence of computational configurations that optimally executes the current application on the device, according to predefined criteria. For example, the predefined criteria can be to minimize the total energy consumption subject to the constraint that the application be completed within a predefined time window. Alternatively, the predefined criteria can be to maximize computational accuracy subject to the constraint that no more than a predefined amount of energy be consumed within the predefined time window. The computational configuration of the computing device 120 can also be optimized according to other predefined criteria.

[0117] In step 240 of method 200, the performance model of the computing device 120 and the small data set used for the estimation of the performance model can be updated to improve the performance model and more accurately estimate the optimal configuration of the computing device 120. Further, if the computing device consumes power at a rate greater or less than the rate indicated by the performance model than the configuration can be updated to reflect these changes and to ensure compliance with the predefined optimization criteria. For example, if the predefined criteria includes a guarantee that no more than a predefined amount of energy be consumed within the predefined time window and a higher than expected amount of energy was consumed in the first part of the window than the energy consumption can be decreased throughout the remaining duration of the time window to ensure the predefined criteria are satisfied. [0118] FIG. 2B shows a flow diagram of process 210. Step

212 of process 210 includes initializing a loop n and initializing a discrete subset of computation configurations selected from the set of all computational configurations of the device. This discrete subset of computation configurations corresponds to the small data set to be used for the comparison to the performance database and the estimation of the performance model in process 220.

[0119] In step 214 of process 210, the computational performance and power consumption of the computing device 120 when executing the current application is measured for the n<sup>th</sup> computational configuration of the subset initialized in step 212.

[0120] In step 216 of process 210, the measured computational performance and power consumption from step 214 is recorded in a table. Also the n<sup>th</sup> computational configuration of the subset is also recorded in the table. FIG. 3 shows an example of a table of eight configurations ranging from a clock rate of 250,000 to 400,000 and ranging from zero additional cores to 2 additional cores. The number of configurations, clockspeeds, and cores provided herein are non-limiting examples. The methods described herein can be used with any clockspeed and any number of cores. They also support other configurable parameters such as network bandwidth, memory bandwidth, cache partitions, etc. The computational performance can be recorded as a normalized speedup factor relative to a baseline configuration, and the power consumption can be recorded as a powerup factor indicating the relative increase in power consumed relative to the baseline configuration.

[0121] In step 218 of process 210, the loop index n is incremented and process 210 inquires whether all of the initialized discrete subset of computational configurations have been evaluated. If all of the computational configurations have been evaluated, then process 210 is complete. Otherwise process 210 proceeds from step 218 to step 212. [0122] FIG. 2C shows a flow diagram of process 220. In step 222 of process 220, a database of performance data is retrieved. The database can include performance data of the computing device 120 in addition to other computing devices contributing to the database. The database includes recorded measurements of the computational performance and power consumption of these devices for various computational configurations and executing various applications. The database is similar to the small data set corresponding to the discrete subset of computation configurations of process 210, except the database has more data and corresponds to several applications. Some of the data from the database will likely represent a similar powerperformance tradeoff as the power-performance tradeoff represented by the small data set from computing device 120 executing the current application. However, the data from the database will also include data points for computational configurations not included in the small data set, and these additional data points in the database can be used to estimate the performance and consumption values for the computing device 120 executing the current application that have been omitted in the original small data set.

[0123] Accordingly, a complete model of the computing device 120 executing the current application can be estimated by comparing the small data set to the more complete data of the database and identifying those combinations of devices and applications having power-performance tradeoffs most similar to the power-performance tradeoffs of the computing device 120 executing the current application. The data of these similar combinations of devices and applications from the database can then be used to fill in the holes left in the small data set to generate a comprehensive model of the computing device 120 executing the current application.

[0124] In step 224 of process 220, the performance-data table obtained in process 210 is compared with the database retrieved in step 222 to find those combinations of devices and applications having similar computational performance and power consumption as a function of computational configuration.

[0125] In step 226 of process 220, a performance model of the device when executing the application is estimated. The performance model includes the computational performance and power consumption for all computational configurations of the device when executing the application based on the performance-data table and similar performance data from the database.

[0126] FIG. 2D shows a flow diagram of process 230. The process 230 in FIG. 2D seeks to optimize the computational configuration according to the predefined criteria of minimizing the total energy consumption under the constraint that the application is completed within a predefined time window. In step 232 of process 230, a target job latency is determined for computational tasks of the current application. The target job latency is the desired amount of time in which each of the computational tasks is to be completed. The target job latency can be obtained from a ratio between the computational tasks required to complete the application

and the predefined time window. Further, the optimal solution to satisfy the predefined criteria can be a sequence of computational configurations. For example, the optimal configuration might be to allocate all computational resource to the application, completing the application as quickly as possible and then to idle throughout the remainder of the predefined time window. If a sequence of computational configurations are used, then the target job latency can vary between the various portions of the sequence.

[0127] In step 234 of process 230, the actual job latency is measured as the computing device 120 executes the application. When the actual job latency deviates from the target job latency, a speedup factor is adjusted according to differences between the measured latency and the target job latency.

[0128] In step 236 of process 230, the estimated performance model is used to determine the optimal computational configuration to achieve the speedup factor. Also, the estimated performance model is used to determine a sequence of computational configurations to achieve the speedup factor.

[0129] In step 238 of process 230, the process 230 continues to step 234 if the current application is still continuing. If the optimal configuration is a sequence of configurations, then process 230 will also include the step of updating the target job latency after the completion of each section of the sequence. If the application is complete then process 230 is also complete.

[0130] As the application is executing, the measured performance and consumption of the computing device 120 can be recorded and used to update the performance model of the computing device 120. The newly measured performance and consumption data of the computing device 120 can be added to the small data set to generate an augmented small data set. This augmented small data set can then be used in a process similar to process 220 to generate an updated model of the computing device 120 when executing the current application. This process of updating the model of the computing device 120 can be performed in parallel with process 230, and the updated model of the computing device 120 can be incorporated into process 230 after the updated model has been generated. This updating of the model of the computing device 120 is indicated as step 240 of method 200, and FIG. 2A shows step 240 as being performed after process 230. However, step 240 can also be performed simultaneously with process 230. Additionally, step 240 can be performed at periodic time intervals after starting process 230. In certain implementations, step 240 can be omitted.

[0131] FIG. 2E shows a flow diagram of process 230', which is an alternative to process 230. In contrast to process 230, process 230' solves the constrained optimization problem of maximizing computational accuracy and maximizing efficiency while providing guarantees that predefined computational tasks are completed within a predefined time period.

[0132] In step 232' of process 230', the performance model is used to determine an optimal-efficiency configuration corresponding to a maximum ratio between computational performance and power consumption of the device when executing the application, and set the device in the optimal-efficiency configuration.

[0133] In step 234' of process 230', a speedup factor is determined in order to operate in the optimal-efficiency

configuration and also complete predefined computational tasks within a desired time period.

[0134] In step 236' of process 230', the completion of the computational tasks are accelerated by the speedup factor by using approximate computing to trade-off accuracy for increased speed.

[0135] In step 237' of process 230', the performance model of the computing device 120 is updated according to continued measurements of the computational performance and power consumption of the computing device 120 when executing the application. This updating of the performance model of the computing device 120 can either be performed according to step 240 or step 237' can be performed using another method described later herein.

[0136] Now a description of one implementation is provided as an illustrative example. This implementation uses probabilistic graphical models (PGMs) to perform the functions of comparing the small data set to the database and to estimate a performance model of the computing device 120. This illustrative example further presents an example of optimizing the computational configuration according to the predefined optimization criteria of minimizing the energy consumption of the current application subject to an additional performance constraint (e.g., the additional performance constraint can be that the work of the application be accomplished by a predefined deadline).

**[0137]** In this example, the following notation is used. The set of real numbers is denoted by  $\mathbb{R} \cdot \mathbb{R}^d$  denotes the set of d-dimensional vectors of real numbers;  $\mathbb{R}^{d \times n}$  denotes the set of real d×n dimensional matrices. The vectors are denoted by lower-case and matrices with upper-case boldfaced letters. The transpose of a vector  $\mathbf{x}$  (or matrix) is denoted by  $\mathbf{x}^T$  or just  $\mathbf{x}'$ .  $\|\mathbf{x}\|_2$  is the  $\mathcal{L}_2$  norm of vector  $\mathbf{x}$ , i.e.

i.e.

$$||x||_2 = \sqrt{\sum_{i=1}^d x^2[i]}$$

.

$||X||_F$  is the Frobenius norm of matrix X,

i.e.

$$||X||_F = \sqrt{\sum_{i=1}^d \sum_{i=1}^n X^2[i][j]}$$

.

Let  $A \in \mathbb{R}^{d \times d}$  denote a d-dimensional square matrix. tr(A) is the trace of the matrix A and is given as,

$$tr(A) = \sum_{i=1}^{d} A[i][j].$$

Further, diag (x) is a d-dimensional diagonal matrix B with the diagonal elements given as, B[i][i]=x[i] and off-diagonal elements being 0.

**[0138]** Now, a review the standard statistical notation used herein is provided below. Let x, y denote any random variables in  $\mathbb{R}^d$ . The notation  $x \sim \mathcal{D}$  represents that x is drawn from the distribution  $\mathcal{D}$ . Similarly, the notation x,  $y \sim \mathcal{D}$  represents that x and y are jointly drawn from the distribution  $\mathcal{D}$ , and finally  $x|y \sim \mathcal{D}$  represents that x is drawn from the distribution after observing (or conditioned

on) the random variable y. The following are the operators on x: E[x] expected value of x, var[x]: variance of x, var[x]: covariance of x and y.  $\hat{x}$  denotes the estimated value for the random variable x.

[0139] The energy optimization problem can be formalized by the predefined optimization criteria of minimizing the energy consumed while executing the current application according to predefined constraints. In the example considered here, these predefined constraints include completing the application by a predefined deadline. The computing device 120 can be configurable in various computational configurations, each configuration having application-specific computational performance characteristics and power consumption characteristics. The goal of the optimization is to select the configuration that finishes the work (e.g., completes execution of the application) by the deadline while minimizing the energy consumption.

**[0140]** Formally, this goal can be expressed generally as the computing device **120** accomplishing W work units in time T. The computing device **120** has a set of configurations (e.g., combinations of cores and clock speeds) denoted by  $\mathcal C$ . When each configuration c in the set of configurations  $\mathcal C$  has an application-specific performance (or work rate)  $\mathbf r_c$  and power consumption  $\mathbf p_c$ , then the energy minimization problem can be formulated as a linear program, which is given by

$$\min_{t \ge 0} \sum_{c \in C} p_c t_c,$$

subject to  $\sum_{c \in C} r_c t_c = W$ , and

$$\sum_{c \in C} t_c \le T,$$

wherein  $p_c$  is the power consumed when executing the application using the  $c^{th}$  configuration;  $r_c$  is the performance rate when running on  $c^{th}$  configuration; W is the work to be performed by the application;  $t_c$  is the time spent executing the application while configured in the  $c^{th}$  configuration; and T is the total run time when executing the application. The linear program above finds the times  $t_c$  during which the application is executed using the  $c^{th}$  configuration so as to minimize the total energy consumption and ensure all work is completed by the deadline. The values  $p_c$  and  $r_c$  are central to solving this problem, and the values  $p_c$  and  $r_c$  are obtained from the performance model of the device. When  $p_c$  and  $r_c$  are known, the structure of this linear program enables the minimal energy schedule to be found using convex optimization techniques, for example.

[0141] This formulation is abstract so that it can be applied to many applications and systems. In one embodiment, this abstract formulation can be performed using a Kmeans application using a 16-core Linux x86 server with hyperthreading (allowing up to 32 cores to be allocated) as the computing device 120. The numbers of core counts provided herein are non-limiting examples. The methods described herein can be used with any core counts. Further, other learning techniques can be advantageous choices at different core counts, but the same techniques are applicable. Moreover, the configurable parameter need not be cores, but any allocatable resource.

**[0142]** The Kmeans application is a clustering algorithm used to analyze large data sets. The Kmeans application can be run with different performance demands and can be optimized in order to minimize energy for any given performance demand. To do so for Kmeans on the 32-core system, the performance and consumption is estimated as a function of the number of cores allocated to the application. Given this information, the most energy efficient number of cores can be selected according to the given performance demand.