## THE UNIVERSITY OF CHICAGO

## ARCHITECTURAL DESIGN FOR EMERGING QUANTUM TECHNOLOGIES

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF COMPUTER SCIENCE

BY JONATHAN M. BAKER

CHICAGO, ILLINOIS

DECEMBER 2022

Copyright  $\bigcirc$  2022 by Jonathan M. Baker All Rights Reserved

# TABLE OF CONTENTS

| LI | ST O | F FIGURES                                             | vi         |

|----|------|-------------------------------------------------------|------------|

| LI | ST O | F TABLES                                              | ĺΧ         |

| A  | CKNO | OWLEDGMENTS                                           | хi         |

| A] | BSTR | ACTxxx                                                | ii         |

| 1  | INT  | RODUCTION                                             | 1          |

| 2  | DET  | TERMINING THE RIGHT ABSTRACTIONS: MULTIVALUED QUANTUM |            |

|    | LOC  | GIC                                                   | 7          |

|    | 2.1  | Relevant Background                                   | 9          |

|    | 2.2  |                                                       | .3         |

|    |      | 2.2.1 Qudits                                          | 3          |

|    |      | 2.2.2 Generalized Toffoli Gate                        | .3         |

|    | 2.3  | Circuit Constructions                                 | .5         |

|    |      | 2.3.1 Key Intuition                                   | .5         |

|    |      |                                                       | 6          |

|    |      |                                                       | 7          |

|    |      |                                                       | 8          |

|    |      |                                                       | 21         |

|    | 2.4  | , , ,                                                 | 26         |

|    |      | 11                                                    | 26         |

|    |      | ·                                                     | 27         |

|    |      | 8                                                     | 27         |

|    |      | 8                                                     | 27         |

|    | 2.5  |                                                       | 28         |

|    | 2.0  |                                                       | 28         |

|    |      |                                                       | <b>3</b> 0 |

|    | 2.6  | v                                                     | 32         |

|    | 2.0  |                                                       | 32         |

|    |      |                                                       | 33         |

|    |      | 1 7 1                                                 | 34         |

|    | 2.7  |                                                       | 5<br>5     |

|    | 2.8  |                                                       | 66<br>16   |

|    | 2.0  |                                                       | 6<br>6     |

|    |      |                                                       | 50<br>37   |

|    |      |                                                       | 10<br>10   |

|    | 2.0  | 1                                                     |            |

|    | 2.9  | Discussion                                            | 15         |

| 3 |       | CHITECTURAL TRADE-OFFS IN EMERGING TECHNOLOGY: NEUTRAL    |

|---|-------|-----------------------------------------------------------|

|   | AT(   | OM ARCHITECTURES                                          |

|   | 3.1   | Introduction                                              |

|   | 3.2   | Relevant Background                                       |

|   |       | 3.2.1 Quantum Computation and the Gate Model              |

|   |       | 3.2.2 The Quantum Compilation Problem                     |

|   |       | 3.2.3 Neutral Atoms                                       |

|   | 3.3   | Neutral Atom Compiler and Methodology                     |

|   |       | 3.3.1 Mapping, Routing, and Scheduling                    |

|   |       | 3.3.2 Benchmarks                                          |

|   |       | 3.3.3 Experimental Setup                                  |

|   | 3.4   | Unique Advantages of Neutral Atom Architectures           |

|   |       | 3.4.1 Long Range Interactions                             |

|   |       | 3.4.2 Native Multiquibit Gates                            |

|   | 3.5   | Error Analysis of Neutral Atom Architectures              |

|   | 3.6   | Unique Challenge: Sporadic Atom Loss                      |

|   | 3.7   | Remarks                                                   |

| , | 4 D.I |                                                           |

| 4 |       | PLICATION-GUIDED ARCHITECTURAL DESIGN. VIRTUALIZING ERROR |

|   |       | RRECTED QUBITS                                            |

|   | 4.1   | Introduction                                              |

|   | 4.2   | Relevant Background                                       |

|   |       | 4.2.1 Superconducting Qubit Architectures                 |

|   |       | 4.2.2 Qubit Memory Technology                             |

|   |       | 4.2.3 Quantum Errors                                      |

|   |       | 4.2.4 Surface Codes, Error Decoding, and                  |

|   | 4.0   | Lattice Surgery                                           |

|   | 4.3   | Virtualized Logical Qubits                                |

|   |       | 4.3.1 Natural Surface Code Embedding                      |

|   |       | 4.3.2 Transversal CNOT                                    |

|   |       | 1                                                         |

|   | 1 1   | 4.3.4 Architectural Considerations                        |

|   | 4.4   | Evaluation                                                |

|   |       | 4.4.1 Error Model and Noise Assumptions                   |

|   | 4 5   | 4.4.2 Experimental Setup                                  |

|   | 4.5   | Error Threshold Results                                   |

|   | 4.6   | Error Sensitivity Results                                 |

|   | 4.7   | Magic State Distillation                                  |

|   | 4.0   | Resource Estimates                                        |

|   | 4.8   | Conclusion                                                |

| 5  | EVA  | LUAT   | ING ARCHITECTURES AT THEIR LIMITS: IMPROVED COMPILA-                |

|----|------|--------|---------------------------------------------------------------------|

|    | TIO  | N MET  | THODS                                                               |

|    | 5.1  | Memo   | ry-Equipped Quantum Architectures: The Power of Random Access . 128 |

|    |      | 5.1.1  | Relevant Background                                                 |

|    |      | 5.1.2  | A Memory-Equipped Quantum Architecture                              |

|    |      | 5.1.3  | Experimental Setup                                                  |

|    |      | 5.1.4  | Results and Discussion                                              |

|    | 5.2  | Remai  | rks                                                                 |

|    | 5.3  | Time-  | Sliced Quantum Circuit Partitioning for Modular Architectures 157   |

|    |      | 5.3.1  | Relevant Background                                                 |

|    |      | 5.3.2  | Mapping Qubits to Clusters                                          |

|    |      | 5.3.3  | Lookahead Weights                                                   |

|    |      | 5.3.4  | Experimental Setup                                                  |

|    |      | 5.3.5  | Results and Discussion                                              |

|    |      | 5.3.6  | Remarks                                                             |

|    | 5.4  | Noise- | Adaptive Compiler Mappings for Noisy Intermediate Scale Quantum     |

|    |      | Comp   | uters                                                               |

|    |      | 5.4.1  | Relevant Background                                                 |

|    |      | 5.4.2  | Overview of our Compilation Framework                               |

|    |      | 5.4.3  | Optimal Compilation: Detailed Approach                              |

|    |      | 5.4.4  | Heuristic Compilation                                               |

|    |      | 5.4.5  | Experimental Setup                                                  |

|    |      | 5.4.6  | Optimizing Execution Reliability                                    |

|    |      | 5.4.7  | Remarks                                                             |

|    | 5.5  | Orche  | strated Trios: Compiling for Efficient Communication in Quantum     |

|    |      | Progra | ams with 3-Qubit Gates                                              |

|    |      | 5.5.1  | Relevant Background                                                 |

|    |      | 5.5.2  | Orchestrated Trios                                                  |

|    |      | 5.5.3  | Evaluation                                                          |

|    |      | 5.5.4  | Results and Discussion                                              |

|    |      | 5.5.5  | Remarks                                                             |

| 6  | DIS  | CUSSIC | ON AND CONCLUSION                                                   |

| RI | EFER | ENCE   | S                                                                   |

# LIST OF FIGURES

| 2.1 | Reversible AND circuit using a single ancilla bit. The inputs are on the left,                           |    |

|-----|----------------------------------------------------------------------------------------------------------|----|

|     | and time flows rightward to the outputs. This AND gate is implemented using                              |    |

|     | a Toffoli (CCNOT) gate with inputs $q_0$ , $q_1$ and a single ancilla initialized to 0.                  |    |

|     | At the end of the circuit, $q_0$ and $q_1$ are preserved, and the ancilla bit is set to                  |    |

|     | 1 if and only if both other inputs are 1                                                                 | 10 |

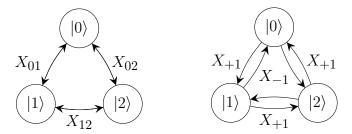

| 2.2 | The five nontrivial permutations on the basis elements for a qutrit. (Left) Each                         |    |

|     | operation here switches two basis elements while leaving the third unchanged.                            |    |

|     | These operations are self-inverses. (Right) These two operations permute the                             |    |

|     | three basis elements by performing a $+1 \mod 3$ and $-1 \mod 3$ operation.                              |    |

|     | They are each other's inverses                                                                           | 11 |

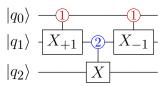

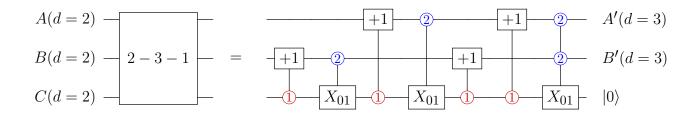

| 2.3 | A Toffoli decomposition via qutrits. Each input and output is a qubit. The                               |    |

|     | red controls activate on $ 1\rangle$ and the blue controls activate on $ 2\rangle$ . The first gate      |    |

|     | temporarily elevates $q_1$ to $ 2\rangle$ if both $q_0$ and $q_1$ were $ 1\rangle$ . We then perform the |    |

|     | X operation only if $q_1$ is $ 2\rangle$ . The final gate restores $q_0$ and $q_1$ to their original     |    |

|     | state                                                                                                    | 16 |

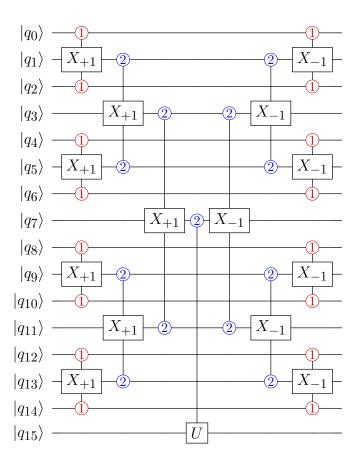

| 2.4 | Our circuit decomposition for the Generalized Toffoli gate is shown for 15                               |    |

|     | controls and 1 target. The inputs and outputs are both qubits, but we allow                              |    |

|     | occupation of the $ 2\rangle$ qutrit state in between. The circuit has a tree structure                  |    |

|     | and maintains the property that the root of each subtree can only be elevated                            |    |

|     | to $ 2\rangle$ if all of its control leaves were $ 1\rangle$ . Thus, the $U$ gate is only executed       |    |

|     | if all controls are $ 1\rangle$ . The right half of the circuit performs uncomputation                   |    |

|     | to restore the controls to their original state. This construction applies more                          |    |

|     | generally to any multiply-controlled $U$ gate. Note that the three-qutrit gates                          |    |

|     | are decomposed into 6 two-qutrit and 7 single-qutrit gates in our actual                                 |    |

|     | simulation, as based on the decomposition in [53]                                                        | 48 |

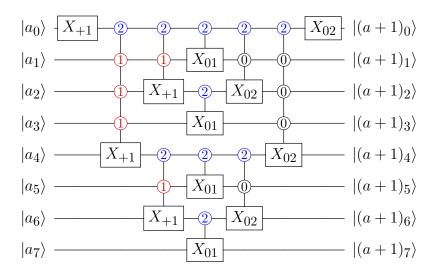

| 2.5 | Our circuit decomposition for the Incrementer. At each step in the design,                |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | multiply-controlled gates using the decomposition in Figure 2.4 are used to               |    |

|     | efficiently propagate carries over half of the subcircuit. The $ 2\rangle$ control checks |    |

|     | for carry generation and the chain of $ 1\rangle$ controls check for carry propagation.   |    |

|     | The circuit depth is $\log^2 N$ , which is only possible because of our log depth         |    |

|     | multiply-controlled gate primitive                                                        | 49 |

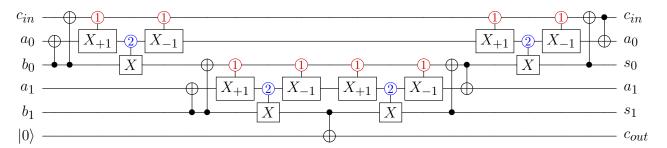

| 2.6 | The Cuccaro adder of [46] with the Toffoli gates replaced by our efficient                |    |

|     | decomposition. This only reduces the total depth of the circuit by a constant             |    |

|     | amount, i.e. no asymptotic benefit is obtained. There are several simplifications         |    |

|     | which can be made to this circuit, most notably the controlled $X_{-1}$ followed          |    |

|     | immediately by a controlled $X_{+1}$ in several places. For clarity we've kept these      |    |

|     | gates to see the direct replacement of our Toffoli decomposition into existing            |    |

|     | circuits                                                                                  | 49 |

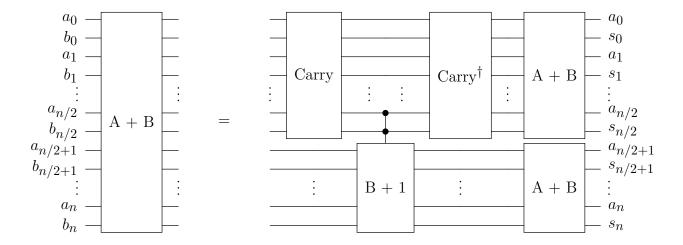

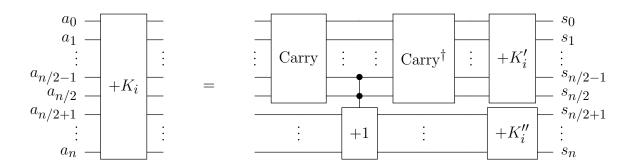

| 2.7 | Decomposing the A+B circuit with intermediate qutrits. We take as input                   |    |

|     | two $n$ qubit registers and output the sum $S$ onto the bits of register $B$ while        |    |

|     | leaving register $A$ unchanged. In this approach, we first decide if there will be        |    |

|     | a carry generated on the top half of the inputs. If so, we apply a $+1$ gate to the       |    |

|     | bottom half of the inputs (specifically on the bits of $B$ ) and then recursively         |    |

|     | add the first half of $A$ and $B$ and second half of $A$ and $B$ in parallel. The         |    |

|     | carry circuit outputs an encoded carry status on $a_{n/2}, b_{n/2}$ . The controlled      |    |

|     | $+1$ can be implemented by just modifying the initial $X_{+1}$ and final $X_{02}$ gates   |    |

|     | of the incrementer to be controlled by the final output carry status. This                |    |

|     | decomposition is $O(\log^3 n)$ depth provided the Carry circuit is $O(\log n)$ depth      |    |

|     | and the incrementer is $O(\log^2 n)$ depth                                                | 50 |

| 2.8  | On the left is the encoding for generate (g), propagate (p), and kill (k) carry   |    |

|------|-----------------------------------------------------------------------------------|----|

|      | statuses. On the right is the result of combining two input carry statuses $C_i$  |    |

|      | and $C_j$ with $C_i$ corresponding to the less significant bits. Notice the order |    |

|      | matters, e.g. $k + g = g$ but $g + k = k$                                         | 50 |

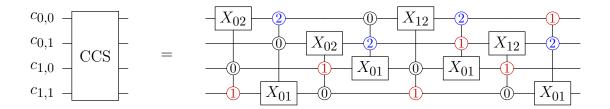

| 2.9  | Realization of the truth table of Table 2.2 as the gadget "Combine Carry          |    |

|      | Status" (CCS). While this gate is expensive in terms of two qutrit gates, it is   |    |

|      | constant depth                                                                    | 51 |

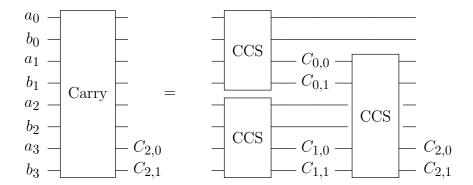

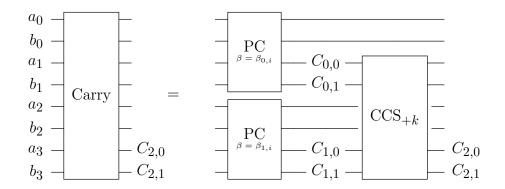

| 2.10 | Realizing the Carry operation in sublinear depth for $n=4$ inputs using the       |    |

|      | CCS gadget. The result is a (11) if and only if a carry is generated, while       |    |

|      | leaving all of the remaining bits as junk, possibly in ternary states. The CCS    |    |

|      | blocks always take four qubits as inputs, the first and last two bits and output  |    |

|      | a binary output on the last two inputs. In the context of the $A+B$ adder, we     |    |

|      | take this output carry status and use it to control an incrementer on the more    |    |

|      | significant bits. Afterwards, we would apply the inverse of the cascade on the    |    |

|      | right to return to the original inputs; this step is omitted here                 | 51 |

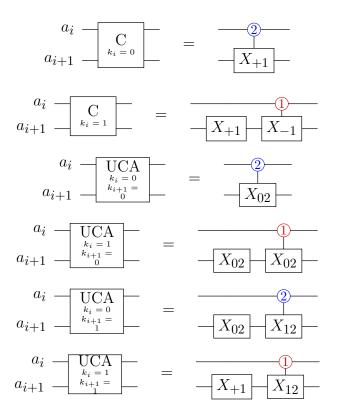

| 2.11 | The carry $(C)$ and UnCompute and Add (UCA) gadgets used for linear $+K$          |    |

|      | adder circuit. There are several instances which are a function of the specific   |    |

|      | $k_i$ and $k_{i+1}$ values                                                        | 52 |

| 2.12 | Linear $+K$ adder, with carry out on a register of size 4. We assume $k_0=1$      |    |

|      | and we use the gadgets of Figure 2.11. For no carry out, i.e. $+K \mod 2^{ K }$   |    |

|      | simply omit the final $C$ component in the cascade. Note a $X_{+1}$ on an ancilla |    |

|      | has the same effect as a $X_{01}$ allowing us to use the same $C$ gadget          | 52 |

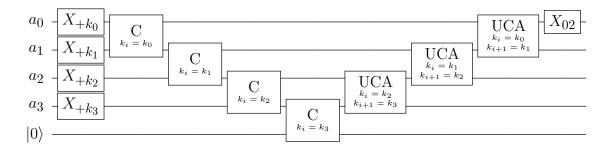

| 2.13 | The Decomposition of the $+K$ circuit into a sequence of $+K_i$ circuits, for     |    |

|      | $i \in [0, M]$ , where M is a constant                                            | 53 |

| 2.14 | The decomposition of the $+K_i$ blocks of Figure 2.13 in $O(\log^3 n)$ depth. Notice            |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | again, the controlled incrementer is done by adding two controls, the carry                     |    |

|      | status output from the Carry circuit to the first and final gate of the incrementer.            |    |

|      | The truth table for this transformation has been omitted for simplicity                         | 53 |

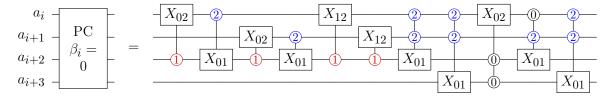

| 2.15 | The Prepare Carry (PC) circuit for when $\beta_i = 0$ . This takes four bits of input           |    |

|      | $A$ and the known constant $\beta_i$ and outputs on the last two bits the carry status          |    |

|      | for this group of bits on its own, adding $(a_i a_{i+1} a_{i+2} a_{i+4}) + (0000)$ . The other  |    |

|      | two inputs are left in possibly ternary states                                                  | 53 |

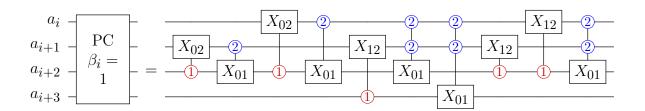

| 2.16 | The Prepare Carry (PC) circuit for when $\beta_i = 1$ . This takes four bits of                 |    |

|      | input A and the known constant $\beta_i$ and outputs on the last two bits the carry             |    |

|      | status for this group of bits on its own, adding $(a_i a_{i+1} a_{i+2} a_{i+4}) + (1000)$ . The |    |

|      | other two inputs are left in possibly ternary states. The truth table for this                  |    |

|      | transformation has been omitted for simplicity                                                  | 53 |

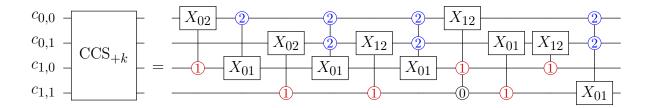

| 2.17 | Similar to the Combine Carry Circuit (CCS) of Figure 2.9, the $\mathrm{CCS}_{+K}$ gadget        |    |

|      | combines carry statuses of the type found in Table 2.3. This gadget always                      |    |

|      | leaves the final two inputs as the new carry status while leaving the other two                 |    |

|      | inputs possibly in ternary states. The truth table for this transformation has                  |    |

|      | been omitted for simplicity.                                                                    | 54 |

| 2.18 | Using the PC and $\mathrm{CCS}_{+K}$ gadgets, we can produce an $O(\log n)$ depth Carry         |    |

|      | circuit for the $+K_i$ circuit                                                                  | 54 |

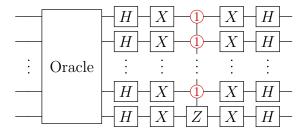

| 2.19 | Each iteration of Grover Search has a multiply-controlled $Z$ gate. Our loga-                   |    |

|      | rithmic depth decomposition, reduces a $\log M$ factor in Grover's algorithm to                 |    |

|      | $\log \log M$                                                                                   | 54 |

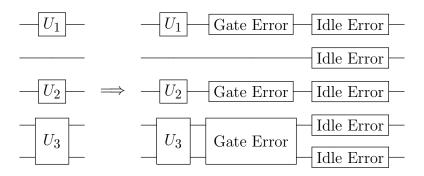

| 2.20 | This Moment comprises three gates executed in parallel. To simulate with                |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | noise, we first apply the ideal gates, followed by a gate error noise channel           |    |

|      | on each affected qudit. This gate error noise channel depends on whether the            |    |

|      | corresponding gate was single- or two- qudit. Finally, we apply an idle error to        |    |

|      | every qudit. The idle error noise channel depends on the duration of the Moment.        | 55 |

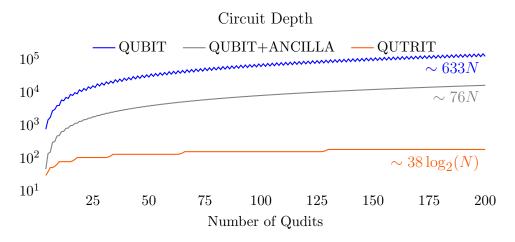

| 2.21 | Exact circuit depths for all three benchmarked circuit constructions for                |    |

|      | the N-controlled Generalized Toffoli up to $N=200.$ Both QUBIT and                      |    |

|      | QUBIT+ANCILLA scale linearly in depth and both are bested by QUTRIT's                   |    |

|      | logarithmic depth                                                                       | 55 |

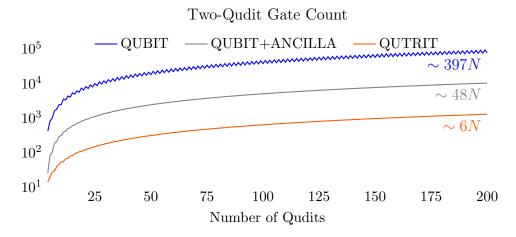

| 2.22 | Exact two-qudit gate counts for the three benchmarked circuit constructions             |    |

|      | for the N-controlled Generalized Toffoli. All three plots scale linearly; however       |    |

|      | the QUTRIT construction has a substantially lower linearity constant. $$                | 56 |

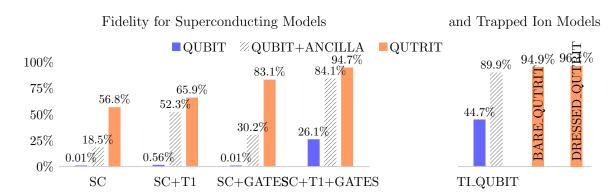

| 2.23 | Circuit simulation results for all possible pairs of circuit constructions and noise    |    |

|      | models. Each bar represents 1000+ trials, so the error bars are all $2\sigma < 0.1\%$ . |    |

|      | Our QUTRIT construction significantly outperforms the QUBIT construction.               |    |

|      | The QUBIT+ANCILLA bars are drawn with dashed lines to emphasize that                    |    |

|      | it has access to an extra ancilla bit, unlike our construction                          | 56 |

| 2.24 | The compression of 3 qubits into 2 qutrits and an ancilla, $ 0\rangle$ . All +1 gates   |    |

|      | are done modulo 3. Using a sequence of qutrit gates, we can transform three             |    |

|      | input qubits into the desired ancilla. When A, B and C are not going to be              |    |

|      | used for a long time in the circuit, they can be temporarily repurposed as an           |    |

|      | ancilla bit elsewhere in the circuit. When we want to operate on these stored           |    |

|      | bits, we run the inverse of this circuit using $any$ ancilla for the third qubit        | 57 |

| 2.25 | The compression of 2 qubits into a single ququart and generating an ancilla,                 |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | $ 0\rangle$ . The +2 gate here is done modulo 4. This operation takes as input two           |    |

|      | qubits, A and B, and produces a single ququart and an ancilla $ 0\rangle$ . To do this,      |    |

|      | we need only 3 two-ququart gates. Similarly, to retrieve the stored information,             |    |

|      | we can do the inverse of this operation using any ancilla for the second qubit.              | 57 |

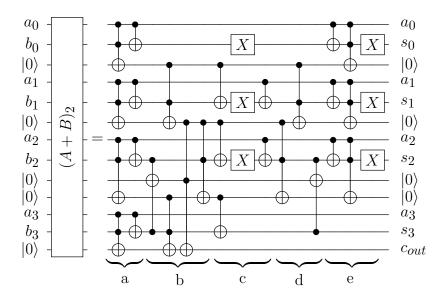

| 2.26 | An adder circuit from $[58]$ on two four-bit registers $A$ and $B$ with a carry-             |    |

|      | out bit using ancilla. The sum $S$ is computed in-place on register $B$ while                |    |

|      | A is untouched and the ancilla are restored to $ 0\rangle$ . We use this as a sub-           |    |

|      | component of our general decomposition. Each of the ancilla in this circuit                  |    |

|      | can be generated from other input qubits not shown here via our compression                  |    |

|      | circuits. Part a of the circuit computes carry generate and propagate for each               |    |

|      | bit position. Part b computes the carry-in for every bit position. Part c does               |    |

|      | the addition, storing the output in register $B$ . Parts d and e uncompute b and             |    |

|      | a respectively, restoring the ancilla back to $ 0\rangle$                                    | 58 |

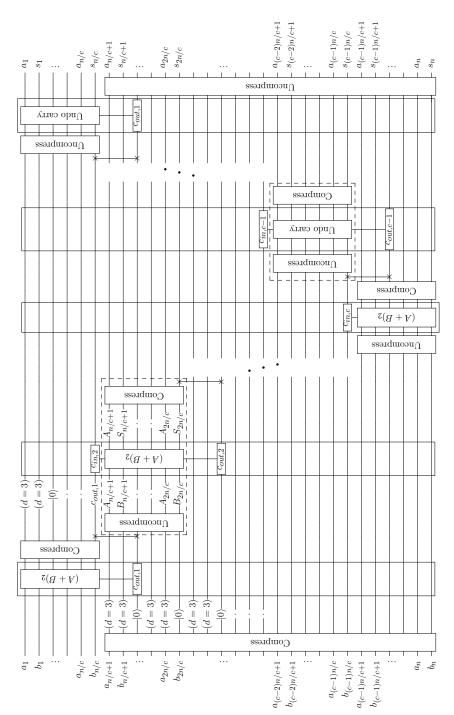

| 2.27 | Our $A+B$ adder that uses no external ancilla. The variant shown here for                    |    |

|      | $c=5$ uses 2-3-1 compression to generate one ancilla (marked as $ 0\rangle)$ for every       |    |

|      | three unused qubits, storing their values in two qutrits (marked as $d=3$ ). A               |    |

|      | box is drawn around every $(A + B)_2$ and Undo carry gate to indicate that                   |    |

|      | they use all the generated ancilla across the circuit. $c_{out,i}$ or $c_{in,i}$ is included |    |

|      | on some of the gates to indicate when the carry-in and carry-out versions are                |    |

|      | used and on which ancilla the carry-out is stored. The SWAP gates (pairs of                  |    |

|      | $\times$ in the diagram) simply move a carry-out bit to another ancilla where it is          |    |

|      | used as the next carry-in. The two blocks of gates shown with dashed lines are               |    |

|      | repeated $c-2=3$ times along the diagonal indicated. If 2-4-1 compression is                 |    |

|      | used, an ancilla is generated for every two unused qubits so only $c=4$ blocks               |    |

|      | are needed. The depth of this circuit is $O(\log n)$                                         | 59 |

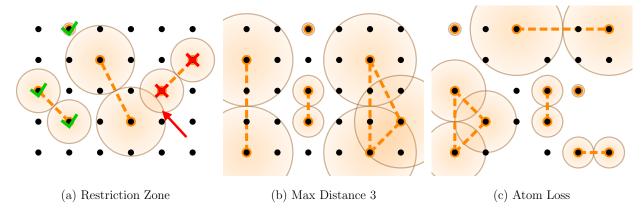

| 3.1 | Examples of interactions on a neutral atom device. (a) Interactions of various   |    |

|-----|----------------------------------------------------------------------------------|----|

|     | distances are permitted up to a maximum. Gates can occur in parallel if their    |    |

|     | zones do not intersect. The interaction marked with green checks can occur in    |    |

|     | parallel with the middle interaction. (b) The maximum interaction distance       |    |

|     | specifies which physical qubits can interact. Compiler strategies suited for     |    |

|     | this variable distance are needed for neutral atom architectures. (c) Neutral    |    |

|     | atom systems are prone to sporadic atom loss. Efficient adaptation to this loss  |    |

|     | reduces computation overhead                                                     | 61 |

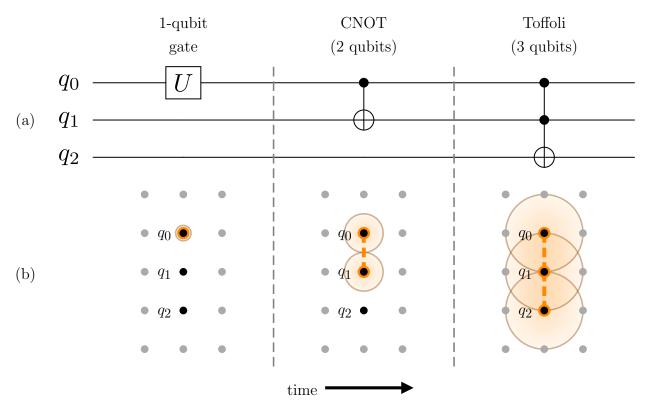

| 3.2 | A quantum circuit with a 1, 2, and 3 qubit gate translated to interactions on a  |    |

|     | NA device. These systems allow the execution of multiqubit gates. For 2 and      |    |

|     | 3 qubit gates the interacting qubits are excited to Rydberg states. Interactions |    |

|     | are possible if all interacting qubits are closer than the maximum interaction   |    |

|     | distance                                                                         | 64 |

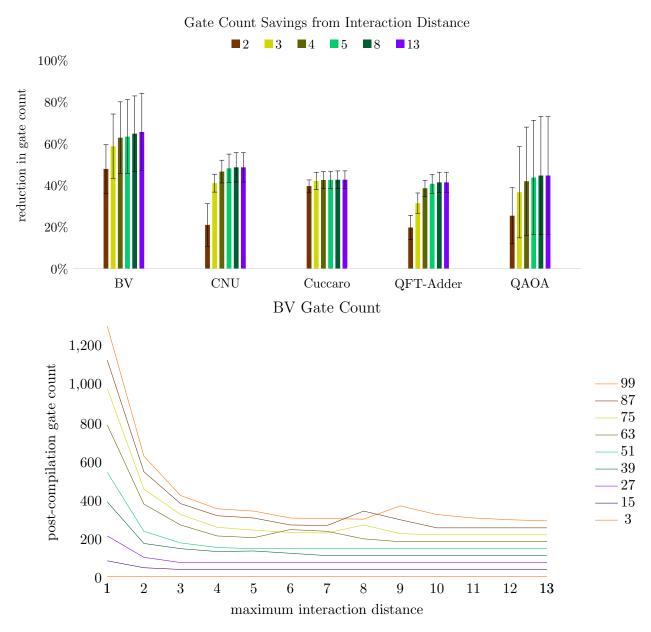

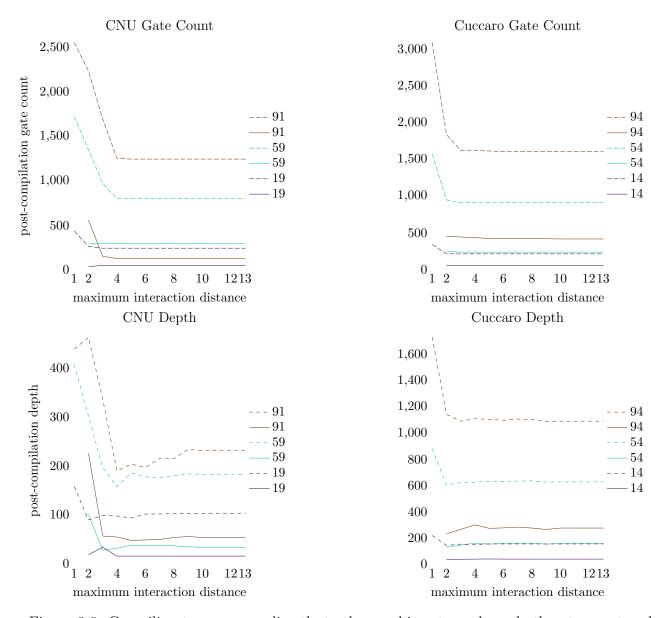

| 3.3 | Post-compilation gate count across benchmarks. On the top are percent savings    |    |

|     | over the distance 1 baseline averaged over program sizes up to 100 qubits.       |    |

|     | Each color is a max interaction distance. Noticeably, there is less additional   |    |

|     | improvement as the MID increases, indicating most benefit is gained for smaller  |    |

|     | distances. On the bottom is a sample benchmark (holds in general) with many      |    |

|     | program sizes compiled for the whole range of MIDs. As the program size          |    |

|     | increases, larger MID show benefit before flattening off                         | 86 |

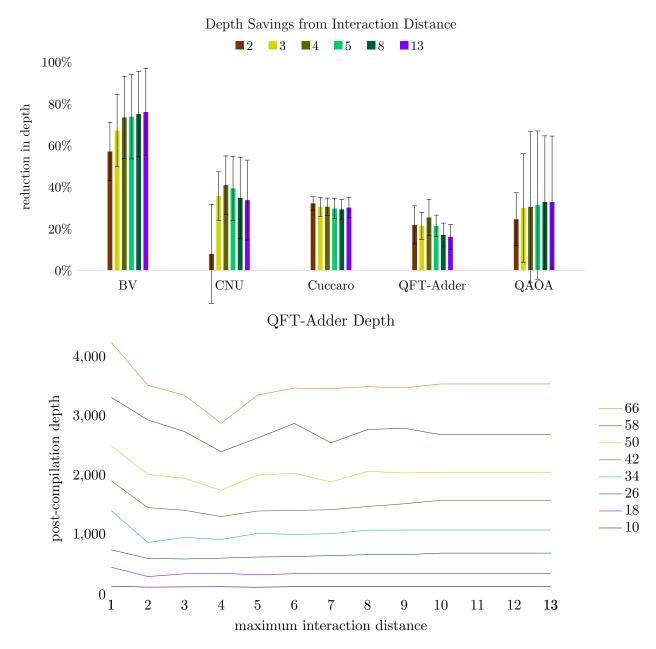

| 3.4 | Post-compilation depth across all benchmarks. On the top, the reduction in         |    |

|-----|------------------------------------------------------------------------------------|----|

|     | depth over the distance 1 baseline. Each bar is the average over all benchmark     |    |

|     | sizes. On the bottom we see a similar drop off in post-compilation depth for       |    |

|     | the QFT-Adder. We've chosen this specific benchmark to highlight the effect        |    |

|     | of restriction zones. Here we show a subset of all sizes run. Depth initially      |    |

|     | drops but for larger interaction distances some of this benefit is lost. We expect |    |

|     | this to be more dramatic for even larger programs                                  | 87 |

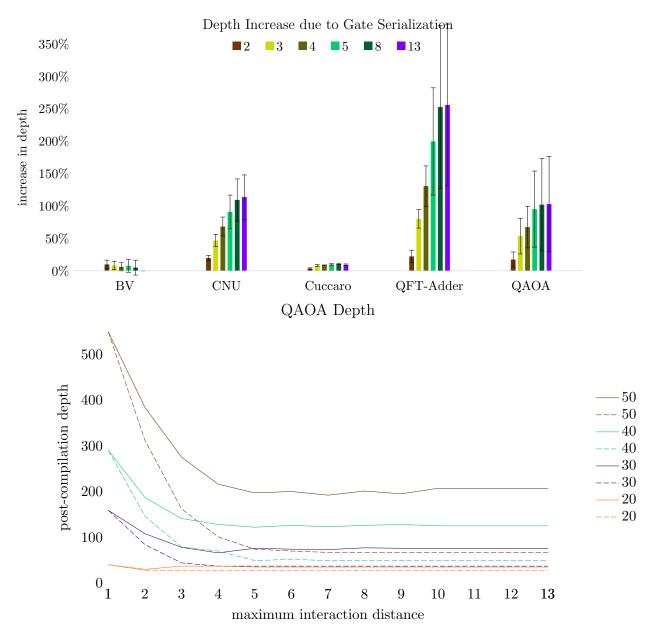

| 3.5 | The induced restriction zone from interaction distance increases serialization.    |    |

|     | In the prior results this is hard to discern because compared to low interaction   |    |

|     | distance the amount of gate savings translates to depth reduction. Here we         |    |

|     | compare benchmarks compiled with our restriction zone and compare to a             |    |

|     | program with no restriction zone, to mimic an ideal, highly parallel execution.    |    |

|     | The existence of a restriction zone most effect on programs which are parallel     |    |

|     | to begin with. On the bottom we directly compare this effect on the QAOA           |    |

|     | benchmark; solid line is compiled with realistic restriction zone and dashed is    |    |

|     | ideal. The separation between the corresponding lines signifies the effect of      |    |

|     | the restriction zone                                                               | 88 |

| 3.6 | Compiling to programs directly to three qubit gates reduces both gate count        |    |

|     | and depth. Here we highlight a serial and parallel application written to three    |    |

|     | qubit gates. Here dashed lines are compiled to two qubit gates decomposing         |    |

|     | all Toffoli gates before mapping and routing. Solid lines compile with native      |    |

|     | Toffoli gates. With native implementation of three qubit gates we obtain huge      |    |

|     | reductions in both depth and gate count for both benchmarks                        | 89 |

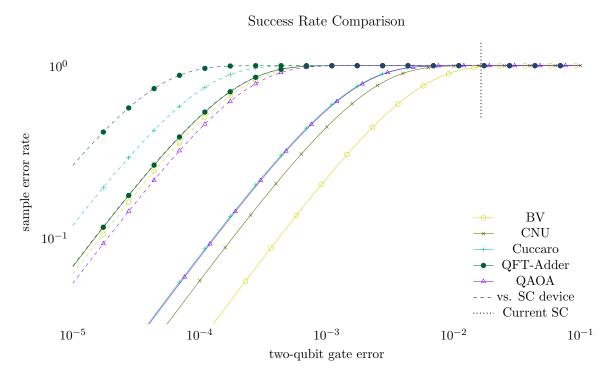

| 3.7 | Program success rate as a function of two-qubit error rate. Because current NA   |    |

|-----|----------------------------------------------------------------------------------|----|

|     | error rates are lagging behind competitive technologies we scan over a range     |    |

|     | of two-qubit error rates for each of the benchmarks all on 50 qubit programs     |    |

|     | (49 for CNU) with max interaction distance of 3. Examining pairs of solid and    |    |

|     | dashed lines we can compare NA to SC. In the limit of very low two qubit error   |    |

|     | rate, systems can support error correction. Both SC and NA systems scale at      |    |

|     | roughly the same rate (slope of the line) but the NA system diverges from the    |    |

|     | completely random outcome at higher error, allowing us to run programs on        |    |

|     | the hardware much sooner                                                         | 90 |

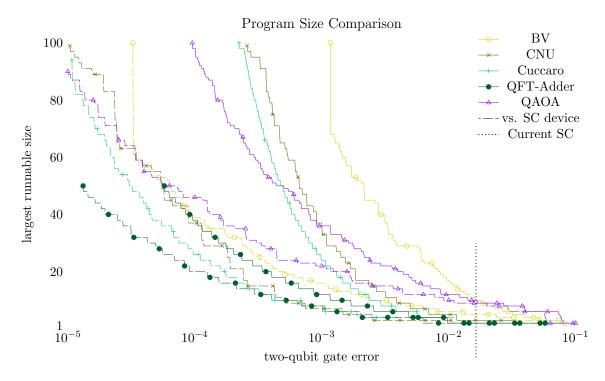

| 3.8 | Another way to examine the data of Figure 3.7 is to ask, given a desired         |    |

|     | program success rate, what the required two qubit error rate is. Here we sweep   |    |

|     | again over two qubit error rates and record the maximum program size to run      |    |

|     | with success probability greater than 2/3. Again, examining pairs of solid and   |    |

|     | dashed lines we can compare NA to SC. With the reduced gate counts and           |    |

|     | depth we expect to be able to run larger programs sooner                         | 91 |

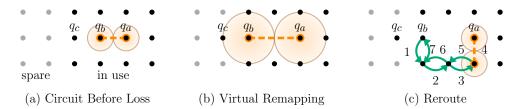

| 3.9 | Examples of two different atom loss coping strategies. (a) shows the initial     |    |

|     | configuration of three qubits, with the spare qubits in a light grey, and in use |    |

|     | qubits black. (b) Represents how the atoms are shifted into the spare qubits to  |    |

|     | accommodate a lost atom under the virtual remapping strategy. Notice that        |    |

|     | the interaction is no longer within interaction distance 1. (c) Demonstrates how |    |

|     | the qubits can be swapped to a valid interaction configuration, and returned     |    |

|     | for rerouting strategies. Numbers indicate the order of swaps                    | 91 |

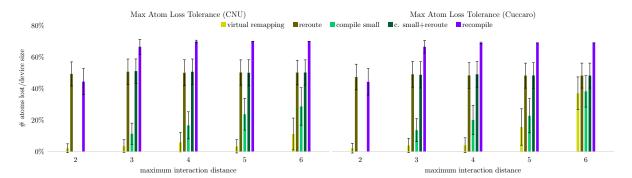

| 3.10 | Atom loss as a percentage of total device size which can be sustained before a  |    |

|------|---------------------------------------------------------------------------------|----|

|      | reload of the array is needed. Each program is 30 qubits on a 100 qubit device. |    |

|      | As the interaction distance increases most strategies can sustain more atom     |    |

|      | loss. Strategies like full recompilation can sustain large numbers of atom loss |    |

|      | but as we will see are expensive computationally. Fast, hardware solutions or   |    |

|      | hybrid solutions can sustain fewer numbers of holes but have lower overhead.    |    |

|      | We show two representative benchmarks parallel vs. serial                       | 92 |

| 3.11 | For strategies which modify the program such as recompilation or rerouting      |    |

|      | strategies, additional gates could be added leading to a lower overall success  |    |

|      | rate. Here we trace the success rate of our three program modifying strategies. |    |

|      | The full recompilation strategy (circles) is a rough upper bound which best     |    |

|      | accounts for holes as they appear being able to move the entire program to      |    |

|      | a more appropriate location and route best. The gap between strategies on       |    |

|      | the same MID gets smaller as the MID gets larger. Here we've chosen the         |    |

|      | two-qubit error rate corresponding to approximate 0.6 success rate to begin     |    |

|      | with (based on Figure 3.8) in order to best demonstrate the change in shot      |    |

|      | success probability over a range of atom loss                                   | 92 |

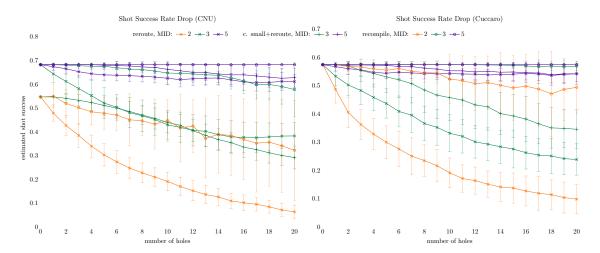

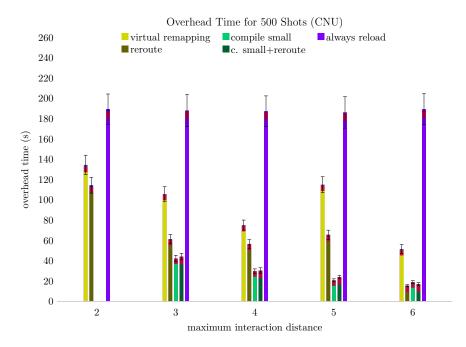

| 3.12 | Strategies that are able reduce the number of reloads necessary greatly reduce  |    |

|      | the overhead time when running circuits. Here we show the overhead time         |    |

|      | for all strategies except recompilation. The proportion of time dedicated to    |    |

|      | reloading is shown by the dominate color in each bar, followed by fluorescence  |    |

|      | in red, and recompilation in black. Any strategy whose overhead exceeds that    |    |

|      | of always reloading, such as full recompilation, should not be considered       | 93 |

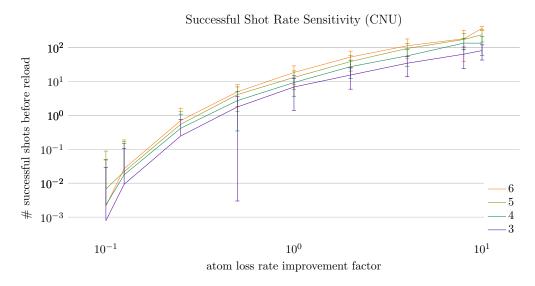

| 3.13 | Sensitivity to the rate of atom loss for the balanced Compile Small and Reroute    |     |

|------|------------------------------------------------------------------------------------|-----|

|      | strategy. In prior experiments we used a fixed rate of $2\%$ atom loss. For larger |     |

|      | systems this rate could be worse and in the future we might expect this rate       |     |

|      | to be much better. For each interaction distance we see as the rate of atom        |     |

|      | loss gets better we can run many more trials before we must perform a reload       |     |

|      | and reset. Some error bars don't show on the log axis.                             | 93  |

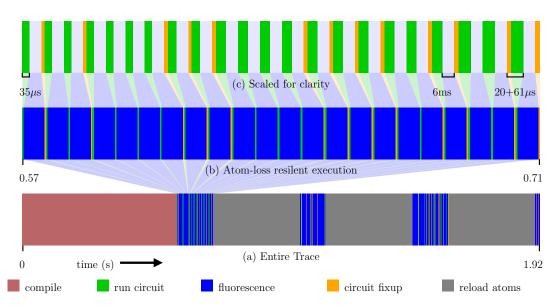

| 3.14 | A timeline of 20 successful shots for Compile Small and Reroute with reload        |     |

|      | time of 0.3 s and fluorescing time of 6 ms. A majority of the overhead time is     |     |

|      | contributed by the reload time and fluorescence, indicating, that the duration     |     |

|      | and count of these actions is crucial to overall runtime                           | 94  |

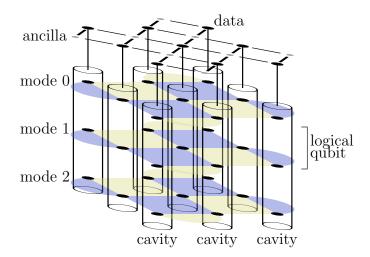

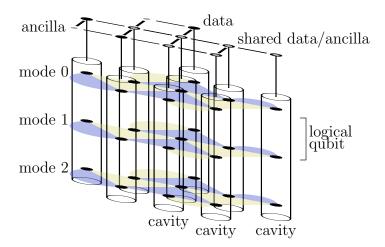

| 4.1  | Our fault-tolerant architecture with random-access memory local to each            |     |

| 1.1  | transmon. On top is the typical 2D grid of transmon qubits. Attached below         |     |

|      |                                                                                    |     |

|      | each data transmon is a resonant cavity storing error-prone data qubits (shown     |     |

|      | as black circles). This pattern is tiled in 2D to obtain a 2.5D array of logical   |     |

|      | qubits. Our key innovation here is storing the qubits that make up each            |     |

|      | logical qubit (shown as checkerboards) across many cavities to enable efficient    |     |

|      | computation                                                                        | 97  |

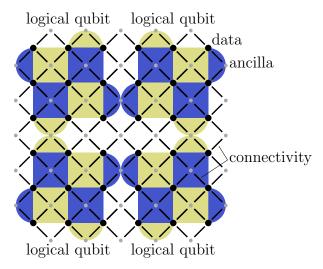

| 4.2  | A typical 2D superconducting qubit architecture. The dots are transmon             |     |

|      | qubits where black are used as data and gray are used as ancilla for error         |     |

|      | correction. The lines indicate physical connections between qubits that allow      |     |

|      | operations between them. Four logical qubits, each consisting of 9 error-prone     |     |

|      | data qubits, are shown here in the rotated surface code with distance 3. Z         |     |

|      | parity checks are shaded yellow (light) and X parity checks are shaded blue        |     |

|      | (dark) where checks on only 2 data are drawn as half circles                       | 100 |

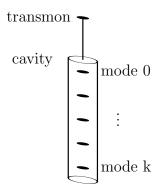

| 4.3 | A close-up representation of the qubit memory technology we use. On top is                |     |

|-----|-------------------------------------------------------------------------------------------|-----|

|     | a superconducting transmon qubit physically connected to a resonant super-                |     |

|     | conducting cavity. This cavity has many resonant modes each used to store a               |     |

|     | qubit. These qubits can be loaded and stored (with random access) via the                 |     |

|     | transmon                                                                                  | 101 |

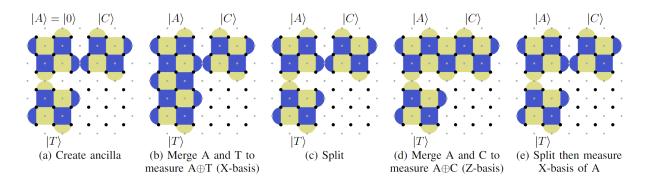

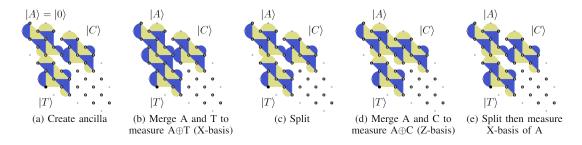

| 4.4 | The lattice surgery operations to perform a logical CNOT on the standard                  |     |

|     | surface code (and directly supported in our architecture). Given control and              |     |

|     | target qubits $ C\rangle$ and $ T\rangle$ , a CNOT is performed by enabling and disabling |     |

|     | the parity checks as shown across 6 timesteps ((e) is two steps). We show this            |     |

|     | complex process to contrast with the fast transversal CNOT enabled by our                 |     |

|     | architecture (described later in Section 4.3.2)                                           | 103 |

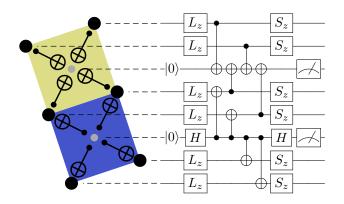

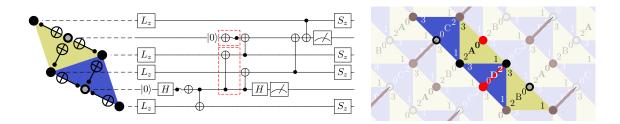

| 4.5 | Circuit showing how to execute our Natural embedding on hardware. Left:                   |     |

|     | The layout of eight data (black) and two ancilla (gray) in hardware. CNOT                 |     |

|     | operations between qubits are drawn between. Right: A circuit diagram of                  |     |

|     | the operations applied over time where each horizontal line corresponds to a              |     |

|     | qubit and each box or symbol is an operation. The steps are $L_z$ : load from             |     |

|     | memory mode $z$ , $ 0\rangle$ : reset ancilla, CNOTs: compute the Z or X parity, Meter:   |     |

|     | measure the result, $S_z$ : store back to memory                                          | 106 |

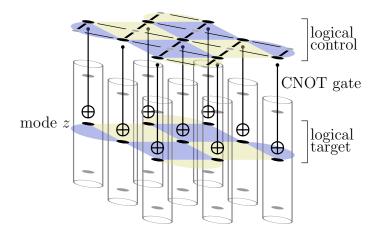

| 4.6 | The transversal CNOT enabled by our 2.5D architecture. The data qubits for                |     |

|     | the control logical qubit are loaded into the transmons. Transmon-mediated                |     |

|     | CNOTs to mode $z$ for every data qubit perform the logical operation. This                |     |

|     | takes one timestep to perform, 6x better than a lattice surgery CNOT                      | 122 |

|     |                                                                                           |     |

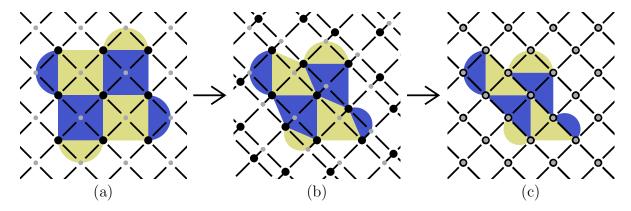

| 4.7  | Transformation from Natural to Compact. (a) Natural embedding: Only                                       |     |

|------|-----------------------------------------------------------------------------------------------------------|-----|

|      | data have attached cavities (not shown). (b) The transformation: Z ancilla                                |     |

|      | (over yellow/light areas) merge with the upper-right data transmon and X                                  |     |

|      | ancilla (over blue/dark areas) merge with the lower-left data transmon. The                               |     |

|      | opposite parings are key to keeping 4-way grid connectivity. (c) Compact                                  |     |

|      | embedding: All ancilla transmons without attached cavities have been removed.                             |     |

|      | All remaining transmons have cavities and are used as both data and ancilla.                              | 122 |

| 4.8  | A 3D view of our Compact embedding. Shown at the top is the 2D grid                                       |     |

|      | of transmon qubits. Attached below every transmon is a resonant cavity.                                   |     |

|      | Compact surface code patches are shown stored, one in each mode. This                                     |     |

|      | deformed patch can be tiled in 2D                                                                         | 123 |

| 4.9  | The Compact lattice surgery operations to perform a CNOT. The logical                                     |     |

|      | operations performed are identical to Figure 4.4 but the corresponding physical                           |     |

|      | operations are arranged as shown in Figure 4.7. This uses half as many                                    |     |

|      | transmons as Natural. As before, it takes 6 timesteps of $d$ error correction                             |     |

|      | cycles each                                                                                               | 123 |

| 4.10 | The CNOT sequence for parity checks in Compact. Left: A quantum circuit                                   |     |

|      | showing the hardware operations over time. Right: The CNOT execution                                      |     |

|      | order repeats $A_0D_2$ , $A_1D_3$ , $A_2C_0$ , $A_3C_1$ , $B_0C_2$ , $B_1C_3$ , $B_2D_0$ , $B_3D_1$ . The |     |

|      | AB and $CD$ sequences run in parallel but offset to ensure ancilla and data use                           |     |

|      | do not conflict. CNOTs for $A_0D_2$ are marked in red where an isolated circle                            |     |

|      | indicates a transmon-mediated CNOT                                                                        | 123 |

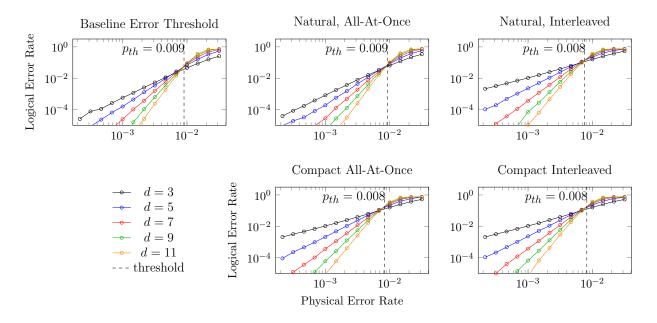

| 4.11 | Error thresholds for the baseline 2D architecture and Natural and Compact               |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | variants of our 2.5D architecture. The thresholds are comparable to the baseline        |     |

|      | indicating the space savings obtained in our system does not substantially              |     |

|      | reduce the error thresholds. The slopes of the lines in this figure indicate,           |     |

|      | post-threshold, how much improvement in physical error rates improve logical            |     |

|      | error rate. Except for the baseline, all use a cavity size of 10                        | 124 |

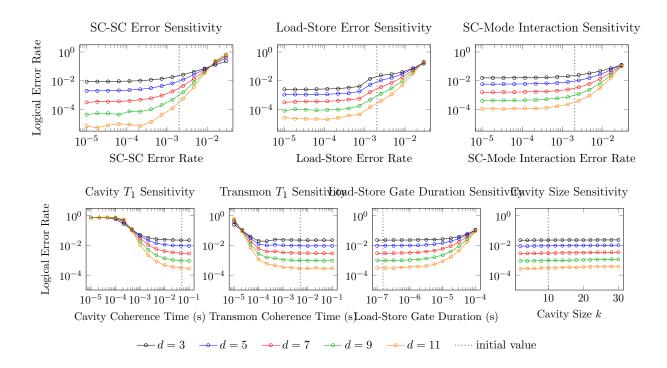

| 4.12 | Sensitivity of logical error rate to various error sources in Compact, Interleaved.     |     |

|      | The logical error rates are most sensitive to physical error of Loads/Stores and        |     |

|      | SC-SC gates. The logical error rate is less sensitive to the coherence times and        |     |

|      | mostly insensitive to effects of load-store duration and cavity size                    | 125 |

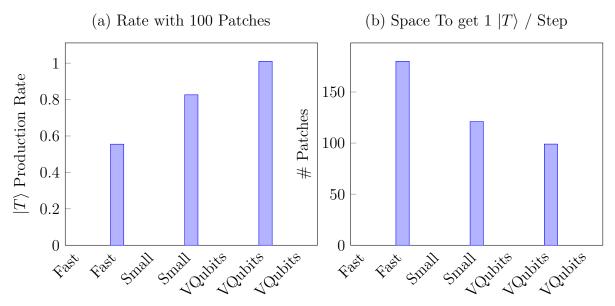

| 4.13 | (a) The T-state generation rates of three different circuits. Higher generation         |     |

|      | rate is better. (b) The space, in terms of number of patches, required to               |     |

|      | produce a single $ T\rangle$ per time step. Lower is better. Fast [124] and Small [123] |     |

|      | work in the surface code and do not use memory. VQubits is implemented                  |     |

|      | with transversal CNOTs in our 2.5D architecture. All are based on [29]                  | 126 |

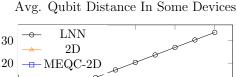

| 5.1  | Average qubit distance on several instances of near-term target architectures.          |     |

|      | Average qubit distance approximates how many SWAPs are necessary to                     |     |

|      | interact an arbitrary pair of qubits. LNN architectures scale extremely poorly          |     |

|      | in this metric resulting in a large number of added gates and depth. 2D and             |     |

|      | MEQC architectures scale much better. We show this translates into reduced              |     |

|      | number of gates and reduced depth as we scale into the future                           | 128 |

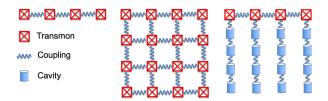

| 5.2 | Both current and the proposed MEQC device. On the left is a LNN device                                |     |

|-----|-------------------------------------------------------------------------------------------------------|-----|

|     | where adjacent superconducting transmons are coupled enabling two qubit                               |     |

|     | interactions. In the center is a 2D mesh architecture common among current                            |     |

|     | manufacturers. On the right is the proposed MEQC architecture with trans-                             |     |

|     | mons arranged in a line. Each transmon has an attached cavity which stores in                         |     |

|     | memory multiple qubits. To operate on the qubits, they must first be loaded                           |     |

|     | into the transmons                                                                                    | 129 |

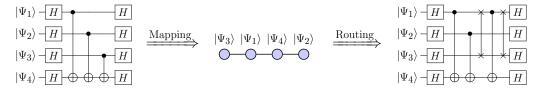

| 5.3 | Compiling to near-term devices is a multi-step process. First we map the                              |     |

|     | logical, circuit qubits to the physical hardware qubits. Based on this placement                      |     |

|     | and the input program, we insert SWAPs in order to interact distant qubits.                           |     |

|     | Here we compile a simple quantum program, Bernstein-Vazirani, to a 4 qubit                            |     |

|     | LNN architecture. Quantum programs, like the input program on the left are                            |     |

|     | a sequence of gates specified on qubits. In this example, based on the given                          |     |

|     | mapping, a pair of SWAPs are required to execute a CNOT between $ \Psi_3\rangle$ and                  |     |

|     | $ \Psi_4\rangle$                                                                                      | 132 |

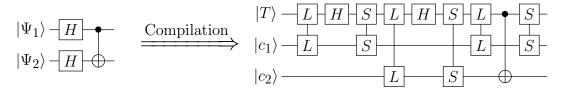

| 5.4 | Compiling a small program to a MEQC device. In this case we map the input                             |     |

|     | qubits $ \Psi_1\rangle$ and $ \Psi_2\rangle$ to one of the two available cavity modes. When executing |     |

|     | the gates, we first execute a Load to move the qubit to the connected transmon.                       |     |

|     | The gate is then executed and the qubit is returned to its original mode via a                        |     |

|     | Store. We represent Loads as $L-L$ and Stores as $S-S$                                                | 136 |

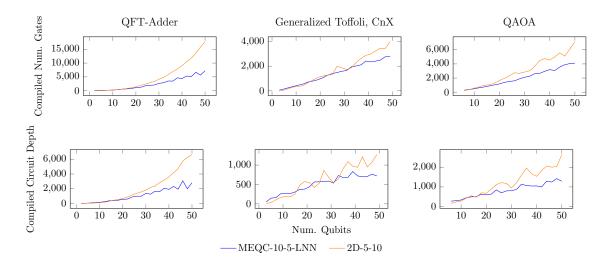

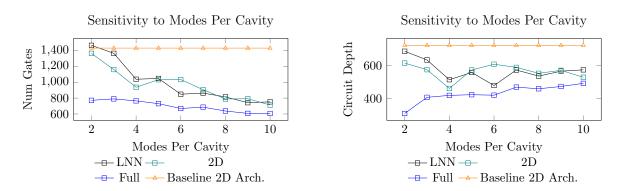

| 5.5 | The scaling of depth and gate count in a subset of our benchmarks. LNN-                               |     |

|     | 50 is omitted because it adds substantially more gates than both of these                             |     |

|     | architectures and as such is not competitive. In many cases, 2D-5-10 is                               |     |

|     | competitive with the proposed architecture, however, clear separation emerges                         |     |

|     | in all cases.                                                                                         | 143 |

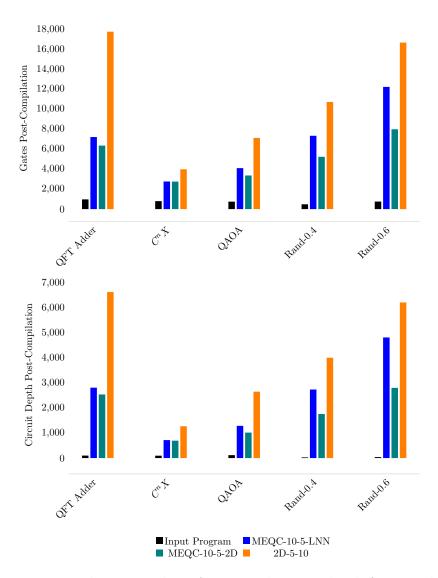

| 5.6 | Post-compilation number of gates and circuit depth for 50 qubit input programs  |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | on all benchmarks. In every case, MEQC with transmons arranged with             |     |

|     | as a chain or a mesh shows improvement over a more standard 2D mesh             |     |

|     | qubit arrangement. The increase in gate count in MEQC architectures is          |     |

|     | approximately $60\%$ due to loads and stores and the rest from SWAPs. By        |     |

|     | requiring fewer gates, we reduce the possibility of gate-induced error          | 148 |

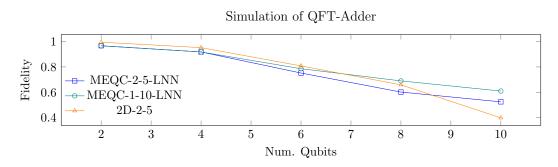

| 5.7 | Output fidelity for full density simulations of the QFT Adder on 2-10 qubits.   |     |

|     | Even with more gates in these small instances, programs compiled to MEQC        |     |

|     | devices are competitive, and at 10 qubits we see the start of advantage         | 149 |

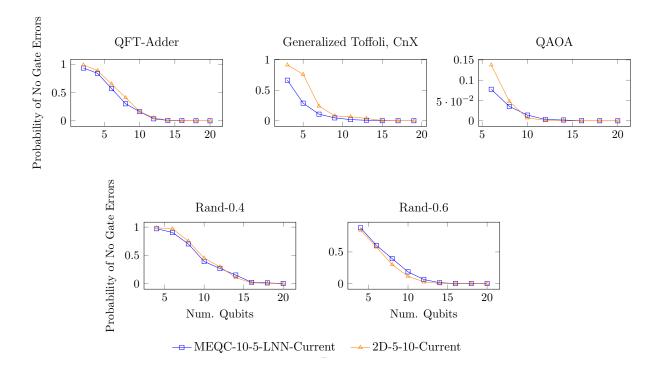

| 5.8 | An estimation of if no gate errors occur in small program instances. As noted,  |     |

|     | this only accounts for errors due to one and two qubit gate errors and is not   |     |

|     | influenced by decoherence errors. Larger is better and in general programs      |     |

|     | compiled to our proposed architecture are competitive or better than a 2D       |     |

|     | architecture. We expect with better T1 times and better gate and depth scaling, |     |

|     | our architecture will outperform, by increasing the likelihood or successful    |     |

|     | execution, by a larger margin as programs scale and gate errors improve. All    |     |

|     | data points were obtained by running 8000 trials of the input compiled input    |     |

|     | program                                                                         | 150 |

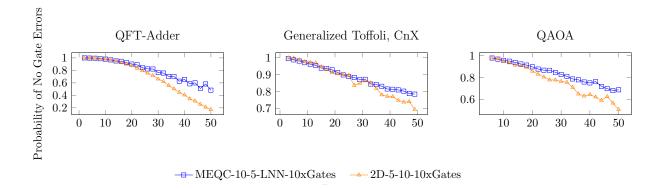

| 5.9 | With 100x better gates, we begin to see the effect of improved compilation.     |     |

|     | Specifically, by reducing the total number of gates required for execution on   |     |

|     | the proposed MEQC devices we reduce the probability of a program failing        |     |

|     | due to gate errors. Furthermore, with substantially longer T1 times in cavity,  |     |

|     | qubits stored in memory are protected from decoherence errors. All data points  |     |

|     | are obtained by running 8000 trials of the input program compiled to the two    |     |

|     | target architectures                                                            | 151 |

| 5.10 | Gates and depth of 20 qubit QFT Adder compiled to MEQC architectures with         |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | different transmon connectivity and varying cavity sizes. As the number of        |     |

|      | qubits per cavity increases, we expect the average qubit distance to be reduced   |     |

|      | meaning fewer SWAPs necessary. However, in MEQC devices operations on             |     |

|      | qubits in the same cavity cannot be done in parallel. Therefore, we expect        |     |

|      | lose some degree of parallelism, hence the increase in depth                      | 154 |

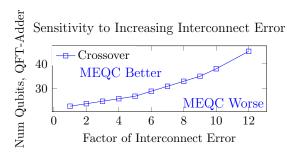

| 5.11 | Crossover points for various interconnect error rates of the QFT-Adder bench-     |     |

|      | mark. Interconnect in MEQC devices may not be as good as SWAPs in                 |     |

|      | traditional architectures. We study how much interconnect error we can toler-     |     |

|      | ate in the NISQ target of 100 qubit devices with $10^{-5}$ two qubit error rates. |     |

|      | We find we can tolerate up to 12x worse interconnect errors, provided programs    |     |

|      | of at least size 52                                                               | 155 |

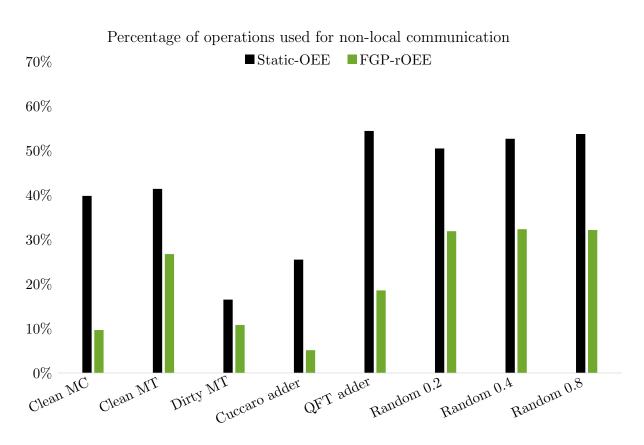

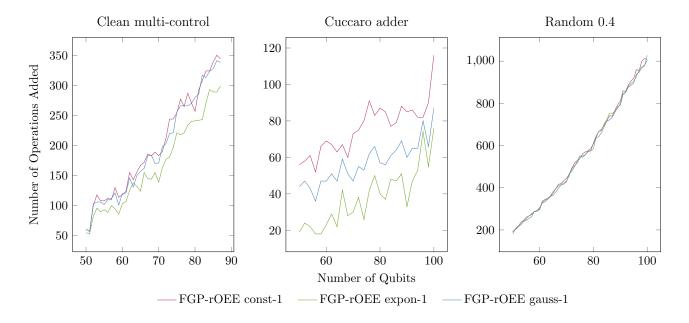

| 5.12 | Non-local communication overhead in circuits mapped to cluster-based ma-          |     |

|      | chines. Our new mapping scheme FPG-rOEE reduces the number of operations          |     |

|      | added for non-local communication on all benchmarks                               | 159 |

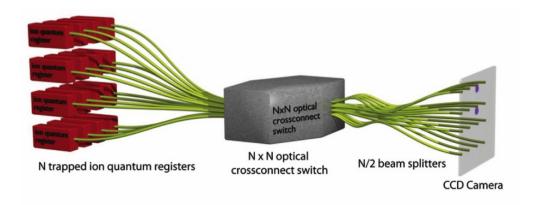

| 5.13 | An example modular architecture of qubits in individual ion traps connected       |     |

|      | with optics proposed by Monroe et al [132]. Communication between traps           |     |

|      | is supported by photon-mediated entanglement. Similar communication for           |     |

|      | superconducting qubits [40] can facilitate modular architectures for that tech-   |     |

|      | nology                                                                            | 160 |

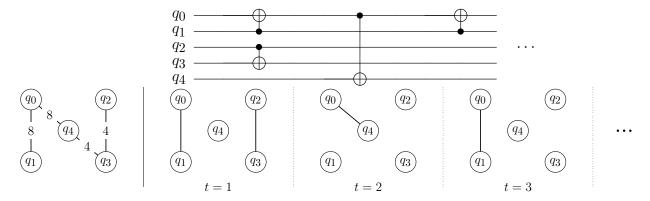

| 5.14 | (Top) An example of a quantum program with single-qubit gates not shown.            |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | The inputs are on the left and time flows to the right toward the outputs. The      |     |

|      | two-qubit operations here are CNOT (controlled-NOT). (Bottom) The graph             |     |

|      | representations of the quantum circuit of the above circuit. On the far left is     |     |

|      | the total interaction graph where each edge is weighted by the total number         |     |

|      | of interactions for the whole circuit. To the right is the sequence of time slice   |     |

|      | graphs, where an edge is only present if the qubits interact in the time slice.     |     |

|      | The sum of all time slice graphs is the total interaction graph                     | 161 |

| 5.15 | An example of a time slice graph with lookahead weights based on the circuit        |     |

|      | in Figure 5.14. We take the graph from the left and add weight to the edges         |     |

|      | of qubits that interact in the future. In this case, we take the weight equal to    |     |

|      | the number of times the qubits will interact in the future                          | 165 |

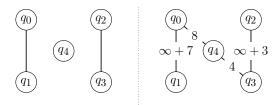

| 5.16 | The effect of different lookahead functions with various $\sigma$ on non-local com- |     |

|      | munication in the Cuccaro adder, a very regular circuit, with 76 data and 24        |     |

|      | ancilla qubits using FGP-rOEE. We see the exponential function outperforms          |     |

|      | the others for a circuit of highly regular structure                                | 168 |

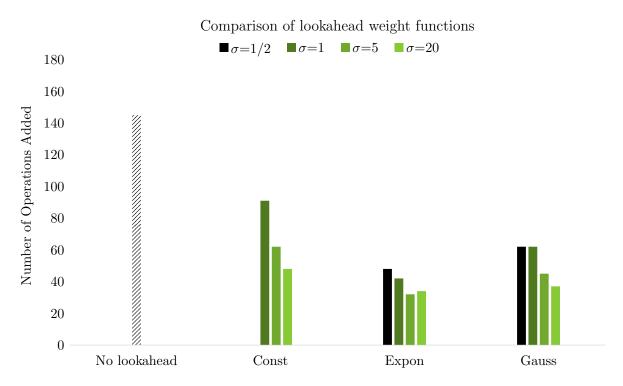

| 5.17 | The non-local communication, measured in number of operations between               |     |

|      | clusters added, for our representative benchmark circuits mapped by each            |     |

|      | FGP-rOEE using different lookahead functions, each with $\sigma=1$ . The x-axis     |     |

|      | is the number of input/output qubits. The remainder are used as ancilla for         |     |

|      | clean multi-control. The exponential function is better on all instances of         |     |

|      | Clean multi-control and Cuccaro adder, and there is no substantial advantage        |     |

|      | of one function over the others in the random circuit.                              | 169 |

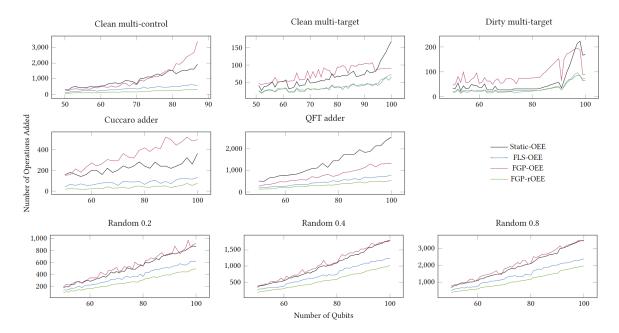

| 5.18 | The non-local communication overhead for our benchmark circuits mapped by           |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | each mapping algorithm. The x-axis is the number of qubits that are used in         |     |

|      | the circuit. The y-axis is the number of non-local communication operations         |     |

|      | inserted to make the circuit executable in our hardware model. In Clean             |     |

|      | multi-control, Clean multi-target, and Dirty multi-target, the remainder of the     |     |

|      | 100 qubits are used as ancilla (clean or dirty determined by the circuit name).     |     |

|      | FGP-rOEE outperforms all other mapping algorithms on all but the multi-             |     |

|      | target circuits, and shows substantial improvement over the static baseline.        |     |

|      | As the size of the circuit increases, rOEE tends to outperform by a greater         |     |

|      | margin, indicating scales better into the future                                    | 176 |

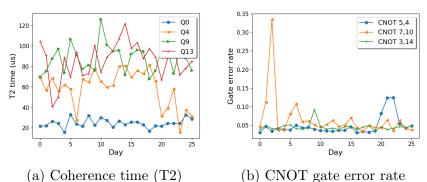

| 5.19 | Daily variations in qubit coherence time (larger is better) and gate error rates    |     |

|      | (lower is better) in IBMQ 16 Rueschlikon. The qubits and gates that are most        |     |

|      | or least reliable are different across days                                         | 180 |

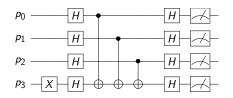

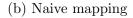

| 5.20 | Figure (a) shows the intermediate representation of the Bernstein-Vazirani          |     |

|      | algorithm on 4 qubits (BV4). Each qubit is represented by a line. X and             |     |

|      | H are single qubit gates. The CNOT gates from each qubit $p_{0,1,2}$ to $p_3$ are   |     |

|      | marked by vertical connectors. The measurement or readout operation is              |     |

|      | indicated by the meter. Figure (b) shows a mapping where qubit movement is          |     |

|      | required. The numbers on the labelled edges indicate the CNOT gate error            |     |

|      | $(\times 10^{-2})$ . In this mapping, an error-prone CNOT is used. Figure (c) shows |     |

|      | an optimized mapping where qubit movement is not required and unreliable            |     |

|      | hardware CNOTs (crossed) and unreliable qubits (hatched) are avoided                | 183 |

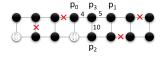

| 5.21 | Optimization Pipeline. Inputs are a QC program, details about the specific                                     |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

|      | hardware configuration, and a set of options, such as routing policy and solver                                |     |

|      | approach. From these, compiler generates a set of appropriate constraints and                                  |     |

|      | uses them to map program qubits to hardware qubits and schedule operations.                                    |     |

|      | Finally, the compiler generates an executable version of the program, here for                                 |     |

|      | <i>IBMQ16</i>                                                                                                  | 184 |

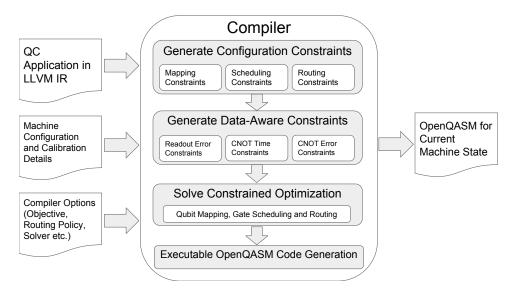

| 5.22 | Two routing policies for swap-based architectures                                                              | 191 |

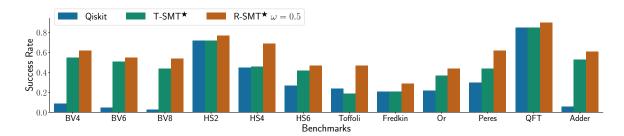

| 5.23 | Measured success rate of R-SMT★<br>compared to Qiskit and T-SMT★. (Of 8192                                     |     |

|      | trials per execution, success rate is the percentage that achieve the correct                                  |     |

|      | answer in real-system execution. R-SMT $^{\bigstar}$ obtains higher success rate than                          |     |

|      | Qiskit because it simultaneously adapts placement according to dynamic error                                   |     |

|      | rates and avoids unnecessary qubit movement                                                                    | 198 |

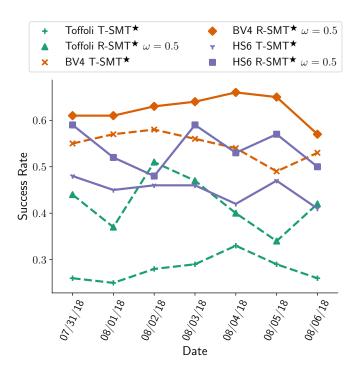

| 5.24 | Executions of three benchmarks for 1 week. R-SMT $\bigstar$ is more resilient to errors                        |     |

|      | compared to T-SMT $\stackrel{\bigstar}{.}$ . Similar trends for other benchmarks                               | 199 |

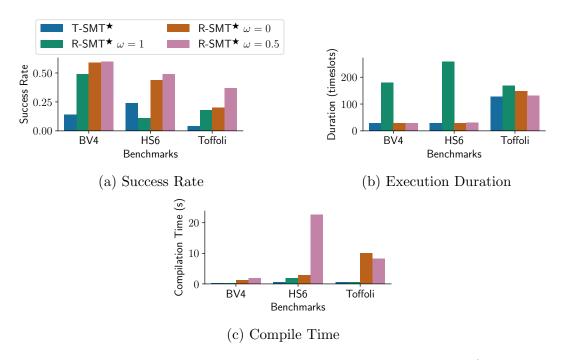

| 5.25 | Measured success rate, execution duration and compile time for three represen-                                 |     |

|      | tative benchmarks. T-SMT $\stackrel{\bigstar}{\bigstar}$ which directly optimizes for execution duration       |     |

|      | obtains the minimum execution durations, but R-SMT $\stackrel{\bigstar}{\bigstar}$ with $\omega=0.5$ is close, |     |

|      | and more resilient to errors (higher reliability). All benchmarks compile in less                              |     |

|      | than 1 minute                                                                                                  | 200 |

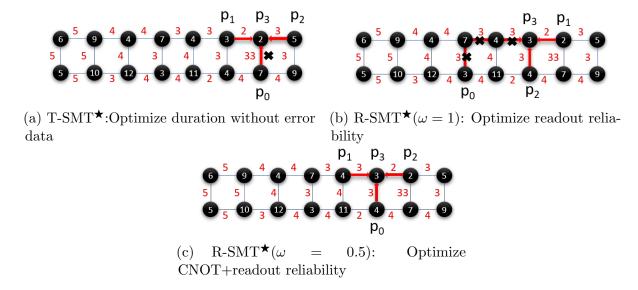

| 5.26 | For real data/experiment, on $\mathit{IBMQ16}$ , qubit mappings for three optimization                         |     |

|      | objectives, varying the type of noise-awareness. In each figure, the edge labels                               |     |

|      | indicate the CNOT gate error rate ( $\times 10^{-2}$ ), and the numbers inside each                            |     |

|      | node indicate that qubit's readout error rate ( $\times 10^{-2}$ ). (a), T-SMT $\bigstar$ uses an              |     |

|      | unreliable hardware CNOT between $p_3$ and $p_0$ . (b) Program qubits are placed                               |     |

|      | on the best readout qubits, but $p_0$ and $p_3$ communicate using swaps. (c) Best                              |     |

|      | CNOTs and readout qubits are used                                                                              | 201 |

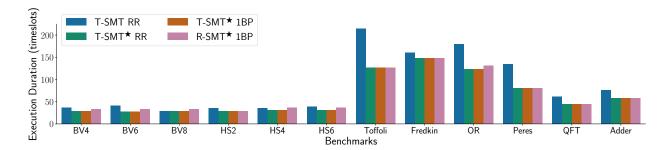

| 5.27 | Effect of gate durations, routing policy and objective function on execution                |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | duration. Although reliability is our primary objective, several variants perform           |     |

|      | well on run time as well. T-SMT $\bigstar$ (either RR or OBP) has the best execution        |     |

|      | duration, but R-SMT $\bigstar$ is very close in run time and offers better success rates.   |     |

|      | Noise-aware policies, R-SMT $\bigstar$ and T-SMT $\bigstar$ , are 1.6x better than T-SMT    | 202 |

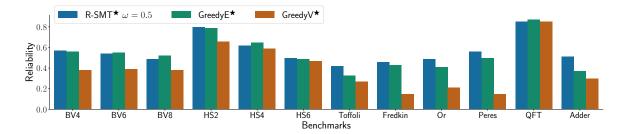

| 5.28 | Noise-aware Heuristics: Greedy<br>E $^\bigstar$ heuristic mapping offers reliability compa- |     |

|      | rable to R-SMT★on most benchmarks                                                           | 203 |

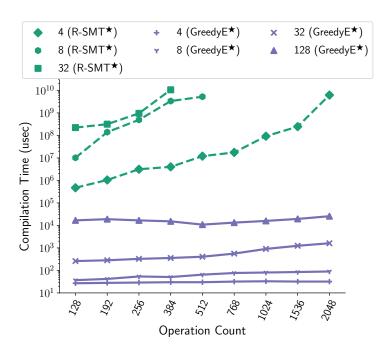

| 5.29 | Scalability of optimal and heuristic methods on synthetic benchmarks. Each                  |     |

|      | line represents a qubit count.                                                              | 204 |

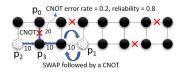

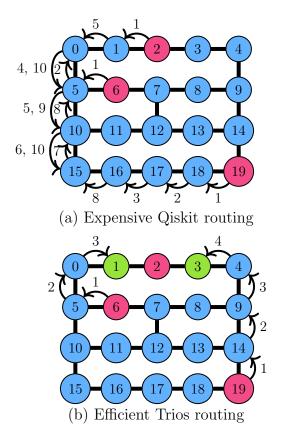

| 5.30 | Example routing from Qiskit (a) vs. Trios (b) for a single Toffoli operation.               |     |

|      | Circles represent qubits and lines indicate two qubits are connected. Input                 |     |

|      | qubits are highlighted in red. SWAP arrows are labeled by timestep. The                     |     |

|      | routed locations for Trios routing are highlighted in green while Qiskit moves              |     |

|      | them several times. Qiskit adds 16 SWAPs (=48 CNOTs), some during the                       |     |

|      | Toffoli, while Trios adds only 7 SWAPs (=21 CNOTs) all before the Toffoli.                  |     |

|      | Performing multiple passes of decomposition allows direct routing and enables               |     |

|      | this huge reduction in communication, increasing the probability of program                 |     |

|      | success                                                                                     | 207 |

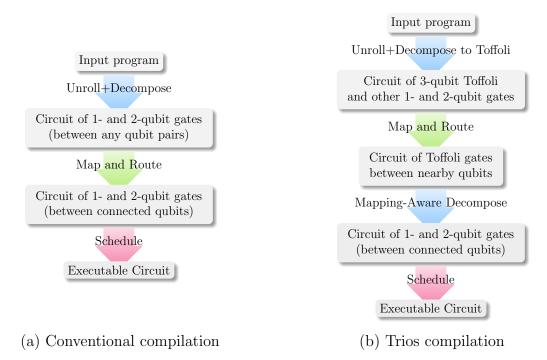

| 5.31 | (a) Typical compilation passes used by Qiskit (simplified). (b) Trios compila-              |     |

|      | tion passes                                                                                 | 209 |

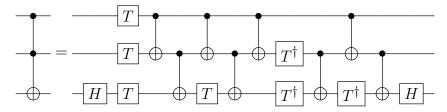

| 5.32 | A 6-CNOT decomposition of the Toffoli gate                                                  | 211 |

| 5 33 | An 8-CNOT decomposition of the Toffoli gate                                                 | 211 |

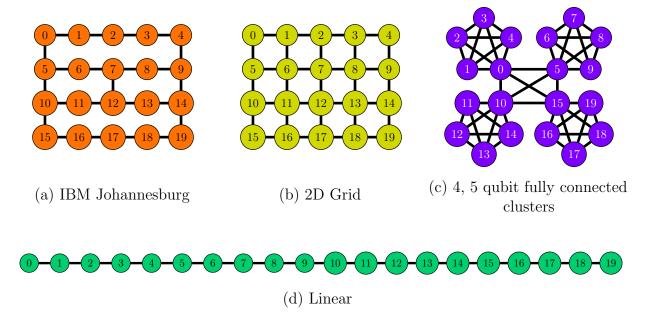

| 5.34 | Example topologies of near-term quantum devices. Orange (a): IBM Johan-                  |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | nesburg. Yellow (b): 2D Grid. Purple (c): four groups of five fully connected            |     |

|      | clusters. Green (d) Linear. Our real experiments run on Johannesburg and                 |     |

|      | our simulations explore all of these topologies. Colors correspond with the              |     |

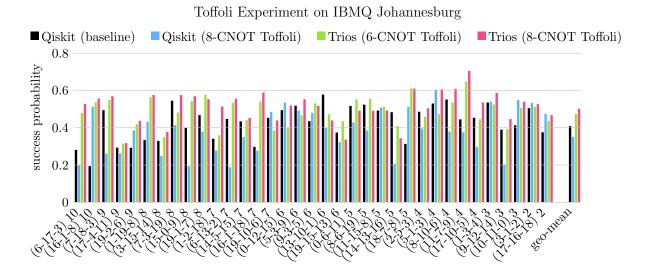

|      | bars in Figures 5.38, 5.39, 5.40                                                         | 212 |

| 5.35 | Success probabilities of Toffoli gates between random triplets of qubits. Higher         |     |

|      | is better. The x labels specify the three qubits and total swap distance. The            |     |

|      | geometric mean success rates for each compiler are $41\%$ , $35\%$ , $47\%$ , and $50\%$ |     |

|      | respectively. Trios (8-CNOT) improves average success rate by $23\%$ vs. the             |     |

|      | Qiskit baseline                                                                          | 219 |

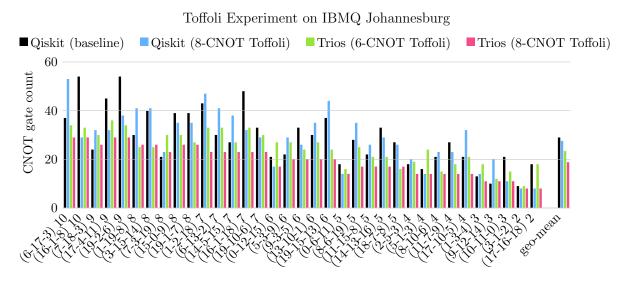

| 5.36 | Total number of two-qubit (CNOT) gates required to execute a Toffoli gate                |     |

|      | between various distant qubits. Lower is better. The x labels specify the three          |     |

|      | qubits and total swap distance. The geometric mean gate counts for each                  |     |

|      | compiler are 29, 28, 23, and 19 respectively. Trios (8-CNOT) reduces average             |     |

|      | gate count by 35%                                                                        | 219 |

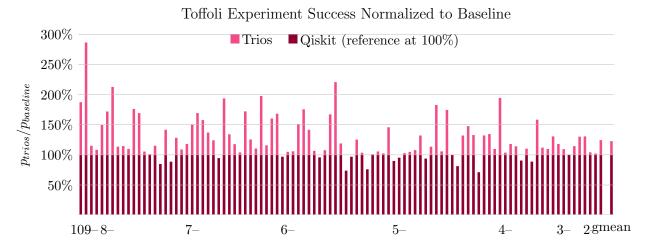

| 5.37 | Normalized success probabilities of Toffoli gates between triplets of qubits.            |     |

|      | Higher is better. Bars below $100\%$ indicate lower success rate for Trios. The          |     |

|      | geometric mean increase in success rate is 23%. The x labels indicate the qubit          |     |

|      | distance for a range of bars                                                             | 220 |

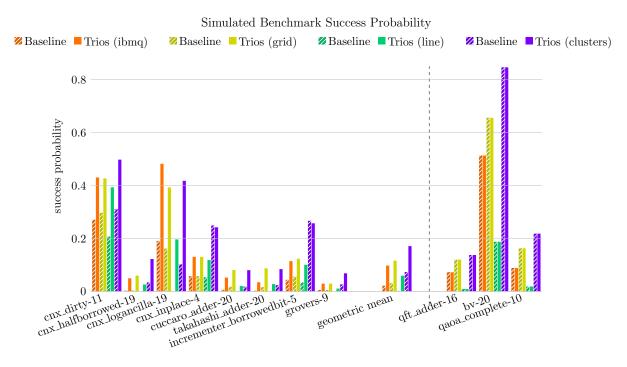

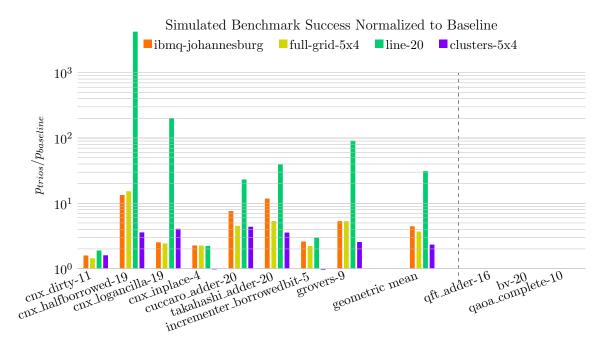

| 5.38 | Simulated upper-bounds on the program execution success probability on                                                    |     |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

|      | various hardware (using 20x lower idle and gate errors than Johannesburg).                                                |     |

|      | Neighboring pairs of bars compare the baseline with Trios compiled for Johan-                                             |     |

|      | nesburg. Higher is better when comparing pairs of bars with the same color.                                               |     |

|      | The geometric mean success rates over the benchmarks that use Toffoli gate                                                |     |

|      | for each device type respectively are $2.2\% \rightarrow 9.8\%$ , $3.2\% \rightarrow 12\%$ , $0.19\% \rightarrow 6.0\%$ , |     |

|      | $7.3\% \rightarrow 17\%$ . The rightmost three benchmarks contain zero Toffoli gates so                                   |     |

|      | have no change vs. the baseline                                                                                           | 220 |

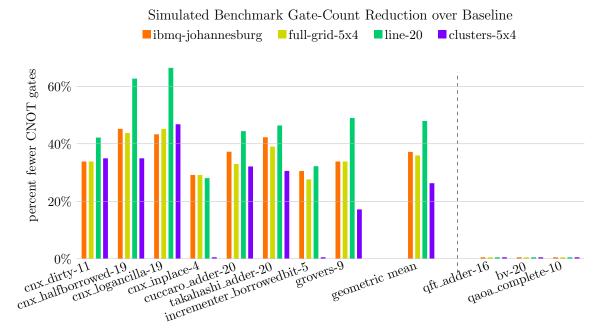

| 5.39 | A comparison between the baseline and Trios for various hardware. Above $0\%$                                             |     |

|      | indicates benefit. All two-qubit gates (for communication and computation)                                                |     |

|      | are counted. The geometric mean reductions in gate counts are 37%, 36%,                                                   |     |

|      | 48%, and 26% respectively. The rightmost three benchmarks contain zero                                                    |     |

|      | Toffoli gates so have no change vs. the baseline                                                                          | 221 |

| 5.40 | Normalized Figure 5.38 to show our consistent increase in program success with                                            |     |

|      | Trios. Above $10^0$ indicates benefit. Some improvement factors are huge due to                                           |     |

|      | near-zero baseline success rates. The geometric mean increases in success rate                                            |     |

|      | are 4.4x, 3.7x, 31x, and 2.3x respectively. The rightmost three benchmarks                                                |     |

|      | contain zero Toffoli gates so have no change vs. the baseline                                                             | 222 |

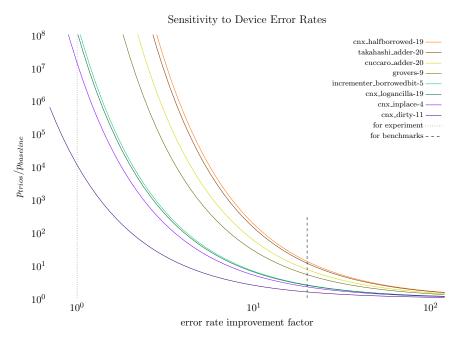

| 5.41 | Factor of improvement in success rate in Trios over baseline for scaling gate                                             |     |

|      | error rates. The dotted line indicates current error rates on IBM Johannesburg                                            |     |

|      | and the dashed line (20x improvement) indicates values of the near future used                                            |     |

|      | in simulation. In our approximation of success rate factors of improvement in                                             |     |

|      | gate error rates lead to an exponential fall off in success ratios, as expected.                                          |     |

|      | In the very near term, we expect Trios to drastically improve the execution of                                            |     |

|      | quantum programs                                                                                                          | 223 |

# LIST OF TABLES

| 2.1 | Asymptotic comparison of $N$ -controlled gate decompositions. The total gate                 |     |

|-----|----------------------------------------------------------------------------------------------|-----|

|     | count for all circuits scales linearly (except for Barenco [15], which scales                |     |

|     | quadratically). Our construction uses qutrits to achieve logarithmic depth                   |     |

|     | without ancilla. We benchmark our circuit construction against Gidney [70],                  |     |

|     | which is the asymptotically best ancilla-free qubit circuit                                  | 14  |

| 2.2 | Truth table for taking two input carry statuses $C_0 = (c_{0,0}c_{0,1})$ and $C_1 =$         |     |

|     | $(c_{1,0}c_{1,1})$ , encoded as in the left table of Figure 2.8 and outputting the resulting |     |

|     | combined carry status $C'_1 = (c'_{1,0}c'_{1,1})$ while dirtying the bits of $C_0$ based on  |     |

|     | the desired behavior of the right table of Figure 2.8. For example, consider                 |     |

|     | the third to last row of the table. The bitstring is (1101) indicating the first             |     |

|     | carry status is generate (g) and the second carry status is propagate (p). The               |     |

|     | means we want to output generate $g = (11)$ on the last two bits but we don't                |     |

|     | care what happens to the first two bits, as we've done here, leaving them in                 |     |

|     | ternary states, specifically $ 2\rangle  2\rangle$                                           | 20  |

| 2.3 | Carry status encoding scheme for the $+K$ adder circuit                                      | 23  |

| 2.4 | Noise models simulated for superconducting devices                                           | 34  |

| 2.5 | Noise models simulated for trapped ion devices                                               | 35  |

| 2.6 | Truth table for 2-3-1 Compression                                                            | 39  |

| 2.7 | Truth table for 2-4-1 Compression                                                            | 40  |

| 4.1 | Starting point coherence times and constant gate times for the hardware models.              | 116 |

| 4.2 | Transmon, depth-10 cavity, and total qubit costs of each T-state generation                  |     |

|     | protocol for $d = 5$                                                                         | 120 |

| 5.1 | Benchmarks and some of their properties                                                      | 139 |

| 5.2 | Error model details for current systems [92, 141]                                            | 139 |

| 5.3 | Summary of the improvements on 50 qubit benchmarks for MEQC-10-5-2D                       |       |

|-----|-------------------------------------------------------------------------------------------|-------|

|     | over 2D-5-10. In all cases, we see strict improvement                                     | 149   |

| 5.4 | A subset of our benchmarks. Clean multi-control has a maximum size of 87.                 |       |

|     | With more than 87 data qubits and fewer than 13 clean ancilla, the depth                  |       |

|     | of the multi-control decomposition is too large to run on these cluster-based             |       |

|     | machines with predicted error rates                                                       | 170   |

| 5.5 | Comparing Static-OEE against FGP-rOEE over all benchmarked instances.                     |       |

|     | We obtain improvement across the board with the worst case still reducing                 |       |

|     | non-local communication by 22.6%                                                          | 177   |

| 5.6 | Estimated execution time of the clean multi-control benchmark with 76 data                |       |

|     | qubits and 24 ancilla. Two-qubit gates take 300ns [92] and the multiplier                 |       |

|     | indicates how many times longer non-local communication operations take                   | 177   |

| 5.7 | List of compiler configurations used in our study. The IBM Qiskit 0.5.7                   |       |

|     | compiler is used as a the baseline. The use of calibration data is marked by a $\bigstar$ | ·.185 |

| 5.8 | Characteristics of benchmark programs                                                     | 196   |

| 5.9 | Details about benchmarks for Trios for reference, both NISQ programs and                  |       |

|     | other quantum subroutines                                                                 | 218   |

## **ACKNOWLEDGMENTS**

First and foremost I want to thank my advisor Fred Chong for all of his guidance through my PhD. I'd also like my committee Hank Hoffmann, Ken Brown, and Ali Javadi-Abhari all of whom have been valuable collaborators and mentors. I'd like to also thank all of my collaborators with special thanks to several of my frequent collaborators - Prakash Murali, Pranav Gokhale, Gokul Ravi, Kaitlin Smith, Sophia Lin, Andrew Litteken, Alex Hoover, and most of all Casey Duckering. I am grateful for each of my collaborators beyond those here, without which none of this work would have ever been completed.

I'd also like to thank everyone else along the way that's supported me - academically, emotionally, or otherwise. This includes all of the people I've met in EPiQC and the University of Chicago and more, too many to list here. Finally I'd like to thank my family without which I'd never have gotten anywhere close to this point.

## ABSTRACT