## THE UNIVERSITY OF CHICAGO

# NEW ABSTRACTIONS FOR QUANTUM COMPUTING

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF COMPUTER SCIENCE

BY

CASEY DUCKERING

CHICAGO, ILLINOIS

DECEMBER 2022

Copyright  $\bigodot$  2022 by Casey Duckering All Rights Reserved

# TABLE OF CONTENTS

| LIS | ST O    | F FIGURES                                                                  | ⁄i            |

|-----|---------|----------------------------------------------------------------------------|---------------|

| LIS | ST O    | F TABLES                                                                   | ii            |

| AC  | CKNC    | OWLEDGMENTS                                                                | ii            |

| ΑF  | BSTR    | ACT xi                                                                     | v             |

| 1   | INT     | RODUCTION                                                                  | 1             |

| 2   | BEY 2.1 |                                                                            | 5<br>5        |

|     | 2.2 2.3 | Background                                                                 | 9<br>3        |

|     | 2.0     |                                                                            | 3             |

|     | 2.4     | Circuit Construction                                                       | 6             |

|     |         | 2.4.1 Key Intuition                                                        | 6<br>7        |

|     | 2.5     |                                                                            | 9             |

|     |         | 2.5.2 Incrementer                                                          | -             |

|     | 2.6     | 2.5.4 Error Correction and Fault Tolerance                                 | $\frac{1}{2}$ |

|     | 2.0     | 2.6.1 Noise Simulation                                                     | 3             |

|     | 2.7     | Noise Models                                                               |               |

|     |         | 2.7.1 Generic Noise Model       2         2.7.2 Superconducting QC       2 |               |

|     | 2.8     | 2.7.3 Trapped Ion <sup>171</sup> Yb <sup>+</sup> QC                        | 0             |

|     | 2.9     | Qubit-Qudit Compression                                                    | 5<br>7        |

|     | 0.10    | 2.9.2 Qubit to Ququart Compression                                         | 8             |

|     | 2.10    |                                                                            | 4             |

|     | 2.11    | 2.10.2 +K Adder                                                            | 5<br>6        |

| 3 | SPA | TIALLY LOCAL MEMORY                                      | 8 |

|---|-----|----------------------------------------------------------|---|

|   | 3.1 | Introduction                                             | 8 |

|   | 3.2 | Background                                               | 2 |

|   |     | 3.2.1 Basics of Quantum Computing                        | 2 |

|   |     | 3.2.2 Superconducting Qubit Architectures                | 3 |

|   |     | 3.2.3 Qubit Memory Technology                            | 3 |

|   |     | 3.2.4 Quantum Errors                                     | 5 |

|   |     | 3.2.5 Surface Codes, Error Decoding, and Lattice Surgery | 6 |

|   | 3.3 | Virtualized Logical Qubits                               | 9 |

|   |     | 3.3.1 Natural Surface Code Embedding                     | 0 |

|   |     | 3.3.2 Transversal CNOT                                   | 3 |

|   |     | 3.3.3 Compact Surface Code Embedding                     | 4 |

|   |     | 3.3.4 Architectural Considerations                       | 8 |

|   | 3.4 | Evaluation                                               | 0 |

|   |     | 3.4.1 Error Model and Noise Assumptions                  |   |

|   |     | 3.4.2 Experimental Setup                                 |   |

|   | 3.5 | Error Threshold Results                                  |   |

|   | 3.6 | Error Sensitivity Results                                |   |

|   | 3.7 | Magic State Distillation Resource Estimates              |   |

|   | 3.8 | Summary                                                  |   |

|   |     |                                                          |   |

| 4 | HIE | RARCHICAL PROGRAM STRUCTURE                              | 1 |

|   | 4.1 | Introduction                                             | 1 |

|   | 4.2 | Background                                               | 6 |

|   |     | 4.2.1 Quantum Computing Basics                           | 6 |

|   |     | 4.2.2 Quantum Circuits                                   | 6 |

|   |     | 4.2.3 Current Quantum Devices                            | 8 |

|   |     | 4.2.4 The Compilation Problem                            | 0 |

|   |     | 4.2.5 Evaluation Metrics                                 | 1 |

|   |     | 4.2.6 Simulation                                         | 2 |

|   | 4.3 | Motivation: Conventional Compilation                     | 2 |

|   | 4.4 | Orchestrated Trios                                       | 4 |

|   | 4.5 | Evaluation                                               | 6 |

|   |     | 4.5.1 Toffoli Only Circuits                              | 6 |

|   |     | 4.5.2 NISQ Benchmarks and Quantum Subroutines            | 7 |

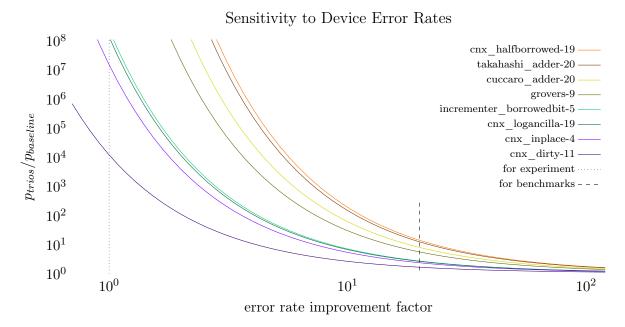

|   | 4.6 | Results and Discussion                                   | 9 |

|   |     | 4.6.1 Trios Reduces Total Number of Gates                | 9 |

|   |     | 4.6.2 Trios Improves Overall Success Rate                |   |

|   |     | 4.6.3 Trios Routes Complex Interactions Better           |   |

|   |     | 4.6.4 Simulation Sensitivity to Error Rates              |   |

|   | 4.7 | Summary                                                  |   |

| 5  | CON  | ICLUSI | ON           |             |       | <br> |      | <br> | <br> |  |  | 108 |

|----|------|--------|--------------|-------------|-------|------|------|------|------|--|--|-----|

|    | 5.1  | Future | Abstractions |             |       | <br> | <br> | <br> | <br> |  |  | 108 |

|    |      | 5.1.1  | Programmer   | Abstraction | ns    | <br> | <br> | <br> | <br> |  |  | 108 |

|    |      | 5.1.2  | Intermediate | Representa  | tions | <br> | <br> | <br> | <br> |  |  | 110 |

|    | 5.2  | Outloo | k            |             |       | <br> |      | <br> | <br> |  |  | 112 |

| RI | EFER | ENCES  | 5            |             |       | <br> | <br> | <br> | <br> |  |  | 113 |

# LIST OF FIGURES

| 2.1 | Reversible AND circuit using a single ancilla bit. The inputs are on the left, and time flows rightward to the outputs. This AND gate is implemented using a Toffoli (CCNOT) gate with inputs $q_0$ , $q_1$ and a single ancilla initialized to 0. At                                                                        |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | the end of the circuit, $q_0$ and $q_1$ are preserved, and the ancilla bit is set to 1 if and only if both other inputs are 1                                                                                                                                                                                                | 10  |

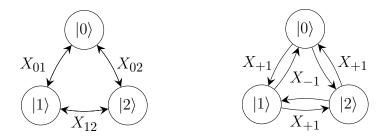

| 2.2 | The five nontrivial permutations on the basis elements for a qutrit. (Left) Each operation here switches two basis elements while leaving the third unchanged. These operations are self-inverses. (Right) These two operations permute the three basis elements by performing a $+1 \mod 3$ and $-1 \mod 3$ operation. They |     |

|     | are each other's inverses                                                                                                                                                                                                                                                                                                    | 12  |

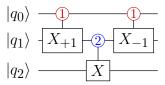

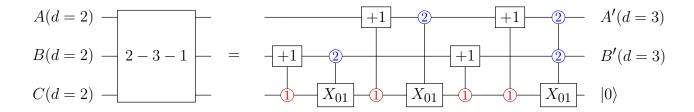

| 2.3 | A Toffoli decomposition via qutrits. Each input and output is a qubit. The red controls activate on $ 1\rangle$ and the blue controls activate on $ 2\rangle$ . The first gate                                                                                                                                               |     |

|     | temporarily elevates $q_1$ to $ 2\rangle$ if both $q_0$ and $q_1$ were $ 1\rangle$ . We then perform the qubit-X operation only if $q_1$ is $ 2\rangle$ . The final gate restores $q_1$ to its original state.                                                                                                               | 17  |

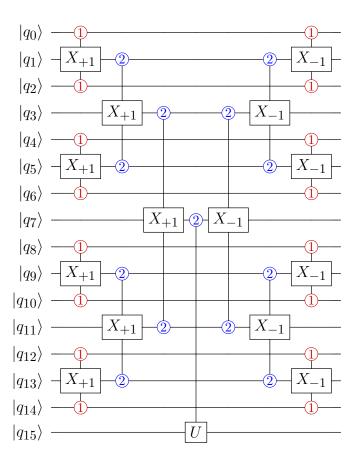

| 2.4 | Our circuit decomposition for the Generalized Toffoli gate is shown for 15 controls and 1 target. The inputs and outputs are both qubits, but we allow occupation                                                                                                                                                            | 11  |

|     | of the $ 2\rangle$ qutrit state in between. The circuit has a tree structure and maintains the property that the root of each subtree can only be elevated to $ 2\rangle$ if all of its control leaves were $ 1\rangle$ . Thus, the $U$ gate is only executed if all controls                                                |     |

|     | are $ 1\rangle$ . The right half of the circuit performs uncomputation to restore the controls to their original state. This construction applies more generally to any                                                                                                                                                      |     |

|     | multiply-controlled $U$ gate. Note that the three-input gates are decomposed into                                                                                                                                                                                                                                            |     |

|     | 6 two-input and 7 single-input gates in our actual simulation, as based on the                                                                                                                                                                                                                                               |     |

|     | decomposition in Di and Wei [2011]                                                                                                                                                                                                                                                                                           | 18  |

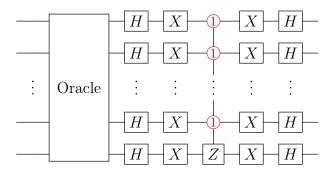

| 2.5 | Each iteration of Grover Search has a multiply-controlled $Z$ gate. Our logarithmic                                                                                                                                                                                                                                          |     |

|     | depth decomposition, reduces a $\log M$ factor in Grover's algorithm to $\log \log M$ .                                                                                                                                                                                                                                      | 20  |

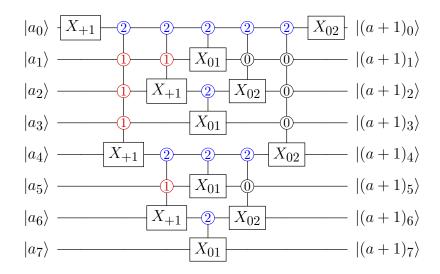

| 2.6 | Our circuit decomposition for the Incrementer. At each subcircuit in the recursive                                                                                                                                                                                                                                           |     |

|     | design, multiply-controlled gates are used to efficiently propagate carries over half                                                                                                                                                                                                                                        |     |

|     | of the subcircuit. The $ 2\rangle$ control checks for carry generation and the chain of $ 1\rangle$ controls checks for carry propagation. The circuit depth is $\log^2 N$ , which is only                                                                                                                                   |     |

|     | possible because of our log depth multiply-controlled gate primitive                                                                                                                                                                                                                                                         | 21  |

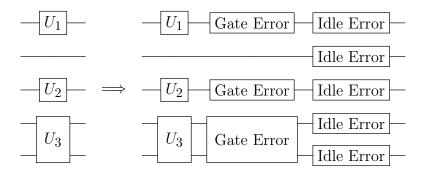

| 2.7 | This Moment comprises three gates executed in parallel. To simulate with noise, we                                                                                                                                                                                                                                           | 41  |

| 2   | first apply the ideal gates, followed by a gate error noise channel on each affected                                                                                                                                                                                                                                         |     |

|     | qudit. This gate error noise channel depends on whether the corresponding gate                                                                                                                                                                                                                                               |     |

|     | was single- or two-qudit. Finally, we apply an idle error to every qudit. The idle                                                                                                                                                                                                                                           |     |

|     | error noise channel depends on the duration of the $Moment$                                                                                                                                                                                                                                                                  | 24  |

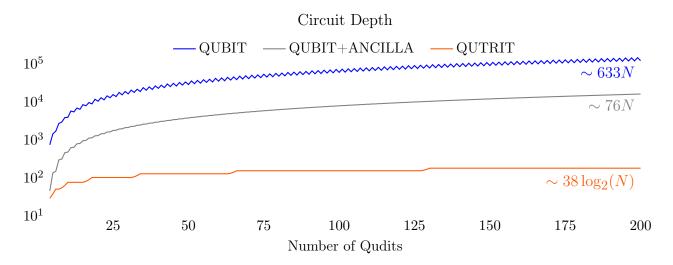

| 2.8 | Exact circuit depths for all three benchmarked circuit constructions for the N-                                                                                                                                                                                                                                              |     |

|     | controlled Generalized Toffoli up to $N = 200$ . Both QUBIT and QUBIT+ANCILLA                                                                                                                                                                                                                                                | 0.0 |

| 0.0 | scale linearly in depth and both are bested by QUTRIT's logarithmic depth                                                                                                                                                                                                                                                    | 32  |

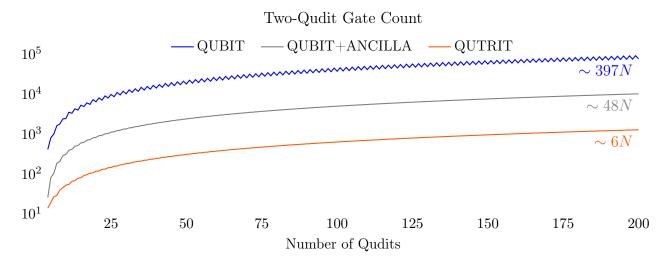

| 2.9 | Exact two-qudit gate counts for the three benchmarked circuit constructions for                                                                                                                                                                                                                                              |     |

|     | the N-controlled Generalized Toffoli. All three plots scale linearly; however the QUTRIT construction has a substantially lower linearity constant                                                                                                                                                                           | 33  |

|     | & 11.11 Constitution has a substantiany lower infeatity constant                                                                                                                                                                                                                                                             | oo  |

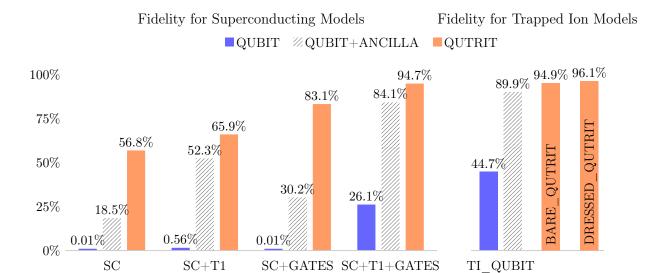

| 2.10 | Circuit simulation results for all possible pairs of circuit constructions and noise models. Each bar represents $1000+$ trials, so the error bars are all $2\sigma < 0.1\%$ . Our QUTRIT construction significantly outperforms the QUBIT construction. The QUBIT+ANCILLA bars are drawn with dashed lines to emphasize that it                                                                                                                                                                                                                                                                                                                                                                             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | has access to an extra ancilla bit, unlike our construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34 |

| 2.12 | the inverse of this circuit using <i>any</i> ancilla for the third qubit The compression of 2 qubits into a single ququart and generating an ancilla, $ 0\rangle$ . The +2 gate here is done modulo 4. This operation takes as input two qubits, A and B, and produces a single ququart and an ancilla $ 0\rangle$ . To do this, we need only 3 two-ququart gates. Similarly, to retrieve the stored information, we can                                                                                                                                                                                                                                                                                     | 38 |

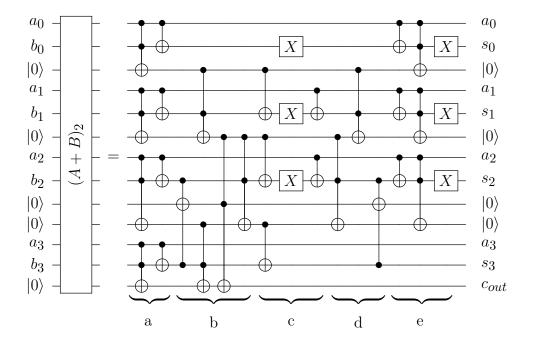

| 2.13 | do the inverse of this operation using $any$ ancilla for the second qubit An adder circuit from Draper et al. [2006] on two four-bit registers $A$ and $B$ with a carry-out bit using ancilla. The sum $S$ is computed in-place on register $B$ while $A$ is untouched and the ancilla are restored to $ 0\rangle$ . We use this as a sub-component of our general decomposition. Each of the ancilla in this circuit                                                                                                                                                                                                                                                                                        | 39 |

| 2.14 | can be generated from other input qubits not shown here via our compression circuits. Part a of the circuit computes carry, generate, and propagate for each bit position. Part b computes the carry-in for every bit position. Part c does the addition, storing the output in register $B$ . Parts d and e uncompute b and a respectively, restoring the ancilla back to $ 0\rangle$                                                                                                                                                                                                                                                                                                                       | 41 |

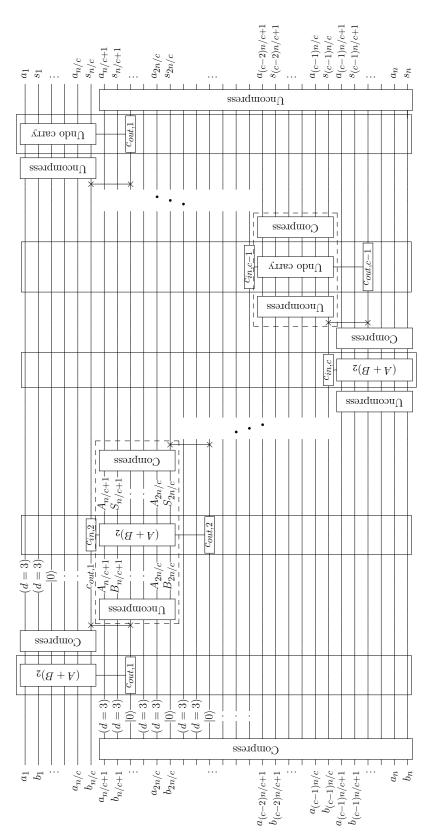

|      | drawn around every $(A+B)_2$ and Undo carry gate to indicate that they use all the generated ancilla across the circuit. $c_{out,i}$ or $c_{in,i}$ is included on some of the gates to indicate when the carry-in and carry-out versions are used and on which ancilla the carry-out is stored. The SWAP gates (pairs of $\times$ in the diagram) simply move a carry-out bit to another ancilla where it is used as the next carry-in. The two blocks of gates shown with dashed lines are repeated $c-2=3$ times along the diagonal indicated. If 2-4-1 compression is used, an ancilla is generated for every two unused qubits so only $c=4$ blocks are needed. The depth of this circuit is $O(\log n)$ | 42 |

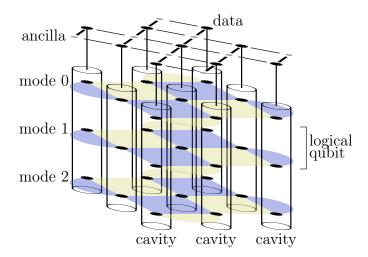

| 3.1  | Our fault-tolerant architecture with random-access memory local to each transmon. On top is the typical 2D grid of transmon qubits. Attached below each data transmon is a resonant cavity storing error-prone data qubits (shown as black circles). This pattern is tiled in 2D to obtain a 2.5D array of logical qubits. Our key innovation here is storing the qubits that make up each logical qubit (shown as checkerboards) across many cavities to enable efficient computation.                                                                                                                                                                                                                      | 50 |

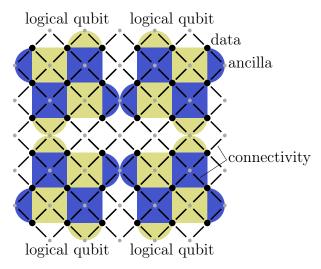

| 3.2 | A typical 2D superconducting qubit architecture. The dots are transmon qubits where black are used as data and gray are used as ancilla for error correction. The                                                                              |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | lines indicate physical connections between qubits that allow operations between                                                                                                                                                               |     |

|     | them. Four logical qubits, each consisting of 9 error-prone data qubits, are shown                                                                                                                                                             |     |

|     | here in the rotated surface code with distance 3. Z parity checks are shaded                                                                                                                                                                   |     |

|     | yellow (light) and X parity checks are shaded blue (dark) where checks on only 2                                                                                                                                                               |     |

|     | data are drawn as half circles                                                                                                                                                                                                                 | 54  |

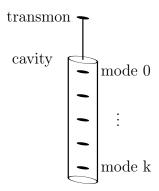

| 3.3 | A close-up representation of the qubit memory technology we use. On top is<br>a superconducting transmon qubit physically connected to a resonant supercon-<br>ducting cavity. This cavity has many resonant modes each used to store a qubit. |     |

|     | These qubits can be loaded and stored (with random access) via the transmon.                                                                                                                                                                   | 55  |

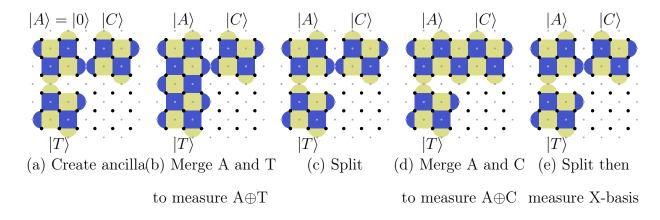

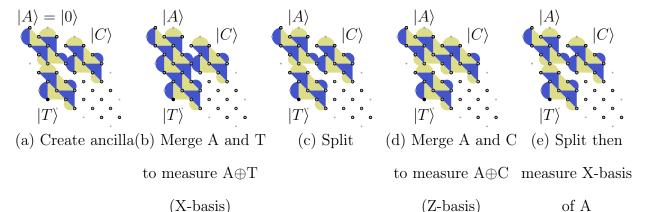

| 3.4 | The lattice surgery operations to perform a logical CNOT on the standard surface                                                                                                                                                               | 00  |

| 0.1 | code (and directly supported in our architecture). Given control and target qubits                                                                                                                                                             |     |

|     | $ C\rangle$ and $ T\rangle$ , a CNOT is performed by enabling and disabling the parity checks                                                                                                                                                  |     |

|     | as shown across 6 timesteps ((e) is two steps). We show this complex process to                                                                                                                                                                |     |

|     | contrast with the fast transversal CNOT enabled by our architecture (described                                                                                                                                                                 |     |

|     | later in Section 3.3.2).                                                                                                                                                                                                                       | 57  |

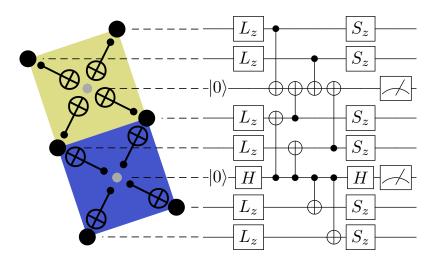

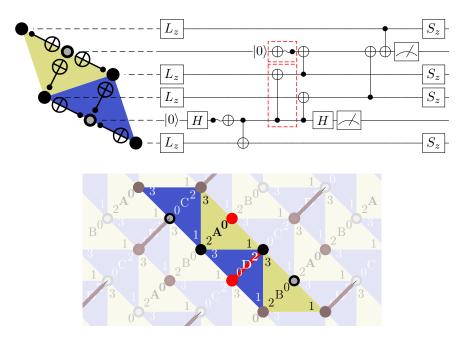

| 3.5 | Circuit showing how to execute our Natural embedding on hardware. Left: The                                                                                                                                                                    |     |

|     | layout of six data (black) and two ancilla (gray) in hardware. CNOT operations                                                                                                                                                                 |     |

|     | between qubits are drawn between. Right: A circuit diagram of the operations                                                                                                                                                                   |     |

|     | applied over time where each horizontal line corresponds to a qubit and each box                                                                                                                                                               |     |

|     | or symbol is an operation. The steps are $L_z$ : load from memory mode $z$ , $ 0\rangle$ :                                                                                                                                                     |     |

|     | reset ancilla, CNOTs: compute the Z or X parity, Meter: measure the result, $S_z$ :                                                                                                                                                            | 00  |

| 2.6 | store back to memory.                                                                                                                                                                                                                          | 62  |

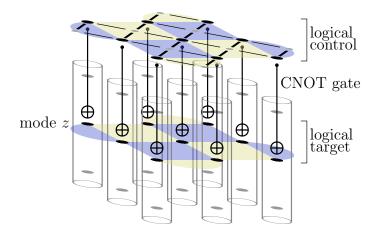

| 3.6 | The transversal CNOT enabled by our 2.5D architecture. The data qubits for the control logical qubit are loaded into the transmons. Transmon-mediated CNOTs to mode $z$ for every data qubit perform the logical operation. This takes one     |     |

|     | timestep to perform, 6x better than a lattice surgery CNOT                                                                                                                                                                                     | 63  |

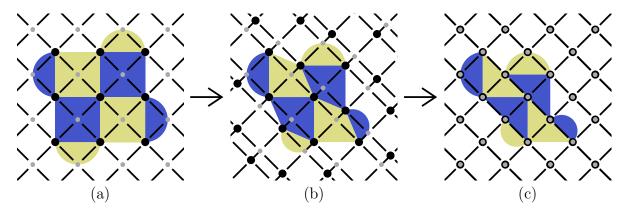

| 3.7 | Transformation from Natural to Compact. (a) Natural embedding: Only data                                                                                                                                                                       |     |

|     | have attached cavities (not shown). (b) The transformation: Z ancilla (over                                                                                                                                                                    |     |

|     | yellow/light areas) merge with the upper-right data transmon and X ancilla (over                                                                                                                                                               |     |

|     | blue/dark areas) merge with the lower-left data transmon. The opposite parings                                                                                                                                                                 |     |

|     | are key to keeping 4-way grid connectivity. (c) Compact embedding: All ancilla                                                                                                                                                                 |     |

|     | transmons without attached cavities have been removed. All remaining transmons                                                                                                                                                                 |     |

|     | have cavities and are used as both data and ancilla.                                                                                                                                                                                           | 65  |

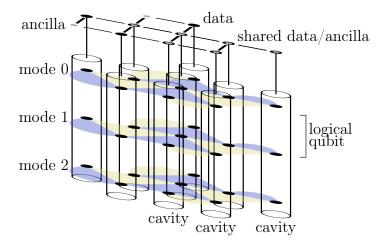

| 3.8 | A 3D view of our Compact embedding. Shown at the top is the 2D grid of                                                                                                                                                                         |     |

|     | transmon qubits. Attached below every transmon is a resonant cavity. Compact                                                                                                                                                                   |     |

|     | surface code patches are shown stored, one in each mode. This deformed patch                                                                                                                                                                   | 0.0 |

|     | can be tiled in 2D                                                                                                                                                                                                                             | 66  |

| 3.9        | The Compact lattice surgery operations to perform a CNOT. The logical operations performed are identical to Figure 3.4 but the corresponding physical operations are arranged as shown in Figure 3.7. This uses half as many transmons as Natural. As before, it takes 6 timesteps of $d$ error correction cycles                                                                                           |          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.10       | each                                                                                                                                                                                                                                                                                                                                                                                                        | 67       |

|            | showing the hardware operations over time. Bottom: The CNOT execution order repeats $A_0D_2$ , $A_1D_3$ , $A_2C_0$ , $A_3C_1$ , $B_0C_2$ , $B_1C_3$ , $B_2D_0$ , $B_3D_1$ . The $AB$ and $CD$ sequences run in parallel but offset to ensure ancilla and data use do not conflict. CNOTs for $A_0D_2$ are marked in red where an isolated circle indicates a transmon-                                      |          |

|            | mediated CNOT                                                                                                                                                                                                                                                                                                                                                                                               | 67       |

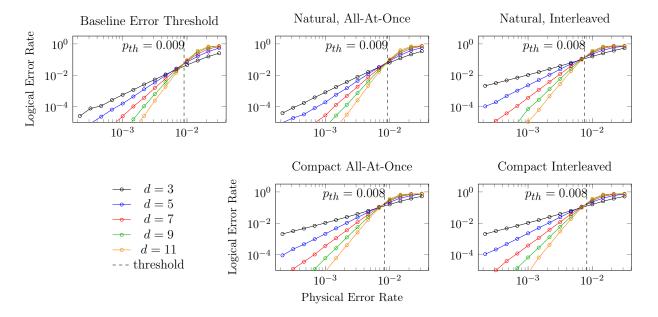

| 3.11       | Error thresholds for the baseline 2D architecture and Natural and Compact variants of our 2.5D architecture. The thresholds are comparable to the baseline indicating the space savings obtained in our system does not substantially reduce                                                                                                                                                                |          |

|            | the error thresholds. The slopes of the lines in this figure indicate, post-threshold, how much improvement in physical error rates improve logical error rate. Except                                                                                                                                                                                                                                      |          |

| 2 10       | for the baseline, all use a cavity size of 10                                                                                                                                                                                                                                                                                                                                                               | 74       |

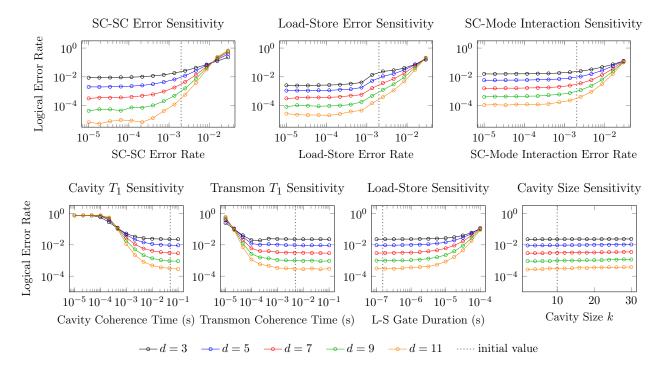

| 3.12       | Sensitivity of logical error rate to various error sources in Compact, Interleaved. The logical error rates are most sensitive to physical error of Loads/Stores and SC-SC gates. The logical error rate is less sensitive to the coherence times and                                                                                                                                                       |          |

|            | mostly insensitive to effects of load-store duration and cavity size                                                                                                                                                                                                                                                                                                                                        | 76       |

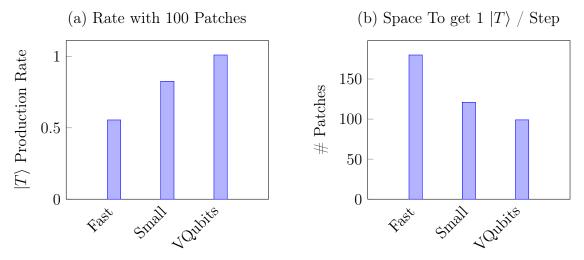

| 3.13       | is better. (b) The space, in terms of number of patches, required to produce a single $ T\rangle$ per time step. Lower is better. Fast Litinski [2019a] and Small Litinski [2019b] work in the surface code and do not use memory. VQubits is implemented                                                                                                                                                   |          |

|            | with transversal CNOTs in our 2.5D architecture. All are based on Bravyi and Haah [2012]                                                                                                                                                                                                                                                                                                                    | 77       |

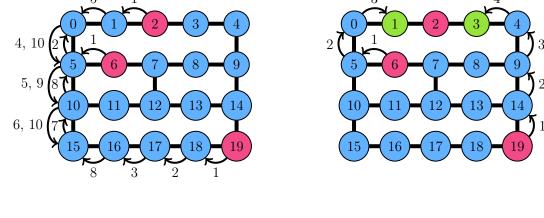

| 4.1        | Example routing from Qiskit (a) vs. Trios (b) for a single Toffoli operation. Circles represent qubits and lines indicate two qubits are connected. Input qubits are highlighted in red. SWAP arrows are labeled by timestep. The routed locations for Trios routing are highlighted in green while Qiskit moves them several times. Qiskit adds 16 SWAPs (=48 CNOTs), some during the Toffoli, while Trios |          |

|            | adds only 7 SWAPs (=21 CNOTs) all before the Toffoli. Performing multiple passes of decomposition allows direct routing and enables this huge reduction in                                                                                                                                                                                                                                                  | 00       |

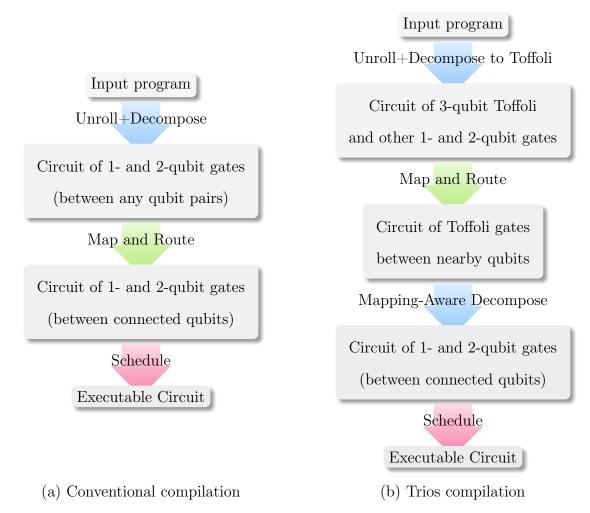

| 4.2        | communication, increasing the probability of program success                                                                                                                                                                                                                                                                                                                                                | 82       |

| <b>-</b>   | tion passes. The Unroll+Decompose pass is split into two parts: decompose into medium-size operations (Toffoli gates), later finish decomposition, but using                                                                                                                                                                                                                                                |          |

| 4.0        | information from the Map and Route pass                                                                                                                                                                                                                                                                                                                                                                     | 83       |

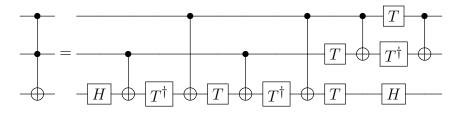

| 4.3<br>4.4 | The common 6-CNOT decomposition of the Toffoli gate                                                                                                                                                                                                                                                                                                                                                         | 88<br>88 |

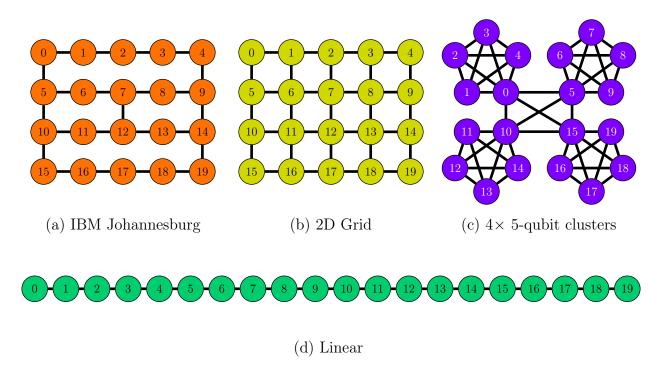

| 4.5  | Example topologies of near-term quantum devices. Orange (a): IBM Johannesburg. Yellow (b): 2D Grid. Purple (c): four groups of five fully connected         |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | clusters. Green (d) Linear. Our real experiments run on Johannesburg and our                                                                                |     |

|      | simulations explore all of these topologies. Colors correspond with the bars in                                                                             |     |

|      | Figures 4.9, 4.10, and 4.11                                                                                                                                 | 89  |

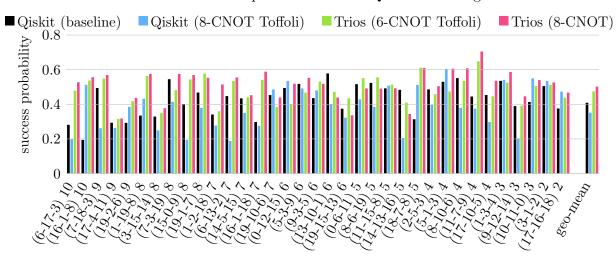

| 4.6  | Success probabilities of Toffoli gates between random triplets of qubits. Higher                                                                            |     |

|      | is better. The x-labels specify the three qubits and total swap distance. The                                                                               |     |

|      | geometric mean success rates for each compiler are 41%, 35%, 47%, and 50%                                                                                   |     |

|      | respectively. Trios (8-CNOT) improves average success rate by 23% vs. the Qiskit                                                                            |     |

|      | baseline                                                                                                                                                    | 101 |

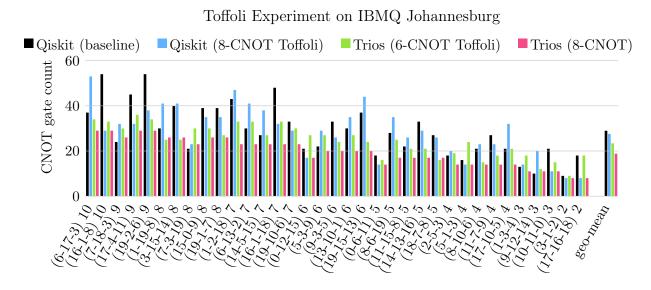

| 4.7  | Total number of two-qubit (CNOT) gates required to execute a Toffoli gate be-                                                                               |     |

|      | tween various distant qubits. Lower is better. The x-labels specify the three                                                                               |     |

|      | qubits and total swap distance. The geometric mean gate counts for each com-                                                                                |     |

|      | piler are 29, 28, 23, and 19 respectively. Trios (8-CNOT) reduces average gate count by 35%                                                                 | 101 |

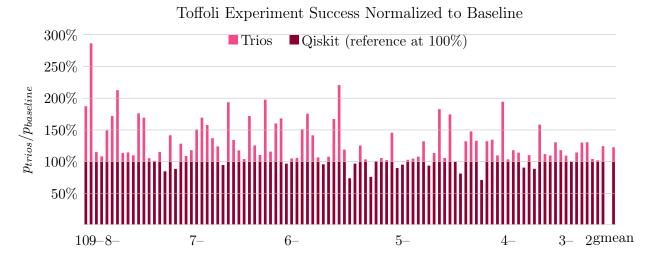

| 4.8  | Normalized success probabilities of Toffoli gates between triplets of qubits. Higher                                                                        | 101 |

| 4.0  | is better. Bars below 100% indicate lower success rate for Trios. The geometric                                                                             |     |

|      | mean increase in success rate is 23%. The x-labels indicate the qubit distance for                                                                          |     |

|      | a range of bars.                                                                                                                                            | 102 |

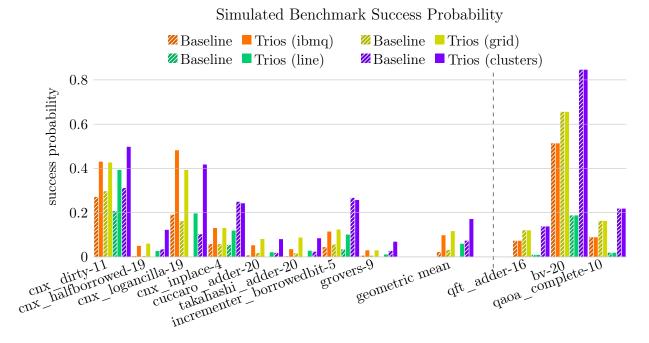

| 4.9  | Simulated upper-bounds on the program execution success probability on various                                                                              |     |

|      | hardware (using 20x lower idle and gate errors than Johannesburg). Neighboring                                                                              |     |

|      | pairs of bars compare the baseline with Trios compiled for Johannesburg. Higher                                                                             |     |

|      | is better when comparing pairs of bars with the same color. The geometric                                                                                   |     |

|      | mean success rates over the benchmarks that use Toffoli gate for each device                                                                                |     |

|      | type respectively are $2.2\% \to 9.8\%$ , $3.2\% \to 12\%$ , $0.19\% \to 6.0\%$ , $7.3\% \to 17\%$ . The                                                    |     |

|      | rightmost three benchmarks contain zero Toffoli gates so have no change vs. the                                                                             | 104 |

| 1 10 | baseline.                                                                                                                                                   | 104 |

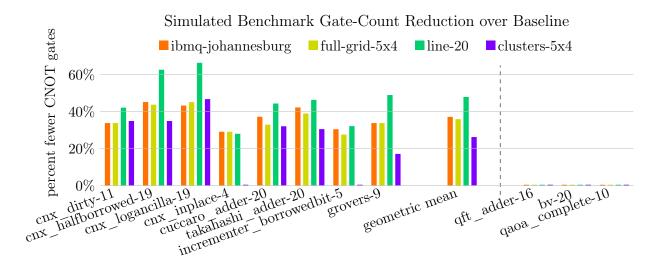

| 4.10 | A comparison between the baseline and Trios for various hardware. Above 0%                                                                                  |     |

|      | indicates benefit. All two-qubit gates (for communication and computation) are counted. The geometric mean reductions in gate counts are 37%, 36%, 48%, and |     |

|      | 26% respectively. The rightmost three benchmarks contain zero Toffoli gates so                                                                              |     |

|      | have no change vs. the baseline                                                                                                                             | 105 |

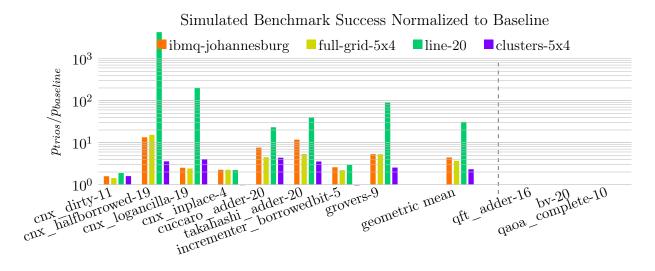

| 4.11 | Normalized Figure 4.9 to show our consistent increase in program success with                                                                               | 100 |

|      | Trios. Above $10^0$ indicates benefit. Some improvement factors are huge due to                                                                             |     |

|      | near-zero baseline success rates. The geometric mean increases in success rate are                                                                          |     |

|      | 4.4x, 3.7x, 31x, and 2.3x respectively. The rightmost three benchmarks contain                                                                              |     |

|      | zero Toffoli gates so have no change vs. the baseline                                                                                                       | 105 |

# LIST OF TABLES

| 2.1 | Asymptotic comparison of <i>n</i> -controlled gate decompositions. The total gate                                                                               |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | count for all circuits scales linearly (except for Barenco et al. [1995], which scales                                                                          |    |

|     | quadratically). Our construction uses qutrits to achieve logarithmic depth with-                                                                                |    |

|     | out ancilla. We benchmark our circuit construction against Gidney [2015], which                                                                                 |    |

|     | is the asymptotically best ancilla-free qubit circuit                                                                                                           | 15 |

| 2.2 | Noise models simulated for superconducting devices. Current publicly accessible                                                                                 |    |

|     | IBM superconducting quantum computers have single- and two-qubit gate errors                                                                                    |    |

|     | of $3p_1 \approx 10^{-3}$ and $15p_2 \approx 10^{-2}$ , as well as $T_1$ lifetimes of 0.1 ms (IBM Devices,                                                      |    |

|     | Linke et al. [2017]). Our baseline benchmark, SC, assumes 10x better gate errors                                                                                |    |

|     | and $T_1$ . The other three benchmarks add a further 10x improvement to $T_1$ , gate                                                                            | 20 |

| 0.2 | Noise models simulated for transpol ion devices. The simulator two sutait sets                                                                                  | 30 |

| 2.3 | Noise models simulated for trapped ion devices. The single- and two-qutrit gate error channel probabilities are based on calculations from experimental parame- |    |

|     | ters. For all three models, we use single- and two-qudit gate times of $\Delta t \approx 1 \ \mu s$                                                             |    |

|     | and $\Delta t \approx 200 \ \mu s$ respectively                                                                                                                 | 31 |

| 2.4 | Truth table for 2-3-1 Compression                                                                                                                               | 37 |

| 2.5 | Truth table for 2-4-1 Compression                                                                                                                               | 39 |

| 2.0 | iradii daole for 2 11 compression                                                                                                                               | 00 |

| 3.1 | Starting point coherence times and constant gate times for the hardware models.                                                                                 | 72 |

| 3.2 | Transmon, depth-10 cavity, and total qubit costs of each T-state generation pro-                                                                                |    |

|     | to col for $d = 5$                                                                                                                                              | 79 |

| 4.1 | Details about our benchmarks both NISQ programs and other quantum sub-                                                                                          |    |

| 1.1 | routines. We consider circuits with and without Toffoli gates where we expect                                                                                   |    |

|     | advantage only for circuits containing Toffoli gates. For BV we assume the all                                                                                  |    |

|     | 1-bit string. The different CnX (many-controlled-NOT) gates use various num-                                                                                    |    |

|     | bers of ancilla. *The total number of CNOT gates is after decomposition with                                                                                    |    |

|     | the 8-CNOT Toffoli but does not including any SWAPs for routing                                                                                                 | 98 |

|     |                                                                                                                                                                 |    |

## ACKNOWLEDGMENTS

I would like to thank my advisor, Fred Chong, for his constant mentorship and support throughout my PhD. Thanks also to my dissertation committee members Hank Hoffman and Ken Brown for their time and valuable feedback on my systems and error correction ideas. I am grateful to Craig Gidney at my summer internships for teaching me all his quantum tricks that have served me well during my PhD.

None of this research would exist without the friendship, collaboration, and casual conversations with my research group and other co-authors: Adam, Adrian, Alex, Andrew, Ben, Claire, Dan, David, Gokul, Hele, Jonathan, Josh, Kartik, Kate, Kunal, Max, Natalie, Pranav, Reza, Rohan, Ryan, Siddharth, Sophia, Soumik, Yongshan, and Yunong. All the friends I've made during my time in Chicago, especially everyone at Tea Time, the Ministry, and Team Beer, have made my time in Chicago worthwhile. Finally, thanks to my family for their love and support.

This research is funded in part by EPiQC, an NSF Expedition in Computing, under grants CCF-1730449/1832377; in part by STAQ, under grant NSF Phy-1818914; in part by DOE grants DE-SC0020289 and DE-SC0020331; and in part by NSF OMA-2016136 and the Q-NEXT DOE NQI Center. This research used resources of the Oak Ridge Leadership Computing Facility, which is a DOE Office of Science User Facility supported under Contract DE-AC05-00OR22725. Disclosure: F. Chong is also Chief Scientist for Quantum Software at ColdQuanta and an advisor to Quantum Circuits, Inc.

# **ABSTRACT**

The field of quantum computing is at an exciting time where we are constructing novel hardware, evaluating algorithms, and finding out what works best. As qubit technology grows and matures, we need to be ready to design and program larger quantum computer systems. An important aspect of systems design is layered abstractions to reduce complexity and guide intuition. Classical computer systems have built up many abstractions over their history including the layers of the hardware stack and programming abstractions like loops. Researchers initially ported these abstractions with little modification when designing quantum computer systems and only in recent years have some of those abstractions been broken in the name of optimization and efficiency.

We argue that new or quantum-tailored abstractions are needed to get the most benefit out of quantum computer systems. We keep the benefits gained through breaking old abstraction by finding abstractions aligned with quantum physics and the technology. This dissertation is supported by three examples of abstractions that could become a core part of how we design and program quantum computers: third-level logical state as scratch space, memory as a third spacial dimension for quantum data, and hierarchical program structure.

## CHAPTER 1

## INTRODUCTION

Moore's Law and the expectation that computers double in speed every 18 months is at an end, so hard problems in chemistry, physics simulation, and combinatorial optimization cannot be solved by waiting for a faster computer. Since the end of Moore's Law, researchers have been developing special-purpose accelerators to squeeze better performance out of each transistor. However once fully realized, quantum computers can solve specific classes of problems in simulation and cryptography exponentially faster.

Quantum computers work by harnessing quantum physics instead of classical Newtonian physics. Because quantum physics is a superset of classical physics, we often treat quantum computers as classical computers with the additional features of *superposition*, *entanglement*, and *interference*. This view is apparent in Shor's algorithm (Shor [1997]) which creates a quantum superposition, followed by classical arithmetic, and finishes with quantum phase estimation.

Seeing quantum programming through a classical lens can be limiting and sometimes harmful. It is common for programmers who are new to quantum to invent a "quantum algorithm" that is simply a randomized classical algorithm run on a quantum computer, using quantum measurements as random number generators. More subtly, concepts such as binary representation of data, random access memory, and hierarchical modularity of programs when used in the design of quantum computers limit the performance due to mismatches with the underlying technology. Even classical concepts of causality and movement of data can be limiting; quantum teleportation, a quantum protocol described in Nielsen and Chuang [2011], moves quantum data long distances by pre-transferring another resource before the data exists.

When we design quantum architectures and compilers, the abstractions we use are key to a good design. The abstraction of two-level *bits* is very beneficial for classical computer

reliability but is yet to be decided for quantum. Early classical computers used base-10 addresses and arithmetic until early computer architects settled on binary as the most efficient and reliable design. This history informs the general assumption that binary (base-2) is best for quantum computers, but that is not necessarily the case. We discuss this further in Chapter 2.

Because quantum computing is a rapidly developing field with many competing technologies there is no clear "best" for any use case. Each quantum technology has capabilities and constraints that inform a variety of hardware designs and architectures that show how to turn a qubit technology into a practical quantum computer. The principles of abstraction and modularity we use to build any complex system still apply when we design a quantum computer hardware layout, instruction set, compiler, and programming language, but we must tailor the abstractions to best fit the physics and the technology or we will limit future efficiency.

This dissertation presents three cases of new or old abstractions that we have tailored for quantum computing. We discuss the methodologies to select these abstractions and how we use them with a particular class of quantum architectures. We show that good abstractions can allow more space efficient algorithms and more effective compilers.

This dissertation is comprised of three core papers introducing three abstractions covered in the following chapters. Additional content from other work is included that shows further benefits and refinement to the abstractions. We start in Chapter 2 by introducing three-level quantum trits and other d-level quantum dits: Asymptotic Improvements to Quantum Circuits via Quantum Circuits, Gokhale et al. [2019] and Efficient Quantum Circuit Decompositions via Intermediate Qudits, Baker et al. [2020a]. These abstractions replace and augment the use of binary qubits with three-level quarits or d-level qudits, but require us to completely rethink how algorithms and compilers allocate and use scratch space. Most quantum technologies can reliably support three or more quantum states with minor changes to the control signal design

and no change to the hardware design. Supported technologies include superconducting transmon, ion trap, and neutral atom, but notably not some types of photonic qubits.

Chapter 3 considers abstractions that spatially separate quantum data storage or memory from computation on that data: Virtualized Logical Qubits: A 2.5D Architecture for Error-Corrected Quantum Computing, Duckering et al. [2020]. Classical computers contain high speed buses that can transfer data between memory (RAM) and computation (CPU), but this extreme separation of memory from compute does not make sense either for current small (NISQ) or for future (fault-tolerant) quantum computers. The typical abstraction for both kinds is a monolithic 2D array of qubits because NISQ computers cannot sacrifice the data-parallelism and fault-tolerance requires constant error correction to prevent errors. Compiler design is simple in this monolithic model because there is no heterogeneity; compilers can place related data nearby in the plane. But we compare an alternative to the monolithic model. We redesign the surface code to use small amounts of distributed memory and find that it improves the space efficiency of fault-tolerant algorithms.

Classical programmers have used a hierarchy of function calls and modules in the design of a program to great effect. Hierarchy gives structure to what would otherwise be a very long list of primitive instructions. Compilers use this structure to guide optimizations and to avoid duplicate work of repeated components. However, quantum programmers currently trend toward highly hand-optimized programs with no hierarchy; they use optimization passes that erase any hierarchy and perform flat, program-wide optimizations. Chapter 4 introduces Orchestrated Trios: Compiling for Efficient Communication in Quantum Programs with 3-Qubit Gates, Duckering et al. [2021], to show that hierarchy can guide quantum compiler heuristics even for small- to mid-size programs. Program hierarchy enables sequences of compiler passes to repeat for each level, improving heuristic performance and allowing new kinds of passes like our connectivity-aware split pass. This is key for quantum where data locality constraints restrict data movement and can inform program structure.

Picking the right abstractions are crucial for quantum programming, compiling, and execution. Chapter 5 concludes with a discussion and other places where we still need better abstractions.

## CHAPTER 2

#### **BEYOND BINARY**

#### 2.1 Introduction

Recent advances in both hardware and software for quantum computation have demonstrated significant progress towards practical outcomes. While early research efforts focused on longer-term systems employing full error correction to execute large programs for algorithms like Shor [1997] and Grover [1996], recent work has focused on NISQ (Noisy Intermediate Scale Quantum, Preskill [2018]) computation. The NISQ regime considers near-term machines with just tens to hundreds of quantum bits (qubits) and moderate errors.

In the NISQ regime, quantum programs rely directly on the individual qubits in the quantum device and severe resource constraints prohibit the use of error correction. Given the severe constraints on quantum resources, it is critical to fully optimize the compilation of a quantum program in order to have successful computation. Prior architectural research on techniques such as mapping, scheduling, and parallelism (Ding et al. [2018], Javadi-Abhari et al. [2017], Guerreschi and Park [2018]) have helped to extend the amount of useful computation possible, but without error correction, programs are exposed to noise and errors in their qubits. On the flip side, programs in the NISQ regime can directly take advantage of typically unused technology capabilities.

This chapter shows how to greatly reduce resource requirements by replacing the binary abstraction required by two-level qubits with a new abstraction enabled by three-level qutrits or multi-level qudits. Qutrits and qudits are natural features of technologies in the NISQ regime, which we evaluate, but the takeaways from this chapter may require further research to apply in an error-corrected setting.

While quantum computation is typically expressed as a two-level binary abstraction of qubits, the underlying physics of quantum systems are not intrinsically binary. Whereas

classical computers operate in binary states at the physical level (e.g. clipping above and below a threshold voltage), quantum computers have natural access to an infinite spectrum of discrete energy levels. In fact, hardware must actively suppress higher level states in order to achieve the two-level qubit approximation. Hence, using three-level qutrits is simply a choice of including an additional discrete energy level, albeit at the cost of more opportunities for error.

Prior work on qutrits (or more generally, d-level qudits) identified only constant factor gains from extending beyond qubits. In general, the prior work Pavlidis and Floratos [2017] has emphasized the information compression advantages of qutrits. For example, N qubits can be expressed in base-3 ternary as  $\frac{N}{\log_2(3)}$  qutrits, which leads to  $\log_2(3) \approx 1.6$ -constant factor improvements in space and runtime.

This chapter evaluates the benefits of a novel abstraction that uses qutrits in a novel fashion. We use the first two states as usual to represent computed values in binary but use the third state as temporary storage when needed. The per-operation error rate of qutrit operations is higher but the runtime (i.e. circuit depth or critical path) is asymptotically faster, and the overall reliability of computations is improved due to the novel temporary storage. Moreover, this abstraction only applies qutrit operations in an intermediary stage: the input and output are still qubits, which is important for initialization and measurement on real devices (Randall et al. [2015, 2018]) and reduces the burden to transition to the new abstraction.

We consider the benefits of different applications of this temporary qutrit abstraction. The first application we consider is a novel implementation of the generalized Toffoli circuit by Gokhale et al. [2019], a subroutine used in many quantum algorithms. By cleverly storing intermediate computations in the unused third state of input qubits, our implementation avoids the use of costly additional temporary qubits (called ancilla), but it achieves the speed of the fastest implementations that require many ancilla qubits.

In contrast, we also consider potential automated uses of temporary qutrits. The hand-designed generalized Toffoli implementation makes excellent use of one additional logical state and, while hand-optimization can be a good way to squeeze performance out of resource-constrained devices, codifying manual strategies into our compilers can have wider performance benefit and free most programmers to think at a higher level. By intelligently "compressing" the data in groups of idle qubits into smaller groups of qutrits as in Baker et al.  $[2020a]^1$  (using the  $\log_2(3)$  compression ratio) or qudits ( $\log_2(d)$  ratio), similar benefits for resource-constrained quantum computers can be achieved for a wider range of quantum programs.

The main benefit of compression is to produce ancilla, specifically clean ancilla, generated locally during the compilation of an algorithm into a quantum circuit. That is, we propose a new circuit which performs qubit-qudit compression storing the information of many qubits as a small number of qudits at the cost of some gate overhead. These compression circuits produce clean ancilla in the  $|0\rangle$  state. The stored data can be retrieved later when needed since all quantum operations are reversible (this is technically a re-encoding, not compression). Essentially, when certain groups of qubits will be unused for a long period of time, we can repurpose them by compressing them and using the produced ancilla. This "compression" is a rearrangement of the stored binary values into higher states, letting us store more information into the same number of physical quantum devices and free up qubits for computation. We evaluate this compression strategy in the design of an improved quantum adder circuit.

The key result of this chapter is that use of this abstraction by quantum subroutines or compilers extends the frontier of what limited-size quantum computers can compute. In particular, the frontier is defined by the zone in which every machine qubit is a data qubit,

<sup>1.</sup> CD's contributions to the works that comprise this chapter, Gokhale et al. [2019] and Baker et al. [2020a], include the novel circuit designs (in addition to contributions from PG and JMB for the ancilla-free Generalized Toffoli and with equal contributions from JB for all others), the qudit circuit implementations, numerical simulations, validation, and simulation results.

for example a 100-qubit program running on a 100-qubit machine. In this frontier zone, we do not have room for non-data workspace qubits known as ancilla. The lack of ancilla in the frontier zone is a costly constraint that generally leads to inefficient circuits. For this reason, typical circuits instead operate well below the frontier zone, with many machine qubits used as ancilla. This chapter demonstrates that ancilla can be substituted with qutrits, enabling us to operate efficiently within the ancilla-free frontier zone.

We highlight the primary contributions of this chapter:

- 1. A circuit construction for the generalized Toffoli subroutine that uses temporary qutrits and no ancilla qubits. This is an asymptotically faster circuit ( $633N \rightarrow 38 \log_2 N$ ) than equivalent qubit-only ancilla-free constructions.

- 2. Qutrit and qudit "compression" circuit designs.

- 3. A circuit construction for arithmetic addition in binary using qudit compression and no ancilla qubits.

- 4. An open-source qudit circuit library and simulator, now a core feature of Google's Cirq (Cirq).

This chapter is organized as follows: Section 2.2 presents relevant background about quantum computation and Section 2.3 outlines related prior work that we benchmark our work against. Section 2.4 demonstrates our key circuit construction, and Section 2.5 surveys applications of this construction toward important quantum algorithms. Section 2.6 introduces our open-source qudit circuit simulator. Section 2.7 explains our noise modeling methodology, and Section 2.8 presents simulation results for the generalized Toffoli circuits under these noise models.

In the remainder of the chapter, we present an application of this technique to give logarithmic depth decompositions of quantum arithmetic circuits—a carry lookahead adder and, by extension, addition by a constant. In Section 2.9 we present two compression circuits

for qubit-qutrit and qubit-ququart (d = 4) compression and evaluate advantages of various compression schemes. In Section 2.10 we present our decomposition of the zero-ancilla, in-place A + B adder which takes as input two registers A and B of qubits and possibly carry-in and carry-out; any fresh  $|0\rangle$  states used are generated locally. We then evaluate the costs of this decomposition. We end with extensions to our arithmetic decomposition in Sections 2.10.1 and 2.10.2 and finish with a discussion and summary in Section 2.11.

# 2.2 Background

A qubit is the fundamental unit of quantum computation. Compared to their classical counterparts which take values of either 0 and 1, qubits may exist in a superposition of the two states. We designate these two basis states as  $|0\rangle$  and  $|1\rangle$  and can represent any qubit as  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$  with  $||\alpha||^2 + ||\beta||^2 = 1$ .  $||\alpha||^2$  and  $||\beta||^2$  correspond to the probabilities of measuring  $|0\rangle$  and  $|1\rangle$  respectively.

Quantum states can be acted on by quantum gates which (a) preserve valid probability distributions that sum to 1 and (b) guarantee reversibility. For example, the X gate transforms a state  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$  to  $X |\psi\rangle = \beta |0\rangle + \alpha |1\rangle$ . The X gate is also an example of a classical reversible operation, equivalent to the NOT operation. In quantum computation, we have a single irreversible operation called measurement that transforms a quantum state into one of the two basis states with a given probability based on  $\alpha$  and  $\beta$ .

In order to interact different qubits, two-qubit operations are used. The CNOT gate appears both in classical reversible computation and in quantum computation. It has a control qubit and a target qubit. When the control qubit is in the  $|1\rangle$  state, the CNOT performs a NOT operation on the target. The CNOT gate serves a special role in quantum computation, allowing quantum states to become entangled so that a pair of qubits cannot be described as two individual qubit states. Any operation may be conditioned on one or more controls that act like the conditions of an if-statement, only performing the operation

on the states where all controls are  $|1\rangle$ .

Many classical operations, such as AND and OR gates, are irreversible and therefore cannot directly be executed as quantum gates. For example, consider the output of 1 from an OR gate with two inputs. With only this information about the output, the value of the inputs cannot be uniquely determined. These operations can be made reversible by the addition of extra, temporary workspace bits initialized to 0. Using a single additional ancilla, the AND operation can be computed reversibly as in Figure 2.1.

$$\begin{array}{c|c} |q_0\rangle & \longrightarrow & |q_0\rangle \\ |q_1\rangle & \longrightarrow & |q_1\rangle \\ |0\rangle & \longrightarrow & |q_0 \text{ AND } q_1\rangle \end{array}$$

Figure 2.1: Reversible AND circuit using a single ancilla bit. The inputs are on the left, and time flows rightward to the outputs. This AND gate is implemented using a Toffoli (CCNOT) gate with inputs  $q_0$ ,  $q_1$  and a single ancilla initialized to 0. At the end of the circuit,  $q_0$  and  $q_1$  are preserved, and the ancilla bit is set to 1 if and only if both other inputs are 1.

Classical operations are fed an input state and produce an output state but quantum operations do more. Quantum operations take a *superposition* state, a complex linear combination of some or all  $2^n$  classical (binary) input states and produce an output *superposition* state. For example, the quantum CNOT gate applied to a pair of control and target qubits  $|ct\rangle$  transforms an input superposition  $\alpha_1 |00\rangle + \alpha_2 |01\rangle + \alpha_3 |10\rangle + \alpha_4 |11\rangle$  to the output superposition  $\alpha_1 |00\rangle + \alpha_2 |01\rangle + \alpha_3 |11\rangle + \alpha_4 |10\rangle = \alpha_1 |00\rangle + \alpha_2 |01\rangle + \alpha_4 |10\rangle + \alpha_3 |11\rangle$ .

Physical systems in classical hardware are typically binary. However, in common quantum hardware, such as in superconducting and trapped ion computers, there is an infinite spectrum of discrete energy levels. The qubit abstraction is an artificial approximation achieved by suppressing all but the lowest two energy levels. Instead, the hardware may be configured to manipulate the lowest three energy levels by operating on qutrits. In gen-

eral, such a computer could be configured to operate on any number of d levels, except as d increases the number of opportunities for error, termed error channels, increases. Here, we focus on d=3 and later d=4 with which we achieve the desired improvements to the Generalized Toffoli gate and qudit "compression". For a complete guide to superconducting qubits we refer to Krantz et al. [2019].

In a three level system, we consider the computational basis states  $|0\rangle$ ,  $|1\rangle$ , and  $|2\rangle$  for qutrits. A qutrit state  $|\psi\rangle$  may be represented analogously to a qubit as  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle + \gamma |2\rangle$ , where  $||\alpha||^2 + ||\beta||^2 + ||\gamma||^2 = 1$ . Qutrits are manipulated in a similar manner to qubits; however, there are additional gates which may be performed on qutrits.

For instance, in quantum binary logic, there is only a single X gate. In ternary, there are three X gates denoted  $X_{01}$ ,  $X_{02}$ , and  $X_{12}$ . Each of these  $X_{ij}$  for  $i \neq j$  can be viewed as swapping the amplitudes of  $|i\rangle$  and  $|j\rangle$  and leaving the third basis element unchanged. For example, for a qutrit  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle + \gamma |2\rangle$ , applying  $X_{02}$  produces  $X_{02} |\psi\rangle = \gamma |0\rangle + \beta |1\rangle + \alpha |2\rangle$ . Each of these operations' actions can be found in the left state diagram in Figure 2.2.

There are two additional non-trivial operations on a single trit. They are the +1 and -1 (sometimes referred to as a +2) operations (with + meaning addition modulo 3). These operations can be written as  $X_{01}X_{12}$  and  $X_{12}X_{01}$ , respectively; however, for simplicity, we will refer to them as  $X_{+1}$  and  $X_{-1}$  operations. A summary of these gates' actions can be found in the right state diagram in Figure 2.2.

When we use qudits with more than three levels, there are many mores gates which can be used depending on d. For a single qudit we have access to every permutation of the d basis states, or d! - 1 nontrivial operations, but in practice, many of these operations are unnecessary and only a small number are needed for universal computation. We make use of the increment permutations, denoted  $X_{+k}$  where + is addition modulo d, which rotates a state  $|i\rangle$  to  $|i+k \mod d\rangle$  and the flip permutations denoted  $X_{ij}$  which flip or switch the

Figure 2.2: The five nontrivial permutations on the basis elements for a qutrit. (Left) Each operation here switches two basis elements while leaving the third unchanged. These operations are self-inverses. (Right) These two operations permute the three basis elements by performing a  $+1 \mod 3$  and  $-1 \mod 3$  operation. They are each other's inverses.

states  $|i\rangle$  and  $|j\rangle$ , leaving all others unchanged.  $X_{01}$  is equivalent to the qubit X gate.

Other, non-classical, operations may be performed on a single qudit. For example, the Hadamard gate (Nielsen and Chuang [2011]) can be extended to work on qudits in a similar fashion as the X gate was extended. In fact, all single qubit gates, like rotations, may be extended to operate on qudits. In order to distinguish qubit, qutrit, and qudit gates, all non-qubit gates will appear with an appropriate subscript.

Each of these operations can be extended to two qudits as a controlled operation that applies the single-qudit operation conditioned on the control qudit being in a certain state. For example, consider applying an  $X_{+2}$  operation on a d=4 level system conditioned on a control qudit being in the  $|3\rangle$  state. These controlled qudits have been physically realized and they are universal for qudit computation, as shown by Muthukrishnan and Stroud [2000]. This can be extended to any number of controls but only two-qudit gates can be directly executed on typical quantum hardware; any use of a multi-controlled gate has a decomposition into one and two qudit gates since these gates are universal. We only require a single 3-qubit, 2-controlled gate (Toffoli-like) whose decomposition is given by Di and Wei [2011] into basic one- and two-qubit gates. We represent these gates in circuit diagrams with the control types indicated by circles with the control values inside. The applied gates, specifically the increment  $(X_{+i})$  and flip gates  $(X_{ij})$  will be given as a square labeled with the name of the gate.

One question concerning the feasibility of using higher states beyond the standard two is whether these gates can be implemented and perform the desired manipulations. Qudit gates have been successfully implemented by Di and Wei [2011], Muthukrishnan and Stroud [2000], Klimov et al. [2003], Chi et al. [2022], indicating that it is possible to consider higher level systems apart from qubit only systems.

In order to evaluate an implementation of a quantum circuit, we consider quantum circuit costs. Quantum circuits consist of a sequence of operations, also called gates, applied to a set of input qubits. These circuits do not have fan-in or fan-out and so when represented each horizontal line in the circuit diagram corresponds to a single qubit and time flows from left to right from inputs to outputs. The space cost of a circuit is therefore the number of qubits (or qudits) and this cost is referred to as circuit width. Requiring ancilla increases the circuit width and therefore the space cost of a circuit. The time cost for a circuit is the depth of a circuit. The depth is the length of the critical path (in number of gates) from input to output.

#### 2.3 Prior Work

# 2.3.1 Qudits