## THE UNIVERSITY OF CHICAGO

## IN-FRIDGE CLASSICAL CONTROLLERS IN QUANTUM COMPUTING

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### DEPARTMENT OF COMPUTER SCIENCE

BY MOHAMMAD REZA JOKAR

> CHICAGO, ILLINOIS JUNE 2022

Copyright  $\bigodot$  2022 by Mohammad Reza Jokar

All Rights Reserved

$I\ dedicate\ this\ dissertation\ to\ my\ parents.$

# TABLE OF CONTENTS

| LIS | ST O              | F FIGU                                     | JRES                                                                                                                         |          | • | •           | •    | • | vi                                                                     |

|-----|-------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------|---|-------------|------|---|------------------------------------------------------------------------|

| LIS | ST O              | F TAB                                      | LES                                                                                                                          |          | • | •           |      |   | х                                                                      |

| AC  | CKNC              | WLED                                       | GMENTS                                                                                                                       |          | • | •           |      |   | xi                                                                     |

| AE  | BSTR              | ACT                                        |                                                                                                                              |          | • | •           | •    |   | xii                                                                    |

| 1   | INT               | RODU                                       | CTION                                                                                                                        |          | • |             |      |   | 1                                                                      |

| 2   |                   | NTUM<br>Introd                             | OOSTING QUANTUM COMPUTING POWER BY APPROX         I ERROR CORRECTION         uction                                          | <br><br> | • |             | <br> |   | 5<br>5<br>8<br>8                                                       |

|     |                   | 2.2.2<br>2.2.3<br>2.2.4<br>2.2.5           | Quantum Error CorrectionThe Surface CodeQuantum Computing Systems OrganizationClassical Control in Quantum Computing Systems | <br><br> | • |             | •    |   | 9<br>10<br>13<br>13                                                    |

|     | 2.3<br>2.4<br>2.5 | Relate                                     | tion: Decoding Must be Fast                                                                                                  | <br><br> | • |             | •    |   | 14<br>17<br>18<br>18<br>21                                             |

|     | 2.6<br>2.7        | 2.5.3<br>Impler<br>2.6.1<br>2.6.2<br>Metho | SFQ-Based Decoder                                                                                                            | · · ·    | • |             | •    |   | 21<br>25<br>25<br>26<br>28                                             |

|     | $2.8 \\ 2.9$      |                                            | tions                                                                                                                        |          |   |             |      |   | 33<br>38                                                               |

| 3   |                   | NG SFQ                                     | CALABLE DIGITAL CONTROLLER FOR QUANTUM CO<br>Q LOGIC                                                                         |          | • | •           | •    |   | 39<br>39                                                               |

|     | 3.2               |                                            | cound and Motivation                                                                                                         | <br><br> | • | •<br>•<br>• | •    |   | <ul> <li>33</li> <li>43</li> <li>43</li> <li>45</li> <li>46</li> </ul> |

|     | 3.3               |                                            | d Work                                                                                                                       | <br><br> | • |             | •    |   | 48<br>48<br>48<br>49                                                   |

|    | 3.4 | DigiQ quantum controller                                                                                                                                                      | ) |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    |     | 3.4.1 SFQ-based universal quantum computation                                                                                                                                 | ) |

|    |     | 3.4.2 Overview of $DigiQ$ architecture $\ldots \ldots \ldots$ | j |

|    | 3.5 | Software calibration of SIMD hardware                                                                                                                                         | j |

|    |     | 3.5.1 Calibrating single-qubit gates                                                                                                                                          | 3 |

|    |     | 3.5.2 Calibrating two-qubit gates                                                                                                                                             | ) |

|    | 3.6 | Methodology and Results                                                                                                                                                       | L |

|    |     | 3.6.1 Hardware results of $DigiQ$                                                                                                                                             |   |

|    |     | 3.6.2 Algorithmic performance results of $DigiQ$                                                                                                                              | 3 |

|    | 3.7 | Conclusions and Future work                                                                                                                                                   | ) |

| 4  | PRA | ACTICAL IMPLICATIONS OF SFQ-BASED TWO-QUBIT GATES 72                                                                                                                          | ) |

| -  | 4.1 | Introduction                                                                                                                                                                  |   |

|    | 4.2 | Background and Motivation                                                                                                                                                     |   |

|    |     | 4.2.1 Physical system                                                                                                                                                         |   |

|    |     | 4.2.2 Microwave optimal control                                                                                                                                               |   |

|    |     | 4.2.3 Fidelity functions                                                                                                                                                      |   |

|    |     | 4.2.4 SFQ control                                                                                                                                                             |   |

|    |     | 4.2.5 Prior work on SFQ-based gates and the motivation of this paper 85                                                                                                       |   |

|    | 4.3 | Detailed study of SFQ-based two-qubit gates                                                                                                                                   |   |

|    |     | 4.3.1 Methodology                                                                                                                                                             |   |

|    |     | 4.3.2 Entangling SFQ-based two-qubit gates on transmon qubit devices 89                                                                                                       | ) |

|    |     | 4.3.3 Realizing both entangling and non-entangling SFQ-based two-qubit                                                                                                        |   |

|    |     | gates on transmon devices                                                                                                                                                     | L |

|    |     | 4.3.4 SFQ-based two-qubit gates on fluxonium qubit devices                                                                                                                    | ŧ |

|    |     | 4.3.5 Comparison with microwave-based gates                                                                                                                                   | j |

|    | 4.4 | Conclusion                                                                                                                                                                    | 5 |

| 5  | CON | NCLUSION                                                                                                                                                                      | 7 |

| BI | TEE | 2ENCES                                                                                                                                                                        | ) |

| тU |     |                                                                                                                                                                               | 1 |

## LIST OF FIGURES

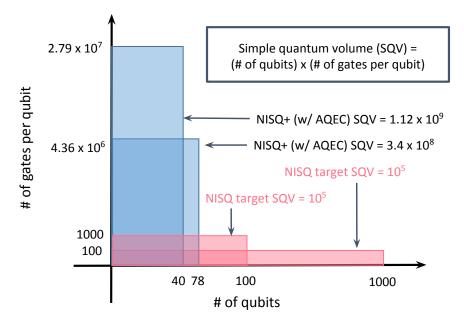

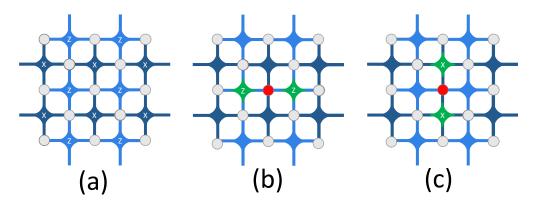

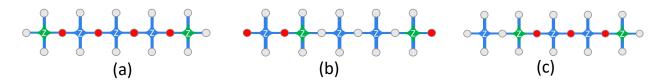

Boosting the quantum computation power with approximate error correction 2.1schemes. A machine with 1024 faulty physical qubits of error rate  $10^{-5}$  has an SQV of  $\approx 10^8$ . By performing fast, online, approximate decoding, we can trade the number of computational qubits for gate fidelity and boost the SQV by over a factor of 3,402. Moving to a higher code distance raises this increase to a factor of 11,163. NISQ machines are severely limited by gate fidelity, and introducing error mitigation techniques can have dramatic effects on SQV. . . . Fig. (a) shows a graphical illustration of a surface code mesh. Gray circles indi-2.2cate data qubits, and nodes labeled X and Z indicate ancillary qubits measuring X and Z stabilizers, respectively. Ancillary qubits are joined by colored edges to the data qubits that they are responsible for measuring. In Fig. (b) a single data qubit experiences a Pauli X error indicated by red coloring, causing the neighboring Z ancillary qubits to detect an odd parity in their data qubit sets and return +1 measurement values indicated by green coloring. In Fig. (c), the data qubit in red experiences a Pauli Z error, causing the vertically adjacent Xancillary qubits to return +1 measurement values. The entire error syndrome strings for either of these two cases would include a string of 12 values, two of which would be +1 and the remaining 10 would be  $0. \ldots \ldots \ldots \ldots \ldots \ldots$ 102.3This figure shows the errors happened in one row of the surface code grid. Fig. (a) shows a data qubit error pattern spanning across ancillary qubits. Each data qubit experiencing error is indicated in red, and the ancillary qubits returning +1measurement values are indicated in green. Each ancillary qubit that is adjacent to two erroneous data qubits does not signal the presence of any errors, as the parity of the data qubit sets are still even. This creates an *error string* that runs from the ancillary qubit on the left of the grid to the one on the right. Decoding must map these +1 values to the corresponding set of 4 data qubit errors that generated it. Fig. (b) and Fig. (c) show degeneracy in error syndrome generation by surface code data qubit error patterns. The figures depict two distinct sets of data qubit error patterns that both generate the same error syndromes. Both

patterns contain the same number of physical data errors, so these patterns are equally likely assuming independence of errors. 12

6

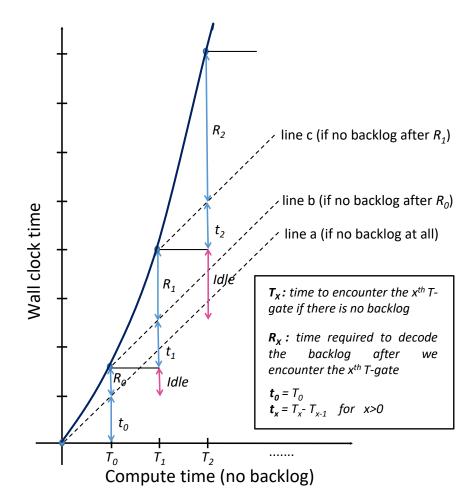

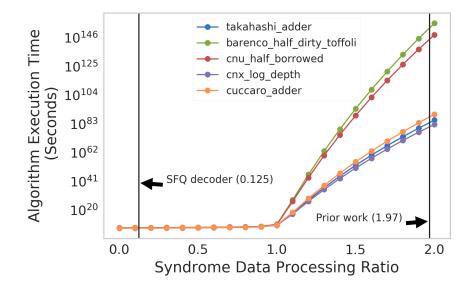

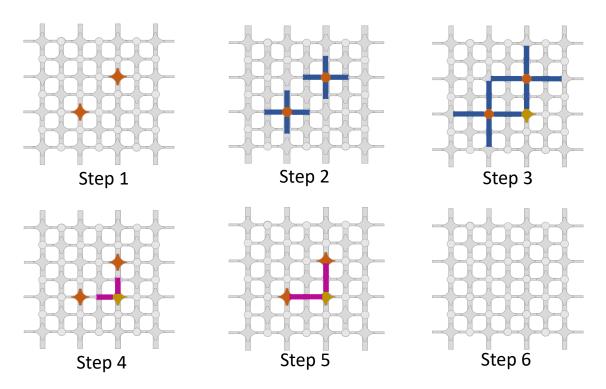

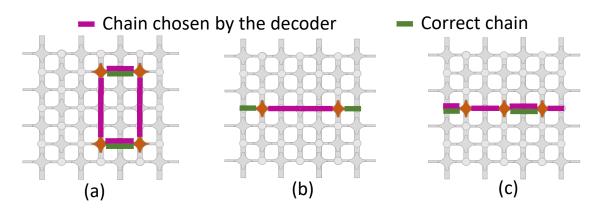

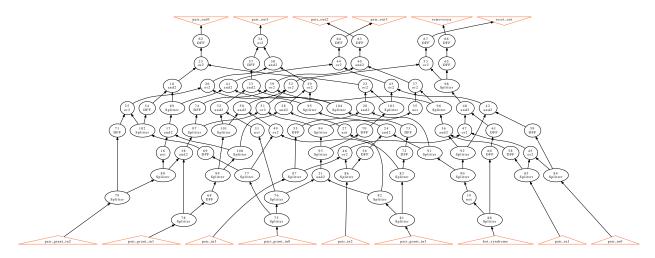

Exponential latency overhead when  $f = \left(\frac{r_{\text{gen}}}{r_{\text{proc}}}\right) > 1$ . X-axis shows the compute 2.4time if there is no backlog and y-axis shows the actual wall clock time; if there is no backlog we expect wall clock time to be the same as the compute time (line a). Every time we encounter a T-gate we need to decode all the syndromes up until that gate before we can continue the execution [Terhal, 2015]. When we encounter the first T-gate at time  $T_0$ , we need to finish the decoding of the data generated during  $t_0$  (not all the data is already decoded as decoding rate is slower than data generation rate) and it takes  $R_0$  to do that. During  $R_0$  where our quantum system is idle, more syndromes are generated and when we encounter the second T-gate at  $T_1 + R_0$ , we need to finish decoding those syndromes in addition to the syndromes generated during  $t_1$  before continuing the program execution. The syndrome data generated during the idle periods is the key reason behind data backlog creation which leads to exponential latency overhead. 152.5Running times of fault tolerant quantum algorithms with decoders of varying efficiency. The X-axis plots  $\frac{r_{\text{gen}}}{r_{\text{proc}}}$ . To the left of 1, data is processed as fast as it is generated, whereas rates to the right of 1 indicate that the decoder is slower than syndrome data is generated. The T-gates require synchronization with the decoder in order to execute. Prior work [Chamberland and Ronagh, 2018] claims that fast neural network inference decoders can perform inference in  $\sim 800$  ns, which places the decoder at approximately the 1.5 - 2 region for a system generating syndromes in the 400-500ns range. Our decoding results show that time to solution never exceeds 20ns, placing it below 1. Clearly computation becomes intractable quickly for slow decoders. 162.6Baseline solution to find the two closest hot syndrome modules. Step1: two decoder modules have "1" hot syndrome input. Step2: the hot syndrome modules propagate grow signals. Step3: the grow signals meet at an intermediate module. Step4: the intermediate module sends pair signals in the opposite direction. Step5: pair signals arrive at the hot syndrome modules. Step6: decoding is complete. Note that the decoder modules that receive a pair signal are considered as 222.7Scenarios where the SFQ decoder chooses the wrong chain where (a) no reset/boundary/equidistant mechanisms are employed, (b) no boundary/equidistant mechanisms are employed, and (c) no equidistant mechanism is employed. . . . 23Overview of decoder module microarchitecture. 272.82.9Pair subcircuit after SFQ specific optimizations and mapping. Triangular shapes at the bottom represent the primary inputs of the circuit and those at the top of the circuit show primary outputs. DFF is SFQ DRO DFF inserted for path balancing. Splitter (balanced) trees are also shown. Splitter is an asynchronous SFQ gate that receives a pulse at its input and after its intrinsic delay, it produces two almost identical output pulses. We insert splitters at the output of an SFQ gate (or a primary input) with more than one fanout. 28

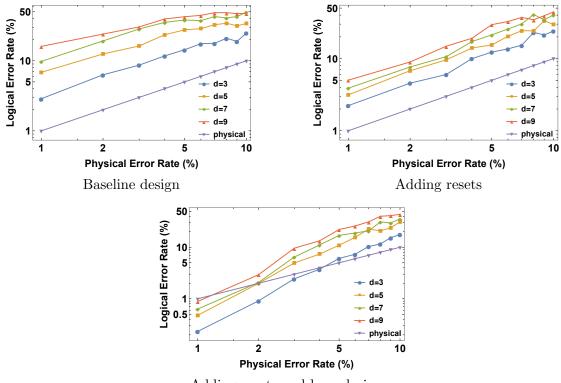

| 2.10         | Logical error rate performance of each incremental design step. The addition<br>of resets and boundaries each contribute heavily to the realization of pseudo-<br>thresholds, and have a dramatic effect on reducing the minimum achievable logical<br>error rates for each code distance                                                                                                                                                                                                                                                   | 30       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.11         | Results for our final design, including support for reset, boundary, and equidistant mechanisms. (a) Error rate scaling for the proposed decoder. An accuracy threshold is evident at approximately 5% physical error rate, while pseudo-thresholds span the range from $\sim 3.5\% - 5\%$ . (b) Logical error rates near the 5% physical error rate value. (c) Truncated unnormalized estimated probability distributions for the execution cycles required by each code distance in simulation. Window                                    |          |

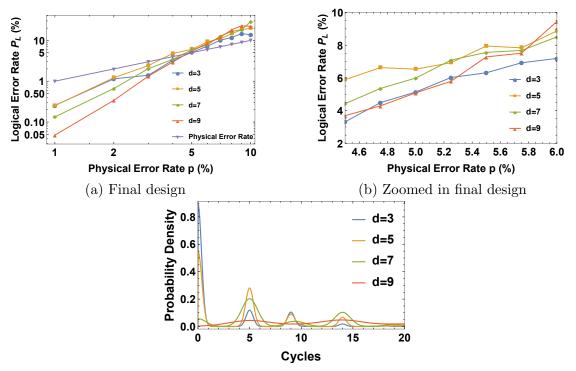

| 2.12         | shows up to 20 cycles for comparison across code distances. Notice that while distances 3, 5, 7 display peaks centered at 0, 5, 9, and 14 cycles Comparison of required code distances of different decoders to execute an algorithm consisting of 100 T-gates. Compared are the SFQ Decoder, MWPM decoder [Fowler et al., 2012a], neural network decoder [Baireuther et al., 2019], Union-Find decoder [Delfosse and Nickerson, 2017], and a theoretical MWPM decoder with no backlog. across both code distances and physical error rates | 31<br>35 |

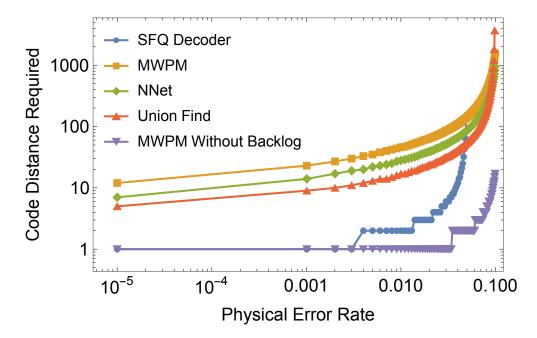

| 3.1          | (a) Today's controller design: controller at room temperature, (b) $DigiQ$ : con-                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

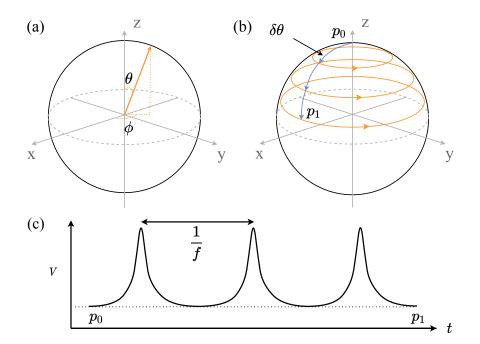

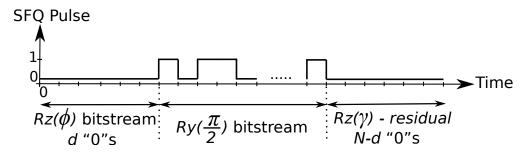

| 3.2          | troller close to quantum chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40       |

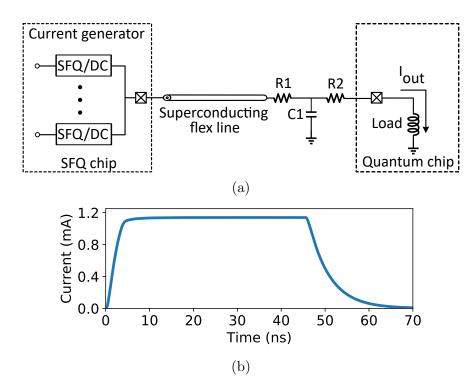

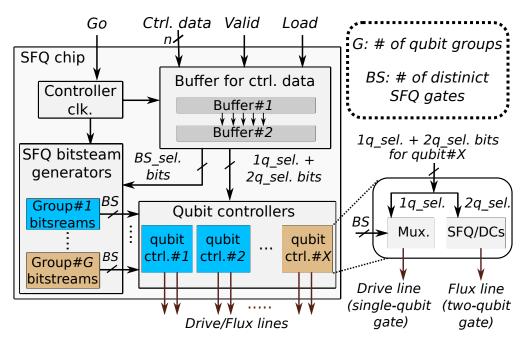

| $3.3 \\ 3.4$ | domain. $f$ is the qubit oscillation frequency. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                         | 44<br>53 |

| 3.5          | transmons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54<br>55 |

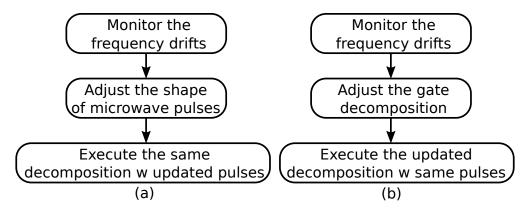

| 3.6          | Calibration process in (a) today's microwave-based quantum machines; (b) <i>DigiQ</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55 57    |

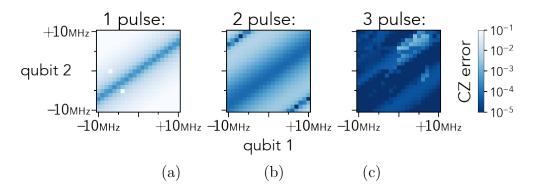

| 3.7          | CZ gate error as a function of frequency drift, assuming 1, 2, or 3 $U_{qq}$ operations                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

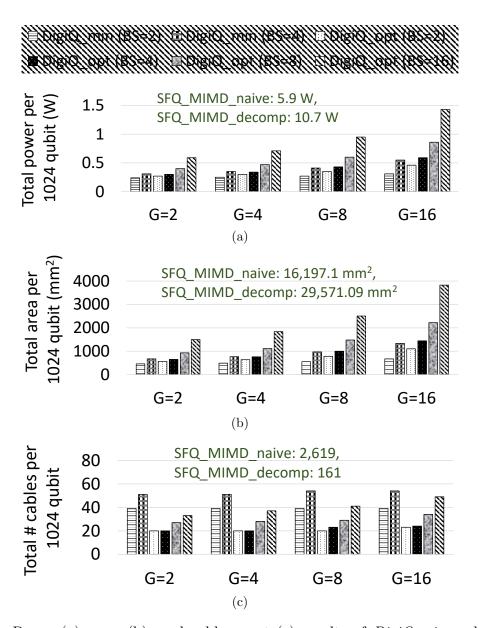

| 3.8          | and ideal single-qubit gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61       |

| 3.9          | comparison. $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63       |

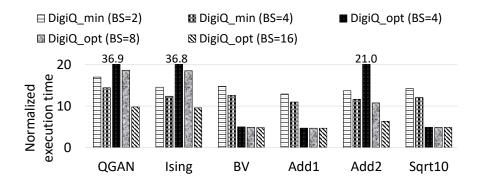

| -            | tem. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67       |

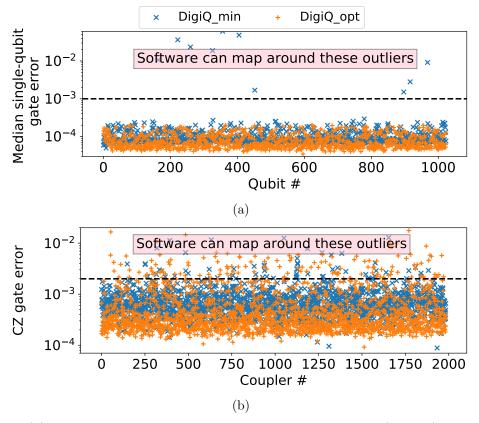

| 3.10         | (a) Median single-qubit gate error on $DigiQ_opt$ ( $BS=8$ ) and $DigiQ_min$ ( $BS=2$ ) with 1024 qubits (well representative of other configurations); (b) CZ gate error on each qubit pair. Software can map around the outliers using the noise-adaptive                                                                                                                                                                                                                                                                                 |          |

|              | mapping techniques [Murali et al., 2019a].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69       |

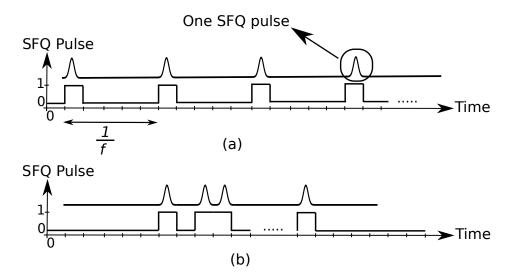

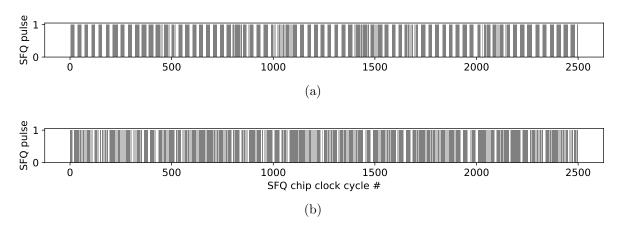

4.1 Bit representation of SFQ pulse trains. (a) coherent pulses are applied to the qubit (1 pulse per qubit oscillation period) to perform rotations around the y axis. (b) a bitstream found by genetic algorithm to perform arbitrary unitary. Bitstreams are processed one bit at a time; if the bit is "0", no pulse is applied to the qubit, and if the bit is "1", one SFQ pulse is applied to the qubit. . . . .

82

83

87

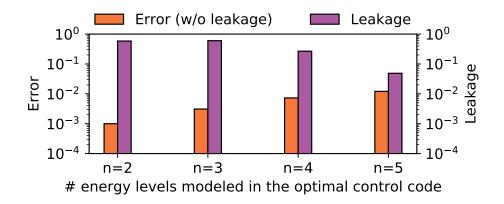

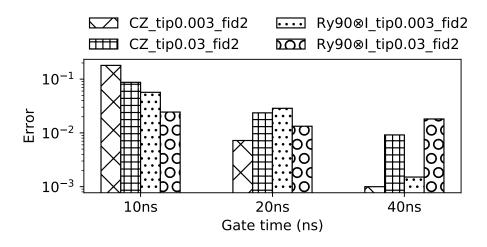

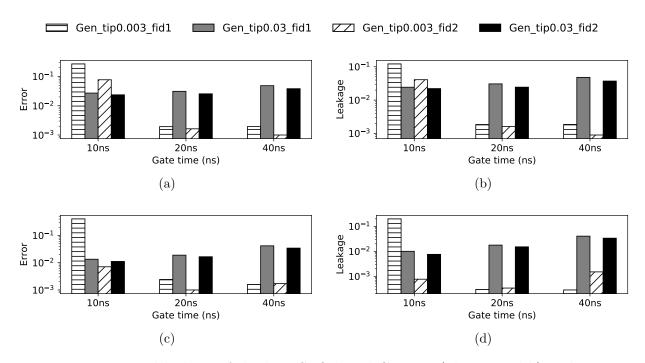

- 4.2 Error and leakage of the best SFQ-based CZ gate with 20 ns gate time found by the genetic algorithm on transmon qubit devices with  $\Omega_x$  control fields. Error is computed using Eq. (4.14) and takes into account only the *n* levels on which the gate was learned. Leakage is computed using Eq. (4.17) and considers higher levels. Thus, low error does not necessarily translate to low leakage.

- 4.4 Bit representation of SFQ bitstreams applied to qubit1 (plot a) and qubit2 (plot b) on a transmon system with  $\Omega_x$  control fields and 0.003 tip angle in order to realize a CZ gate with 20 ns gate time. Each SFQ chip clock cycle is 8 ps. . . . 88

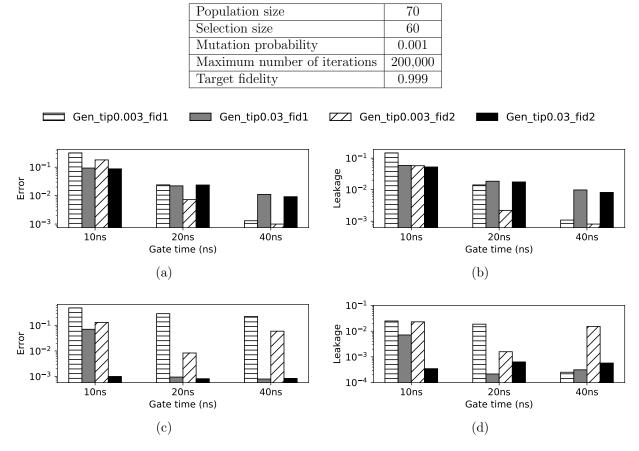

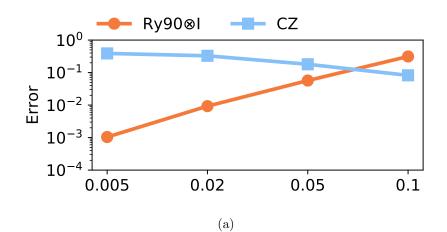

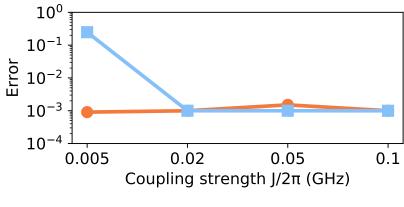

- 4.6 Sensitivity analysis on qubit coupling strength in transmon system with  $\Omega_x$  control fields. The results are shown for 0.003 tip angle and 10 ns (plot a), 20 ns (plot b), and 40 ns (plot c) gate times. The SFQ bitstreams are learned with *fid2*. 92

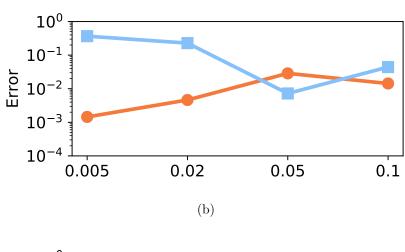

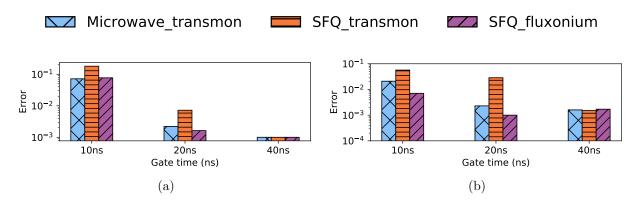

- 4.8 Error comparison between microwave-based gates obtained using Grape code and SFQ-based gates obtained using genetic algorithm (with 0.003 tip angle). The results are reported for CZ gate (plot a) and Ry90⊗I gate (plot b). . . . . . . 94

## LIST OF TABLES

| 2.1 | Characteristics of the simulated benchmarks                                                               | 14  |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 2.2 | The library of ERSFQ cells and corresponding characteristics used for synthe-                             |     |

|     | sizing the circuit into SFQ hardware. Josephson Junction count is listed in the                           |     |

|     | second column.                                                                                            | 32  |

| 2.3 | Experimental synthesis results for the SFQ Decoder. Shown are all gates utilized                          |     |

|     | in the synthesis, as well as submodules that comprise the main circuit. Pair_Req.                         |     |

|     | and Grow subcircuits have been combined into a single subcircuit                                          | 33  |

| 2.4 | Decoder execution time in nanoseconds across each code distance studied and                               |     |

|     | across all simulated error rates.                                                                         | 33  |

| 2.5 | Empirical parameter estimation given a model of the form $P_L \approx c_1 (p/p_{\rm th})^{c_2 \cdot d}$ . |     |

|     | Shown are estimated $c_2$ parameter values                                                                | 34  |

| 2.6 | Comparing decoding algorithms in terms of accuracy threshold. SFQ decoder                                 |     |

|     | sacrifices accuracy for speed in order to avoid exponential latency overhead and                          | ~-  |

|     | achieve quantum advantage                                                                                 | 37  |

| 3.1 | Design space for SFQ-based single-qubit gate controllers                                                  | 48  |

| 3.2 | Optimal parking frequencies and drift tolerance for $Rz(\phi)$ gates with $\leq 10^{-4}$                  |     |

|     | error for $N = 255$ .                                                                                     | 59  |

| 3.3 | The library of RSFQ cells and corresponding characteristics used for synthesis.                           | 61  |

| 3.4 | NISQ benchmark algorithms.                                                                                | 66  |

|     |                                                                                                           | ~ - |

| 4.1 | The parameters used in the genetic algorithm.                                                             | 87  |

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Prof. Fred Chong, for his continuous guidance and support during my Ph.D. study. I had many insightful discussions with Prof. Chong during my study, in which I learned how to tackle challenging research problems. Thanks to the opportunity to work with him, I developed invaluable hard skills and soft skills, for which I am forever grateful.

I am thankful to Prof. Massoud Pedram and Prof. Hank Hoffman, who have been part of my Ph.D. committee, for all their constructive comments and feedback, which improved the quality of this dissertation.

I would like to thank my co-advisor during the first few years of my Ph.D. study, Prof. Yanjing Li. I am grateful for the opportunity to work on many research projects on novel optical technologies [Jokar et al., 2020, 2019b,a, 2017, Yang et al., 2021].

I would like to express my gratitude to my co-author, Rich Rines, for many insightful meetings that we had. I really enjoyed solving complex problems with Rich. I am also thankful to my co-author, Adam Holmes, for many insightful discussions that we had, and for helping me learn quantum error correction and quantum optimal control.

I greatly appreciate the fruitful collaborations with my co-authors at University of Chicago, University of Southern California, and University of Illinois at Urbana-Champaign. I am also thankful to people in Prof. Chong's lab who helped me learn quantum computing.

I thank the International House (I-House) at the University of Chicago, for organizing cultural events and providing an opportunity for students and scholars from all around the world to meet and learn together. Being an I-House fellow has been a rewarding experience and has played a very important role in my growth in life.

Last but not least, I would like to express my deepest gratitude to my family and friends for their continuous love and support all through my Ph.D. study, which made this journey possible.

## ABSTRACT

Today's superconducting quantum computer prototypes rely on a classical controller at room temperature that controls the qubits inside the dilution refrigerator. This approach is simple and straightforward, however, it introduces significant scalability challenges: (1) quantum error correction techniques that are based on room temperature error decoding face exponential latency overhead due to the data backlog caused by the slow decoding process; (2) scalability is limited due to massive costs of generating and routing the microwave control signals.

In this thesis, novel cryogenic controllers are proposed to address the aforementioned challenges. First, we develop an in-fridge classical accelerator for error decoding using ultrafast superconducting Single Flux Quantum (SFQ) logic technology, which can expand the compute volume of near-term quantum machines by factors between 3,402 and 11,163. Second, we develop an in-fridge classical controller using SFQ logic to generate and route the control signals inside the dilution refrigerator. We use state-of-the-art SFQ synthesis tools to calculate the power and area of our in-fridge controller, and show that it can operate within the tight power and area budget of dilution refrigerators at >42,000-qubit scales. Finally, we investigate the practical implications of SFQ-based two-qubit gates and show that they can achieve similar gate fidelity and gate time to that of microwave-based gates. The results of this thesis show that cryogenic controllers play a key role in increasing the scalability and computing power of near-term quantum machines.

# CHAPTER 1 INTRODUCTION

Quantum computing has the potential to revolutionize computing and have massive effects on major industries including agriculture, energy, and materials science by solving computational problems that are intractable with conventional machines [Hastings et al., 2014, Svore and Troyer, 2016]. Superconducting quantum computing, one of the most promising technologies for building a quantum computer, has been studied in industry and academia [Brink et al., 2018, Steffen et al., 2011, Fu et al., 2017, Li et al., 2020], and many prototypes have been manufactured in the recent years [Arute et al., 2019, Kelly, 2018, Steffen et al., 2011, Fu et al., 2017]. However, today's prototypes rely on room temperature controllers which present severe scalability challenges.

First, relying on room temperature controllers causes challenges for boosting the computational power of quantum machines. *Quantum error correction* is a classical control technique that decreases the rate of errors in qubits and expands the "Simple Quantum Volume" (SQV). SQV can be defined as the number of computational qubits of a machine multiplied by the number of gates we expect to be able to perform without error. Prior work has suggested and analyzed software solutions for decoding the errors, but relying on hardwaresoftware communication can be slow, especially considering the cryogenic environment of typical quantum computing systems. If decoding occurs slower than error information is generated, the system will generate a backlog of information as it waits for decoding to complete, introducing an exponential time overhead that will kill any quantum advantage.

Second, large-scale quantum computers are essential in running many quantum algorithms and performing quantum error correction. However, today's prototypes rely on sending separate analog microwave control pulses for each qubit from a classical controller at room temperature to the quantum chip inside the dilution refrigerator, which presents severe scalability challenges due to the massive costs of generating/routing the analog microwave signals, and significant heat dissipation at millikelvin temperatures due to using a large number of high bandwidth coaxial cables [McDermott et al., 2018, Leonard et al., 2019, Li et al., 2019].

A promising approach proposed in this thesis to address the aforementioned challenges is utilizing cryogenic classical controllers. This thesis consists of three following projects:

(1) NISQ+: Boosting quantum computing power by approximating quantum error correction (Chapter 2). Quantum computers are growing in size, and design decisions are being made now that attempt to squeeze more computation out of these machines. In this spirit, we design a method to boost the computational power of near-term quantum computers by adapting protocols used in quantum error correction to implement "Approximate Quantum Error Correction (AQEC)." By approximating fully-fledged error correction mechanisms, we can increase the compute volume (qubits × gates, or "Simple Quantum Volume (SQV)") of near-term machines. The crux of our design is a fast hardware decoder that can approximately decode detected error syndromes rapidly. Specifically, we demonstrate a proof-of-concept that approximate error decoding can be accomplished online in near-term quantum systems by designing and implementing a novel algorithm in superconducting Single Flux Quantum (SFQ) logic technology. This avoids a critical decoding backlog, hidden in all offline decoding schemes, that leads to idle time exponential in the number of T gates in a program [Terhal, 2015].

Under a pure dephasing error model, the proposed accelerator and AQEC solution is able to expand SQV by factors between 3,402 and 11,163 on expected near-term machines. The decoder achieves a 5% accuracy threshold as well as pseudo-thresholds of approximately 5%, 4.75%, 4.5%, and 3.5% physical error rates for code distances 3, 5, 7, and 9, respectively. Decoding solutions are achieved in a maximum of  $\sim 20$  nanoseconds on the largest code distances studied. By avoiding the exponential idle time in offline decoders, we achieve a 10x reduction in required code distances to achieve the same logical performance as alternative designs.

This project was a collaboration between scholars at University of Chicago and University of Southern California. The outcome of the project was a research paper in ISCA 2020 conference [Holmes et al., 2020].

(2) DigiQ: A Scalable Digital Controller for Quantum Computers Using SFQ Logic (Chapter 3). Researchers in industry and academia have focused on designing infridge classical controllers in order to mitigate the scalability challenges of today's quantum computer prototypes. SFQ logic has the potential to maximize scalability thanks to its ultrahigh speed and very low power consumption. However, architecture design for SFQ logic poses challenges due to its unconventional pulse-driven nature and lack of dense memory and logic. Thus, research at the architecture level is essential to guide architects to design SFQ-based classical controllers for large-scale quantum machines.

In this work, we present DigiQ, the first system-level design of a Noisy Intermediate Scale Quantum (NISQ)-friendly SFQ-based classical controller. We perform a design space exploration of SFQ-based controllers and co-design the quantum gate decompositions and SFQ-based implementation of those decompositions to find an optimal SFQ-friendly design point that trades area and power for latency and control while ensuring good quantum algorithmic performance. To validate and characterize DigiQ, we first implement it using hardware description languages and synthesize it using state-of-the-art/validated SFQ synthesis tools. Our synthesis results show that DigiQ can operate within the tight power and area budget of dilution refrigerators at >42,000-qubit scales. Second, we confirm the effectiveness of DigiQ in running quantum algorithms by modeling the execution time and fidelity of a variety of NISQ applications.

This project was a collaboration between scholars at University of Chicago and University of Southern California. The outcome of the project was a research paper that will appear in HPCA 2022 conference [Jokar et al., 2022].

(3) Practical implications of SFQ-based two-qubit gates (Chapter 4). Prior work has demonstrated high-fidelity SFQ-based single-qubit gates. However, little research has been done on SFQ-based multi-qubit gates, which are necessary to realize SFQ-based universal quantum computing. In this work, we present the first thorough analysis of SFQ- based two-qubit gates. Our observations show that SFQ-based two-qubit gates tend to have high leakage to qubit non-computational subspace, which presents severe design challenges. We show that despite these challenges, we can realize gates with high fidelity by carefully designing optimal control methods and qubit architectures. We develop optimal control methods that suppress leakage, and also investigate various qubit architectures that reduce the leakage. After carefully engineering our SFQ-friendly quantum system, we show that it can achieve similar gate fidelity and gate time to microwave-based quantum systems. The promising results of this paper show that (1) SFQ-based universal quantum computation is both feasible and effective; and (2) SFQ is a promising approach in designing classical controllers for quantum machines because it can increase the scalability while preserving gate fidelity and performance.

This project was a collaboration between scholars at University of Chicago. The outcome of the project was a research paper in QCE 2021 conference [Jokar et al., 2021].

## CHAPTER 2

# NISQ+: BOOSTING QUANTUM COMPUTING POWER BY APPROXIMATING QUANTUM ERROR CORRECTION

## 2.1 Introduction

Quantum computing has the potential to revolutionize computing and have massive effects on major industries including agriculture, energy, and materials science by solving computational problems that are intractable with conventional machines [Hastings et al., 2014, Svore and Troyer, 2016. As we begin to build quantum computing machines of between 50-100 qubits [Preskill, 2018] and larger, design decisions are being made to attempt to get the most computation out of a machine, quantified in this work by expanding the "Simple Quantum Volume" (SQV). SQV can be defined as the number of computational qubits of a machine multiplied by the number of gates we expect to be able to perform without error, as in Fig. 2.1. One limiting factor on SQV now is that physical quantum bits (qubits) are extremely error-prone, which means that computation on these machines is bottlenecked by the short lifetimes of qubits. System designers combat this by attempting to build better physical qubits, but this effort is extremely difficult and classical systems can be used to alleviate the burden. Specifically, quantum error correction is a classical control technique that decreases the rate of errors in qubits and expands the SQV. Error correction proceeds by encoding a set of *logical* qubits to be used for algorithms into a set of faulty physical qubits. Information about the current state of the device, called *syndromes*, is extracted by a specific quantum circuit that does not disturb the underlying computation. Decoding is the process by which an error correcting protocol maps this information to a set of *corrections* that, if chosen correctly, should return the system to the correct logical state. Fully fault tolerant machines can expand the SQV rapidly by suppressing qubit errors exponentially with the code distance.

While a fully fault-tolerant quantum computer may take many years to construct, it is

Figure 2.1: Boosting the quantum computation power with approximate error correction schemes. A machine with 1024 faulty physical qubits of error rate  $10^{-5}$  has an SQV of  $\approx 10^8$ . By performing fast, online, approximate decoding, we can trade the number of computational qubits for gate fidelity and boost the SQV by over a factor of 3,402. Moving to a higher code distance raises this increase to a factor of 11,163. NISQ machines are severely limited by gate fidelity, and introducing error mitigation techniques can have dramatic effects on SQV.

possible to use the well-developed theory of error correction as inspiration for constructing error mitigation protocols that still provide a strong expansion in SQV. In this paper we present an approximate decoding solution specifically targeting execution time and show that we can in fact perform decoding at the speed of syndrome generation for near-term machines. Prior work has suggested and analyzed software solutions for decoding, but relying on hardware-software communication can be slow, especially considering the cryogenic environment of typical quantum computing systems. If decoding occurs slower than error information is generated, the system will generate a backlog of information as it waits for decoding to complete, introducing an exponential time overhead that will kill any quantum advantage (see Section 2.3). A hardware solution proposed here results in the ability to perform logical gates with orders of magnitude better fidelity and at the speed of syndrome generation, resulting in a major expansion in SQV as shown in Fig. 2.1. This relies on an approximate decoding algorithm implemented in superconducting Single Flux Quantum (SFQ) hardware. While the algorithmic design enables the accuracy of the hardware accelerator to be competitive at small scale with existing software implementations, the benefits of implementing the circuitry directly in SFQ hardware are numerous. Specifically, high clock speeds, low power dissipation, and unique gating style allows for our accelerator to be co-located with a quantum chip inside a dilution refrigerator, avoiding otherwise high communication costs.

This work contributes the following:

- 1. We design an approximate decoding algorithm for stabilizer codes based on SFQ hardware, leveraging unique capabilities that the hardware offers,

- 2. We show that using this new error mitigation technique, we can expand the SQV of near-term machines by factors of between 3,402 and 11,163,

- 3. We use Monte-Carlo simulation based benchmarking of the hardware accelerator, resulting in effective accuracy and pseudo-thresholds,

- 4. We perform system execution time analysis, realistically benchmarking the decoder performance in real time and showing that decoding is likely to be able to proceed at or exceeding the speed of data generation enabling the benefits of fault tolerant quantum computing.

- 5. We show that our online decoder requires 10x smaller code distance than offline decoders when decoding backlog accounted for.

The remainder of the paper is as follows: Section 2.2 describes the necessary background of quantum computation and details the specifications of typical quantum computing systems stacks. Section 2.2.2 describes quantum error correction and the decoding problem in detail. Section 2.4 describes relevant related work in the area ranging from optimized software implementations of matching algorithms to novel descriptions of neural network based decoders. Section 2.5 describes our decoding algorithm, and Section 2.6 describes implementation details of SFQ technology, and the circuit datapaths in detail. Section 2.7 describes our methodology for evaluation, including details of the simulation environment in which our accelerator was benchmarked, details of the metrics used to evaluate performance, and descriptions of novel synthesis tools used to generate efficient layouts of SFQ circuitry. Section 2.8 presents our accuracy results, a breakdown of the accelerator characterization including area, power, and latency footprints, a timing evaluation, and analysis of the SQV effects. Section 2.9 concludes.

## 2.2 Background

In this section we discuss the basics of quantum computation, quantum error correction, and a description of the fundamental components of a quantum computing system architecture.

## 2.2.1 Basics of Quantum Computation

Here we provide a brief overview of quantum computation necessary to discuss quantum error correction. For more detailed discussions see [Nielsen and Chuang, 2010]. A quantum computing algorithm is a series of operations on two level quantum states called *qubits*, which are quantum analogues to classical bits. A qubit state can be written mathematically as a superposition of two states as  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$ , where the coefficients  $\alpha, \beta \in \mathbb{C}$  and  $|\alpha|^2 + |\beta|^2 = 1$ . A measured qubit will yield a value of  $|0\rangle$  or  $|1\rangle$  with probability  $|\alpha|^2$  or  $|\beta|^2$ , respectively, at which point the qubit state will be exactly  $|0\rangle$  or  $|1\rangle$ . Larger quantum systems are represented simply as  $|\psi\rangle = \sum_i \alpha_i |i\rangle$  where  $|i\rangle$  are computational basis states of the larger quantum system.

Quantum operations (gates) transform qubit states to other qubit states. In this work we will be making use of particular quantum operations known as *Pauli gates*, denoted as  $\{I, X, Y, Z\}$ . These operations form a basis for all quantum operations that can occur on a single qubit, and therefore any operation can be written as a linear combination of these gates. Additionally, error correction circuits make use of the Hadamard gate H, an operation that constructs an evenly weighted superposition of basis elements when acting on a basis element. Two-qubit controlled operations will also be used, which can generate entanglement between qubits and are required to perform universal computation.

## 2.2.2 Quantum Error Correction

Qubits are intrinsically fragile quantum systems that require isolation from environmental interactions in order to preserve their values. *Decoherence*, for example the decay of a quantum state from a general state  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$  to the ground state  $|\psi'\rangle = |0\rangle$  happens rapidly in many physical qubit types, often on the order of tens of nanoseconds [Tomita and Svore, 2014, Tannu et al., 2017b]. This places a major constraint on algorithms: without any modifications to the system, algorithms can only run for a small, finite time frame with high probability of success.

To combat this, quantum error correction protocols have been developed. These consist of encoding a small number of *logical* qubits used for computation in algorithms into a larger number of physical qubits, resulting in a higher degree of reliability [Lidar and Brun, 2013, Dennis et al., 2002, Fowler et al., 2012a, Terhal, 2015]. In general, developing quantum error correction protocols is difficult as directly measuring the qubits that comprise a system will result in destruction of the data. To avoid this, protocols rely upon indirectly gathering error information via the introduction of extra qubits that interact with the primary set of qubits and are measured. This measurement data is then used to infer the locations of erroneous data qubits.

While many different types of protocols have been developed, this work focuses primarily on the *surface code*, a topological stabilizer code [Gottesman, 1997] that is widely considered to be the best performing code for the medium-term as it relies purely on geometrically local interactions between physical qubits greatly facilitating its fabrication in hardware, and has

Figure 2.2: Fig. (a) shows a graphical illustration of a surface code mesh. Gray circles indicate data qubits, and nodes labeled X and Z indicate ancillary qubits measuring X and Z stabilizers, respectively. Ancillary qubits are joined by colored edges to the data qubits that they are responsible for measuring. In Fig. (b) a single data qubit experiences a Pauli X error indicated by red coloring, causing the neighboring Z ancillary qubits to detect an odd parity in their data qubit sets and return +1 measurement values indicated by green coloring. In Fig. (c), the data qubit in red experiences a Pauli Z error, causing the vertically adjacent X ancillary qubits to return +1 measurement values. The entire error syndrome strings for either of these two cases would include a string of 12 values, two of which would be +1 and the remaining 10 would be 0.

been shown to have very high reliability overall [Fowler et al., 2012a].

## 2.2.3 The Surface Code

Errors can occur on physical qubits in a continuous fashion, as each physical qubit is represented mathematically by two complex coefficients that can change values in a continuous range. However, a characteristic of the quantum mechanics leveraged by the surface code is that these continuous errors can be *discretized* into a small set of distinct errors. In particular, the action of the surface code maps these continuous errors into Pauli error operators of the form  $\{I, X, Y, Z\}$  occurring on the data. This is one of the main features of the code that allows error detection and correction to proceed.

The surface code procedure that accomplishes error discretization, detection, and correction is an error correcting code that operates upon a two-dimensional lattice of physical qubits. The code designates a subset of the qubits as data qubits responsible for forming the logical qubit, and others as ancillary qubits responsible for detecting the presence of errors in the data. This is shown graphically in Fig. 2.2. Ancillary qubits interact with all of their neighboring data qubits and are then measured, and the measurement outcomes form the *error syndrome*. This set of operations forms the *stabilizer circuit*, where each ancillary qubit measures a four-qubit operator called a *stabilizer*.

## Error Detection

The ancillary qubits are partitioned into those denoted as X and Z ancilla qubits. These ancilla qubit sets are sufficient for capturing any Pauli error on the data qubits, as Y operators can be treated as a simultaneous X and Z error. The action of the X stabilizer is two-fold: the four neighboring data qubits are forced into a particular state that discretizes any errors that may have occurred on them. Second, the measurement of the X ancilla qubit signals the parity of the number of errors that have occurred on its four neighbors. For example, it yields a +1 value if the state of the four neighboring qubits has an even number of Z errors. The same is true of the Z stabilizers – these track the parity of X errors occurring in the neighboring qubits. If an odd number of errors have occurred in either case, the ancilla qubit measurement will yield a +1 value, an event known as a *detection event* [Fowler et al., 2012d], otherwise these will return values of 0 or -1 depending on convention. We will refer to the ancillary qubits returning +1 values as *hot syndromes*. The *error syndrome* of the code is a bit string of length equal to the total number of ancilla qubits, and is composed of all of these measurement values.

Decoding is the process of mapping a particular error syndrome string to a set of corrections to be applied on the device. An example of this process is shown graphically in Fig. 2.2. In this example, the hot syndromes generated by a single data qubit error are marked in red. Each single data qubit error causes the adjacent ancillary qubits to return +1 values.

A different situation occurs when strings of data qubit errors cross ancillary qubits, as shown in Fig. 2.3. Here, four consecutive data qubits experience errors which generates hot syndrome measurements on the far left and right of the grid. This is because each ancillary

Figure 2.3: This figure shows the errors happened in one row of the surface code grid. Fig. (a) shows a data qubit error pattern spanning across ancillary qubits. Each data qubit experiencing error is indicated in red, and the ancillary qubits returning +1 measurement values are indicated in green. Each ancillary qubit that is adjacent to two erroneous data qubits does not signal the presence of any errors, as the parity of the data qubit sets are still even. This creates an *error string* that runs from the ancillary qubit on the left of the grid to the one on the right. Decoding must map these +1 values to the corresponding set of 4 data qubit errors that generated it. Fig. (b) and Fig. (c) show degeneracy in error syndrome generation by surface code data qubit error patterns. The figures depict two distinct sets of data qubit error patterns that both generate the same error syndromes. Both patterns contain the same number of physical data errors, so these patterns are equally likely assuming independence of errors.

qubit along this chain detects even error parity, so they do not signal the presence of errors. Decoding must be able to pair the two hot syndromes, applying corrections along the chain that connects them.

#### Error Detection Can Fail

Notice that in Fig. 2.3 (a), if the data qubits on the left and right endpoints of the chain had also experienced errors, none of the ancillary qubits would have detected the chain. This represents a class of undetectable error chains in the code, and specifically occurs when chains cross from one side of the lattice to the other. The result of these chains are physical errors present in the code that cannot be corrected, and are known as *logical errors*, as they have changed the state of the logical qubit. One important characteristic of the surface code is the minimal number of qubits required to form a logical error. This number is referred to as the *code distance*, d of a particular lattice.

## 2.2.4 Quantum Computing Systems Organization

While qubits are the foundation of a device, a quantum computer must contain many layers of controlling devices in order to interact with qubits. Qubits themselves can be constructed using many different technologies, some of which include superconducting circuits [Linke et al., 2017, Fu et al., 2018, 2017, Barends et al., 2014, Kelly et al., 2015], trapped ions [Maslov, 2017, Linke et al., 2017, Figgatt et al., 2019, Häffner et al., 2005, Lekitsch et al., 2017], and quantum dots [Zajac et al., 2016]. Controlling these devices is often performed by application of electrical signals at microwave frequencies [Chow et al., 2012, Yang et al., 2003, Paraoanu, 2006, Plantenberg et al., 2007].

This work focuses on systems built around qubits that require cryogenic cooling to milliKelvin temperatures [Hornibrook et al., 2015]. These systems require the use of dilution refrigerators, and typical architectures involve classical controllers located in various temperature stages of the system. Such a system is described schematically in [Tannu et al., 2017b, Hornibrook et al., 2015], and presents many design constraints. Controllers inside the refrigerator are subject to area and power dissipation constraints [Patra et al., 2018, Sebastiano et al., 2017]. Communication between stages can be costly as well. Many systems are constructed today using control wiring that scales linearly with the number of qubits, which will prohibit the construction of scalable machines [Franke et al., 2018].

## 2.2.5 Classical Control in Quantum Computing Systems

Error correction classical processing requires high bandwidth communication of the measurement values of many qubits on the quantum substrate repeatedly throughout the operation of the device, encouraging studies of engineering solutions [Ware et al., 2017], feasibility [Tannu et al., 2017a] and controller design [Tannu et al., 2017b]. Not only are instruction streams primarily dominated by quantum error correction operations [Levy et al., 2009, 2011], but also the classical controller responsible for error correction processing must be tightly coupled to the quantum substrate. If communicating between the quantum substrate and error cor-

|                            | # qubits | # total gates | # T gates |

|----------------------------|----------|---------------|-----------|

| takahashi_adder            | 40       | 740           | 266       |

| barenco_half_dirty_toffoli | 39       | 1224          | 504       |

| cnu_half_borrowed          | 37       | 1156          | 476       |

| cnx_log_depth              | 39       | 629           | 259       |

| cuccaro_adder              | 42       | 821           | 280       |

Table 2.1: Characteristics of the simulated benchmarks.

recting controller is subject to excessive latencies, the execution of fault tolerant algorithms will be completely prohibited.

#### 2.3 Motivation: Decoding Must be Fast

Decoding must be done quickly for the surface code to perform well. During actual computation on a surface code error corrected device, there exist gates called *T*-gates that require knowledge of the current state of errors on the device before they can execute. <sup>1</sup> If decoding is slower than the rate at which syndromes are generated, an algorithm will create a *data backlog*. While the machine is waiting for decoder to process the backlog, more syndrome data is accumulating on the device, which must be processed before executing the subsequent *T*-gate. Over time, this results in latency overhead that is exponentially dependent upon the number of such gates. Specifically, the overhead scales as  $(\frac{r_{\text{gen}}}{r_{\text{proc}}})^k = f^k$ , where  $r_{\text{gen}}$  is the rate of data generation,  $r_{\text{proc}}$  is the rate of decoder processing, each in bauds, f is the decoding ratio, and k is the number of T gates in the quantum algorithm. An exponentially slow quantum computer eliminates all of its usefulness.

Fig. 2.4 shows the exponential latency overhead due to data backlog. The proof of this is summarized as follows (for more details see [Terhal, 2015]): suppose f > 1. This implies that there will be a time  $t_0$  in the application where we encounter a T gate and must wait for syndrome data to be decoded before continuing. Let  $\Delta_{\text{gen}}$  be the amount of time that the machine must stall for processing this data. During this time an additional  $D_1 = r_{\text{gen}} \times \Delta_{\text{gen}}$ bits of syndrome data is generated, which can be processed in time  $\Delta_{\text{proc}} = r_{\text{gen}} \Delta_{\text{gen}}/r_{\text{proc}} =$

<sup>1.</sup> Errors commute and can be post-corrected for other gates, but not T-gates.

Figure 2.4: Exponential latency overhead when  $f = (\frac{r_{\text{gen}}}{r_{\text{proc}}}) > 1$ . X-axis shows the compute time if there is no backlog and y-axis shows the actual wall clock time; if there is no backlog we expect wall clock time to be the same as the compute time (line a). Every time we encounter a T-gate we need to decode all the syndromes up until that gate before we can continue the execution [Terhal, 2015]. When we encounter the first T-gate at time  $T_0$ , we need to finish the decoding of the data generated during  $t_0$  (not all the data is already decoded as decoding rate is slower than data generation rate) and it takes  $R_0$  to do that. During  $R_0$  where our quantum system is idle, more syndromes are generated and when we encounter the second T-gate at  $T_1 + R_0$ , we need to finish decoding those syndromes in addition to the syndromes generated during  $t_1$  before continuing the program execution. The syndrome data generated during the idle periods is the key reason behind data backlog creation which leads to exponential latency overhead.

$f\Delta_{\text{gen}}$ . The backlog problem begins to be noticeable at this point, where during processing of the first block  $D_1$ , we generate a *new block*  $D_2 = r_{\text{gen}} \times \Delta_{\text{proc}} = fD_1 > D1$  in size. Then, at the next T gate this process repeats, and we again generate a block of data of size  $D_3 = fD_2 = f^2D_1$  bits. Hence, by the k'th T gate, we generate an overhead of  $f^kD_1$  bits

Figure 2.5: Running times of fault tolerant quantum algorithms with decoders of varying efficiency. The X-axis plots  $\frac{r_{\text{gen}}}{r_{\text{proc}}}$ . To the left of 1, data is processed as fast as it is generated, whereas rates to the right of 1 indicate that the decoder is slower than syndrome data is generated. The *T*-gates require synchronization with the decoder in order to execute. Prior work [Chamberland and Ronagh, 2018] claims that fast neural network inference decoders can perform inference in ~ 800 ns, which places the decoder at approximately the 1.5 - 2 region for a system generating syndromes in the 400-500ns range. Our decoding results show that time to solution never exceeds 20ns, placing it below 1. Clearly computation becomes intractable quickly for slow decoders.

#### to process, exponential in the decoder's performance ratio.

As a specific example, consider a multiply-controlled NOT operation on 100 logical qubits from [Holmes et al., 2018]. This algorithm contains ~ 2356 gates, of which 686 are *T*-gates after decomposition. Assuming that a syndrome generation cycle time is approximately 400 ns [Ghosh et al., 2012], and the best prior decoder requires 800 ns to execute [Chamberland and Ronagh, 2018], the ratio  $(r_{\rm gen}/r_{\rm proc}) = 2$ , and the execution time is intractable.

Fig. 2.5 shows a simulation of real quantum subroutines each composed of a different number of T gates as denoted in Table 2.1. The exponential overhead scaling shows that as decoders become slower than the rate at which data is being generated (which occurs for "syndrome data processing ratios" over 1), the overheads quickly become intractable. Regardless of the effectiveness of the decoder, if it operates at a processing ratio higher than 1 then it will impose exponentially high latency overheads on algorithm execution. The algorithms all draw inspiration from [Barenco et al., 1995]. Barenco-half-dirty-Toffoli is a logarithmic depth multi-control Toffoli gate using O(n) ancilla bits. It performs the same computation as the "cnx-log-depth" gate with a different circuit. The "cnu-half-borrowed" gives an implementation of a multi-control Toffoli using O(n) dirty ancilla, meaning the initial states of these bits does not need to be known. The Cuccaro adder is a linear depth implementation of a reversible A + B adder, i.e. two registers of the specified length added together. It has a carry in and a carry out bit as well. The Takahashi adder is an optimized version of the Cuccaro adder [Takahashi et al., 2009].

This is the primary motivation for this work – the hardware decoder must be able to execute faster than syndrome data are generated as a prerequisite for tractable fault tolerant computation.

#### 2.4 Related Work

Early work focused on the development of and modifications to the minimum weight perfect matching algorithm (MWPM) [Edmonds, 1965b,a] to adapt it to surface code decoding [Fowler et al., 2012c,b]. This resulted in a claimed constant time algorithm after parallelization [Fowler, 2013].

Other work has constructed maximum likelihood decoders (MLD) based on tensor network contraction [Bravyi et al., 2014]. This work is computationally more expensive than minimum-weight perfect matching, but is more accurate.

Neural networks have been explored as possible solutions to the decoding problem as well [Varsamopoulos et al., 2019a, 2017, 2019b, 2018, Chamberland and Ronagh, 2018, Varsamopoulos et al., 2017, 2018, Baireuther et al., 2019, Torlai and Melko, 2017]. Feedforward neural networks and recurrent neural networks have been explored in combination with lookup tables to form decoders. The primary distinguishing factor in these systems is that the networks function as *high level decoders* in that they predict both a sequence of error corrections on data qubits along with the existence of a logical error. In this sense, they operate at a higher level than both the MWPM and MLD decoders, seemingly at the cost of execution time with respect to training complexity.

Lastly, more customized algorithms have been developed specifically targeting the surface code decoding problem, including renormalization group decoders [Duclos-Cianci and Poulin, 2010b], Union-Find decoding [Delfosse and Zémor, 2017, Delfosse and Nickerson, 2017], and others [Wootton, 2015, Duclos-Cianci and Poulin, 2010a].

The primary distinguishing factor of our work is that the decoder design is guided by practical system performance. Accuracy has been sacrificed in order to achieve quantum advantage. While the proposed decoder design may not achieve logical error suppression at the same order as some other algorithms, the ability to perform the algorithm in SFQ hardware at or exceeding the speed of syndrome generation is achieved, as is satisfaction of system design constraints.

#### 2.5 Decoder Overview and Design

In this section we describe prior decoding algorithms, followed by details of our approximate decoding algorithm, and demonstrate how we make efficient use of unique features of SFQ gates to implement the algorithm in hardware.

## 2.5.1 Prior Decoding Algorithms and their Practical Implications

Different error chains can cause the same error syndrome. The decoding problem requires that the likely set of error chains be reported as a solution, given a particular error syndrome. This can be formulated as a matching problem. Specifically, given an error syndrome, we can construct a complete graph on vertices associated with each ancillary qubit that reported an error, and calculate the weight of each edge in the graph based on the Manhattan distance between its vertices on the original surface code grid, which corresponds to the shortest path between its vertices on the grid. The goal is to find the likely pairing of the syndromes using

#### Algorithm 1: Minimum Weight Matching Decoder Algorithm

**Input:** List of hot syndromes and their (x, y) coordinates on the surface code grid. **Output:** Set of error chains.

- 1 Construct a complete graph G = (V, E) on vertices associated with hot syndromes.

- 2 Calculate the weight  $w_{e_i}$  for each  $e_i \subset E$  that connects  $v_{i_1}$  and  $v_{i_2}$  vertices based on their Manhattan distance;  $w_{e_i} = |x_{i_1} x_{i_2}| + |y_{i_1} y_{i_2}|$ , where  $(x_{i_1}, y_{i_1})$  and  $(x_{i_2}, y_{i_2})$  are the coordinates of  $v_{i_1}$  and  $v_{i_2}$  vertices, respectively.

- **3** Find a perfect matching  $M \subset E$  such that  $\sum_{e_i \in M} w_{e_i}$  is minimum.

- 4 Return M as the set of error chains.

#### Algorithm 2: Union-Find Decoder Algorithm

**Input:** List of hot syndromes and their (x, y) coordinates on the surface code grid. **Output:** Set of error chains.

- 1 Create a cluster for each hot syndrome. These clusters are odd as each includes an odd number of hot syndromes (i.e., 1).

- 2 Initialize the coordinates of each cluster's up, down, left, and right borders on the grid to the coordinate of the cluster's hot syndrome.

- **3** While there exist an odd cluster:

- (I) Grow all the odd clusters in all directions on the grid by half edge, and update the coordinates of the borders.

- (II) If odd clusters meet, merge them and update the number of hot syndromes in the new cluster.

- (III) Remove the clusters that have an even number of hot syndromes.

- 4 Construct a spanning forrest, and apply the peeling decoder to find the set of error chains [Delfosse and Nickerson, 2017].

these weights, which can be done by solving the MWPM problem; given our error model, the likelihood of a specific path between two vertices being the correct set of errors decreases exponentially with the length of the path, thus the shortest path has the maximum likelihood. See Algorithm 1 for the pseudocode of the MWPM decoder. This decoder is effective and provides high accuracy threshold, but it has a worst case time complexity of  $O(n^3)$  [Delfosse and Nickerson, 2017], which is too slow for large code distances [Das et al., 2020]. Thus, prior work proposed faster decoders.

Union-Find is an example of such decoders that uses the Union-Find data structure to find a set of error chains. Union-Find decoder has a worst case time complexity of  $O(n\alpha(n))$ where  $\alpha(n) \leq 3$  for all practical purposes [Delfosse and Nickerson, 2017], while it decreases the accuracy threshold by 0.4% compared to MWPM decoder. See Algorithm 2 for the pseudocode of the Union-Find decoder. Although Union-Find decoder achieves almost-linear time complexity, the decoding time is still longer than the syndrome generation time (> 2X longer), which leads to exponential latency overhead (see Sec. 2.3). Thus, we need to further speed-up the decoding algorithm.

So far, we discussed that latency is one of the main criteria for the decoding algorithms. However, for the room temperature decoders, bandwidth between the quantum chip and the decoder is another main criteria. Such decoders may need to *continuously* (every syndrome generation cycle) receive the syndrome information from the quantum chip and perform the decoding, which leads to significant scalability challenges. Note that today's quantum computers (which are not fault tolerant) already have scalability challenges as they rely on a classical controller to receive control pulses (see Chapter 3), and adding a room temperature decoder only worsen the situation. Thus, we need to develop in-fridge decoders.

SFQ is a promising logic technology to implement in-fridge decoders due to its unique characteristics such as very low power consumption and ultra-high speed. An SFQ-based decoder not only reduces the aforementioned bandwidth requirements significantly but also can perform the decoding with low latency thanks to high SFQ clock speed. The next question is: can we implement either of MWPM or Union-Find decoders using SFQ logic? For a quantum system with 1000 logical qubits and code distance of 11, MWPM and Union-Find decoders requires > 1.5 MB and > 2.5 MB memory capacity, respectively [Das et al., 2020], and the required memory capacity increases with the code distance and the number of logical qubits. However, one limitation of SFQ technology is the lack of a dense memory (memory density is ~ 400 Kb/ $cm^2$  based on optimistic estimations [Tannu et al., 2017b]), which makes the implementation of MWPM and Union-Find decoders infeasible at large scales. This suggests that we need to modify the decoding algorithms based on the characteristics of SFQ technology.

## 2.5.2 A Greedy Approach

Our decoding algorithm is based upon a greedy approximation to the minimum weight matching problem. The algorithm calculates all Manhattan distances  $d(v_i, v_j)$  between vertices and sorts them in ascending order  $d_1, d_2, ..., d_{k'}$  where  $k' = \binom{k}{2}$ . All of the corresponding probability weights are calculated, transforming this ordering to a descending order of likelihood. Then, for each edge e in descending order, add e to the solution M if it forms a matching. This means that it adds another two distinct vertices into M that were not already present. To account for boundary conditions, we introduce a set of external nodes connected to the appropriate sides of the lattice, and connected to one another with weight 0. Under this formulation, the algorithm is a 2-approximation of the optimal solution [Drake and Hougardy, 2003].

## 2.5.3 SFQ-Based Decoder

In this section, we introduce the functional design of our SFQ-based decoder and give some rational for each aspect of its design. As a reminder, Single Flux Quantum is classical logic implemented in superconducting hardware that does not perform any quantum computation. It is a medium used to express our classical algorithm. The decoder is placed above the quantum chip layer; it receives measurement results from ancillary qubits as input, and returns a set of corrections as output. For scalability, our decoder design is built out of a two dimensional array of modules implemented in SFQ logic circuits that we refer to as *decoder modules*. These are connected in a rectilinear mesh topology. Modules are identical and there is one module per each data and ancillary qubit, denoted as *data qubit modules* and *ancilla qubit modules*, respectively. Each decoder module has one input called the *hot syndrome input* that comes from the measurement outcome of the physical quantum bits and determines if the module corresponds to a hot syndrome (note that this input can be "1" only for ancilla qubit modules). Each module contains one output called the *error output* that determines if the module is contained in the error chain (this output can be "1" for

Figure 2.6: Baseline solution to find the two closest hot syndrome modules. Step1: two decoder modules have "1" hot syndrome input. Step2: the hot syndrome modules propagate grow signals. Step3: the grow signals meet at an intermediate module. Step4: the intermediate module sends pair signals in the opposite direction. Step5: pair signals arrive at the hot syndrome modules. Step6: decoding is complete. Note that the decoder modules that receive a pair signal are considered as part of the error chain that has occurred.

all of the decoder modules). In addition, each module has connections to adjacent modules (left, right, up and down).

Our approximate decoder algorithm proceeds as follows. First, the algorithm finds the two modules with "1" hot syndrome input, called *hot syndrome modules*, that are closest together. Next, the algorithm reports the chain of modules connecting them as the correction chain. Finally, it resets the hot syndrome input of the two modules and searches for the next two closest hot syndrome modules. The decoder continues this process until no module with "1" hot syndrome input exists. This is graphically displayed in Fig. 2.6.

**Baseline Solution:** Our baseline design finds the two closest hot syndrome modules as shown in Fig. 2.6 as follows: 1) every hot syndrome module sends *grow* signals to all the adjacent modules in all four directions; each adjacent module propagates the grow signal

Figure 2.7: Scenarios where the SFQ decoder chooses the wrong chain where (a) no reset/boundary/equidistant mechanisms are employed, (b) no boundary/equidistant mechanisms are employed, and (c) no equidistant mechanism is employed.

in the same direction. Grow signals propagate one step at each cycle. 2) When two grow signals intersect at an *intermediate module*, we generate a set of *pair* signals and backpropagate these to their hot syndrome origins. All of the decoder modules that receive pair signals are part of the error chain. Note that more than one intermediate module might exist, however, only one of them is effective and sends the pair signals. For example, in Fig. 2.6, two intermediate modules receive the grow signals, and the decoder is hardwired to be effective (ineffective) when it receives grow signals from up and left directions (down and right directions). Intermediate module refers to the effective one. The baseline solution does not show accuracy or pseudo-threshold behavior and demonstrates poor logical error rate suppression, see the incremental results presented in Section 2.8 in Fig. 2.11.