#### THE UNIVERSITY OF CHICAGO

#### BALANCING PERFORMANCE AND ENERGY IN COMPUTING SYSTEMS

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

#### DEPARTMENT OF COMPUTER SCIENCE

BY CONNOR KELLY IMES

CHICAGO, ILLINOIS

JUNE 2018

Copyright © 2018 by Connor Kelly Imes  $\label{eq:connorKelly Imes}$  All Rights Reserved

# TABLE OF CONTENTS

| LIS             | ST O           | F FIGU  | JRES                                  | vi |  |  |  |  |  |

|-----------------|----------------|---------|---------------------------------------|----|--|--|--|--|--|

| LIST OF TABLES  |                |         |                                       |    |  |  |  |  |  |

| ACKNOWLEDGMENTS |                |         |                                       |    |  |  |  |  |  |

| AE              | BSTR           | ACT     |                                       | xi |  |  |  |  |  |

| 1               | 1 INTRODUCTION |         |                                       |    |  |  |  |  |  |

|                 | 1.1            | Thesis  | Statement                             | 1  |  |  |  |  |  |

|                 | 1.2            | Proble  | m Description                         | 1  |  |  |  |  |  |

|                 | 1.3            | Contri  | butions                               | 4  |  |  |  |  |  |

|                 |                | 1.3.1   | POET                                  | 5  |  |  |  |  |  |

|                 |                | 1.3.2   | CoPPer                                | 6  |  |  |  |  |  |

|                 |                | 1.3.3   | CEES                                  | 8  |  |  |  |  |  |

|                 |                |         |                                       |    |  |  |  |  |  |

| 2               | REL            |         |                                       | 10 |  |  |  |  |  |

|                 | 2.1            |         | 5                                     | 10 |  |  |  |  |  |

|                 | 2.2            |         | 1 0                                   | 13 |  |  |  |  |  |

|                 | 2.3            | Inspire | ed Projects                           | 15 |  |  |  |  |  |

| 0               |                |         |                                       |    |  |  |  |  |  |

| 3               |                |         |                                       | 17 |  |  |  |  |  |

|                 | 3.1            |         |                                       | 17 |  |  |  |  |  |

|                 | 3.2            |         |                                       | 19 |  |  |  |  |  |

|                 |                | 3.2.1   |                                       | 20 |  |  |  |  |  |

|                 |                | 3.2.2   | 1                                     | 22 |  |  |  |  |  |

|                 |                | 3.2.3   |                                       | 24 |  |  |  |  |  |

|                 | 3.3            | -       |                                       | 25 |  |  |  |  |  |

|                 |                | 3.3.1   | 1                                     | 26 |  |  |  |  |  |

|                 |                | 3.3.2   |                                       | 27 |  |  |  |  |  |

|                 |                | 3.3.3   | Runtime                               | 28 |  |  |  |  |  |

|                 | 3.4            | Experi  | mental Design                         | 29 |  |  |  |  |  |

|                 |                | 3.4.1   | Applications                          | 30 |  |  |  |  |  |

|                 |                | 3.4.2   | Evaluation Platforms                  | 30 |  |  |  |  |  |

|                 | 3.5            | Embed   |                                       | 33 |  |  |  |  |  |

|                 |                | 3.5.1   | Meeting Latency Targets               | 34 |  |  |  |  |  |

|                 |                | 3.5.2   | Energy Minimization                   | 35 |  |  |  |  |  |

|                 |                | 3.5.3   |                                       | 37 |  |  |  |  |  |

|                 |                | 3.5.4   | <del>-</del>                          | 38 |  |  |  |  |  |

|                 |                | 3.5.5   |                                       | 39 |  |  |  |  |  |

|                 | 3.6            |         |                                       | 40 |  |  |  |  |  |

|                 | -              |         | · · · · · · · · · · · · · · · · · · · | 41 |  |  |  |  |  |

|   |     | 3.6.2   | Energy Minimization                         |

|---|-----|---------|---------------------------------------------|

|   |     | 3.6.3   | Responding to Application Phases            |

|   |     | 3.6.4   | Adapting to Other Applications              |

|   |     | 3.6.5   | Configurations and Overhead                 |

|   | 3.7 | Discuss | sion of Results and Limitations             |

|   | 3.8 |         | An Extension of POET                        |

|   | 0.0 | 3.8.1   | Motivation                                  |

|   |     | 3.8.2   | Further Generalizing POET's Design          |

|   |     | 3.8.3   | Evaluation                                  |

| 4 | COI | odeb. ( | CONTROL PERFORMANCE WITH POWER              |

| 4 | 4.1 |         | tion                                        |

|   | 4.1 | 4.1.1   | The Future of Software DVFS                 |

|   |     | 4.1.1   | The Challenges of Actuating Power           |

|   | 4.2 |         | eral Power Capping Design                   |

|   | 4.2 | 4.2.1   |                                             |

|   |     | 4.2.1   |                                             |

|   |     |         | The Gain Limit                              |

|   | 4.9 | 4.2.3   | Using CoPPer                                |

|   | 4.3 | _       | mental Design                               |

|   |     | 4.3.1   | Testing Platform                            |

|   |     | 4.3.2   | Applications and Inputs                     |

|   | 4 4 | 4.3.3   | Execution and Analysis                      |

|   | 4.4 |         | tion $\dots$ $7$                            |

|   |     | 4.4.1   | Efficiently Meeting Performance Goals       |

|   |     | 4.4.2   | Controlling Memory-bound Applications       |

|   |     | 4.4.3   | Reducing Power for Unachievable Goals       |

|   |     | 4.4.4   | Adapting to Runtime Changes                 |

|   |     | 4.4.5   | Multiple Applications                       |

|   |     | 4.4.6   | Overhead Analysis                           |

| 5 | CEE | ES: CLA | SSIFICATION OF ENERGY-EFFICIENT SETTINGS 8  |

|   | 5.1 | Motiva  | tion                                        |

|   |     | 5.1.1   | Energy Efficiency is a Unique Challenge     |

|   |     | 5.1.2   | Learning Energy Efficiency                  |

|   | 5.2 | Classif | ying System Settings                        |

|   |     | 5.2.1   | Training Data                               |

|   |     | 5.2.2   | Performance Counters                        |

|   | 5.3 | Experi  | mental Design                               |

|   |     | 5.3.1   | Training Applications                       |

|   |     | 5.3.2   | Evaluation Applications                     |

|   |     | 5.3.3   | Classification Algorithms                   |

|   | 5.4 | Evalua  | tion                                        |

|   |     | 5.4.1   | Reducing Energy Consumption                 |

|   |     | 5.4.2   | Classifier Interval and Feature Selection 9 |

|    | 5.4.3 Application Dynamics                  | 98 |

|----|---------------------------------------------|----|

|    | 5.4.4 Overhead                              | 00 |

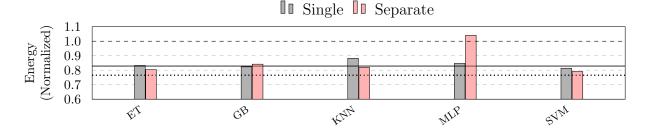

|    | 5.4.5 Using Separate Classifiers            | 02 |

|    | 5.4.6 Discussion of Results and Limitations | 03 |

| 6  | CONCLUSION                                  |    |

| A  | TOOLS FOR SELF-AWARE SYSTEMS RESEARCH       | 10 |

| В  | PUBLISHED CODE                              | 18 |

| ΒI | BLIOGRAPHY 1                                | 10 |

# LIST OF FIGURES

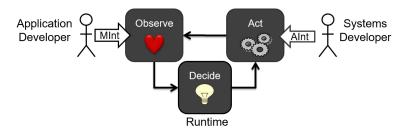

| 1.1         | A self-aware computing (SEEC) runtime model – observe, decide, and act                       | 3  |

|-------------|----------------------------------------------------------------------------------------------|----|

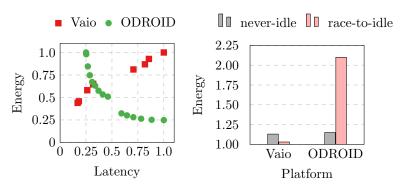

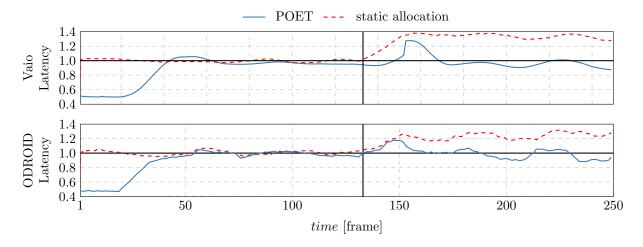

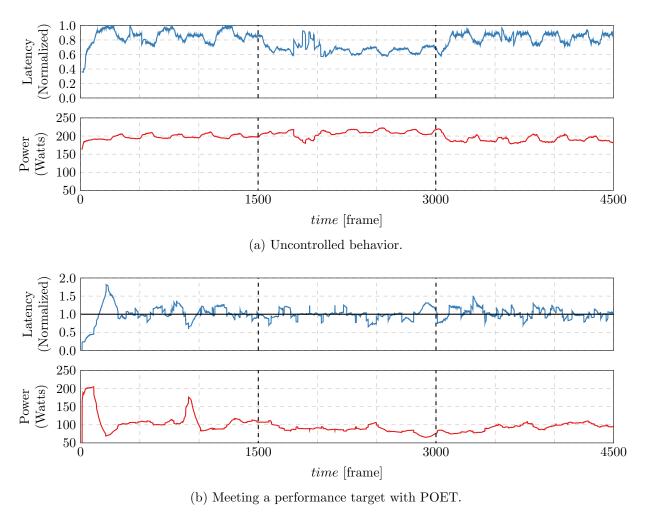

| 3.1         | Timing and energy behavior for encoding video on the Vaio and ODROID                         | 18 |

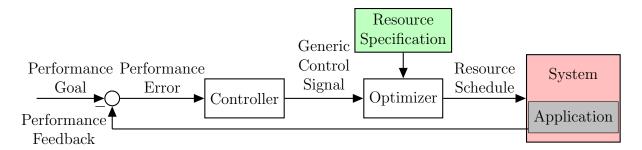

| 3.2         | Overview of the POET runtime                                                                 | 20 |

| 3.3         | Snippets of POET configuration files                                                         | 26 |

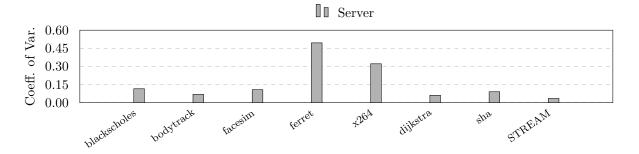

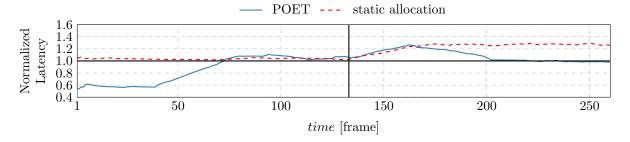

| 3.4         | Embedded systems application latency variability                                             | 32 |

| 3.5         | Server system application latency variability                                                | 33 |

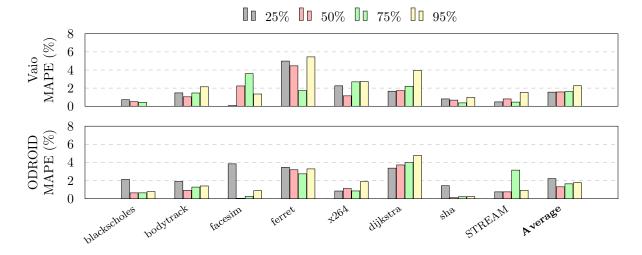

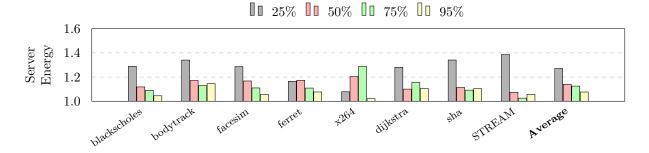

| 3.6         | Embedded systems latency error for different latency targets (lower is better, 0 is optimal) | 35 |

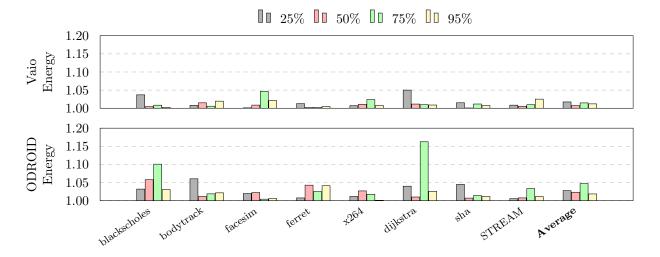

| 3.7         | Embedded systems energy consumption for different latency targets (lower is                  | 99 |

| 9.1         | better, 1 is optimal)                                                                        | 36 |

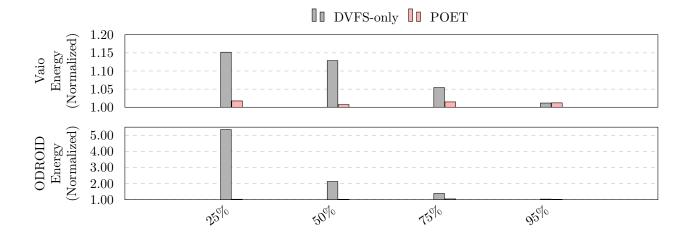

| 3.8         | Comparison of average energy consumption with DVFS-only versus POET (lower                   | 00 |

| <b>5.</b> 0 | is better, 1 is optimal)                                                                     | 37 |

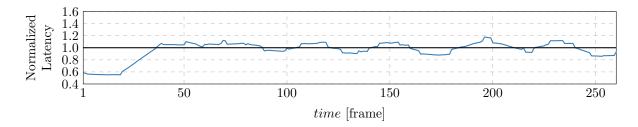

| 3.9         | Processing x264 input with distinct phases on embedded systems                               | 39 |

|             | POET adapting to a background application on embedded systems                                | 40 |

|             | Server system latency error for different latency targets (lower is better, 0 is             |    |

|             | optimal)                                                                                     | 41 |

| 3.12        | Server system energy consumption for different latency targets (lower is better,             |    |

|             | 1 is optimal)                                                                                | 42 |

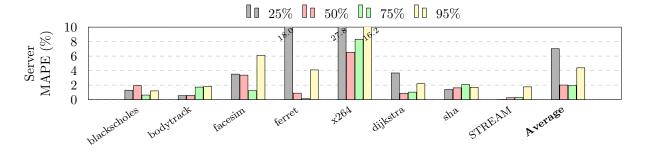

| 3.13        | Processing x264 input with distinct phases on a server system                                | 44 |

|             | POET adapting to a background application on a server system                                 | 45 |

| 3.15        | POET with insufficient window size                                                           | 46 |

| 3.16        | Snippets of Bard configuration files                                                         | 52 |

|             | Changing constraint from timing to power                                                     | 52 |

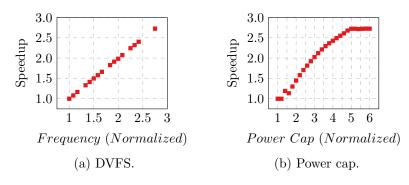

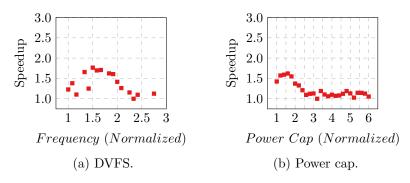

| 4.1         | DVFS and power cap performance impacts for vips                                              | 56 |

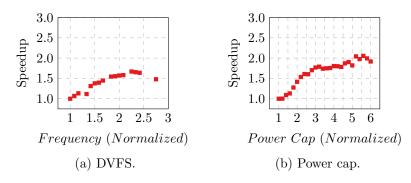

| 4.2         | DVFS and power capping with linear models                                                    | 57 |

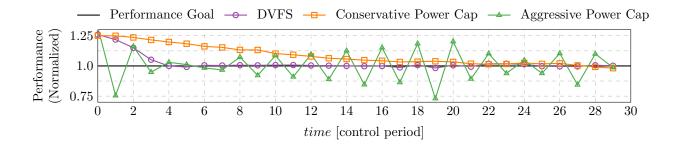

| 4.3         | CoPPer's feedback control design                                                             | 58 |

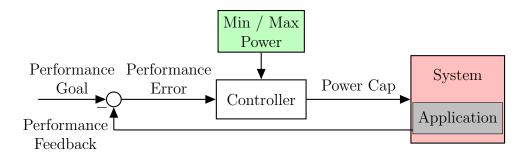

| 4.4         | DVFS and power cap performance impacts for HOP                                               | 60 |

| 4.5         | Application job performance variability.                                                     | 66 |

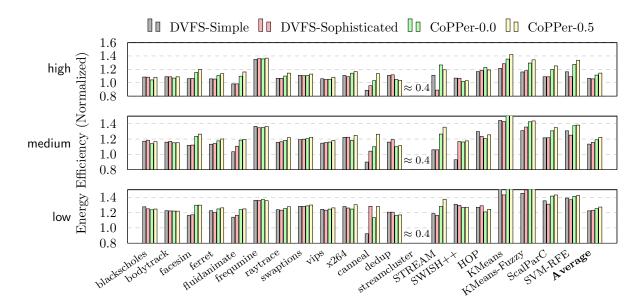

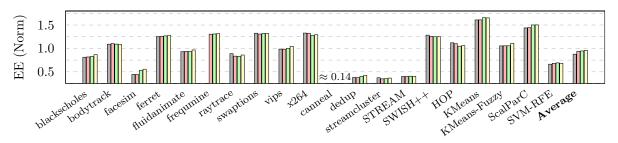

| 4.6         | Application energy efficiency for DVFS controllers and CoPPer, with and without              |    |

|             | a gain limit, for high, medium, and low performance targets (higher is better).              |    |

|             | Results are normalized to an ideal performance DVFS governor                                 | 71 |

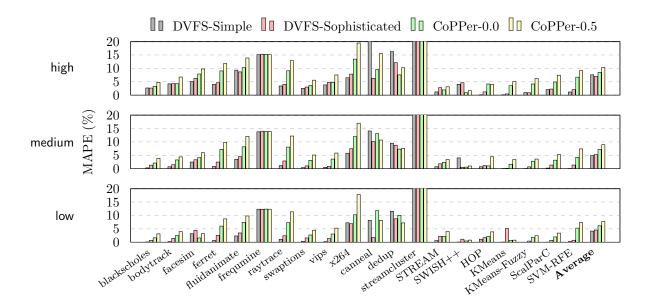

| 4.7         | Application performance error for DVFS controllers and CoPPer, with and with-                |    |

|             | out a gain limit, for for high, medium, and low performance targets (lower is                |    |

|             | better)                                                                                      | 72 |

| 4.8         | DVFS and power cap performance impacts for streamcluster                                     | 73 |

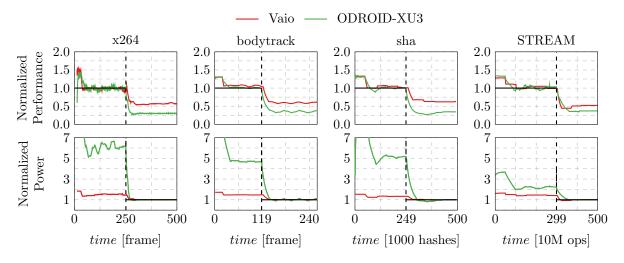

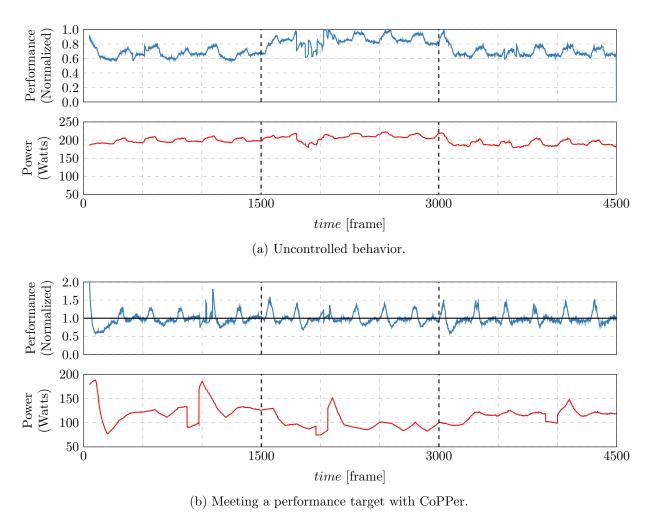

| 4.9         | Processing x264 input with distinct phases.                                                  | 76 |

| 4.10        | Application energy efficiency for DVFS controllers and CoPPer, with and without              |    |

|             | a gain limit, under interference by a second application (higher is better). Results         |    |

|             | are normalized to an ideal performance DVFS governor                                         | 78 |

| Application performance error for DVFS controllers and CoPPer, with and without a gain limit, under interference by a second application (lower is better) | 78                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

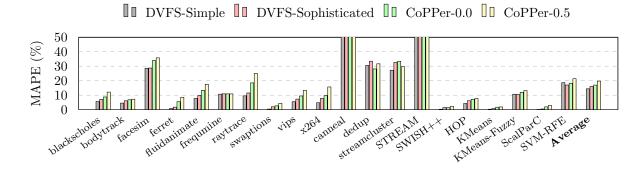

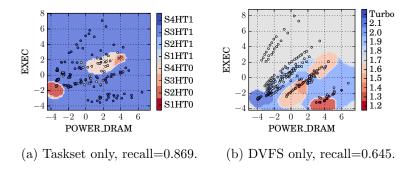

| Training data and learned decision boundaries for two SVM classifiers using two primary features.                                                          | 84                                                                             |

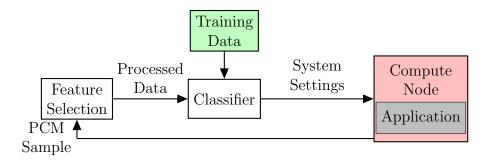

| Design for using machine learning classifiers to predict energy-efficient system settings based on performance counter behavior                            | 86                                                                             |

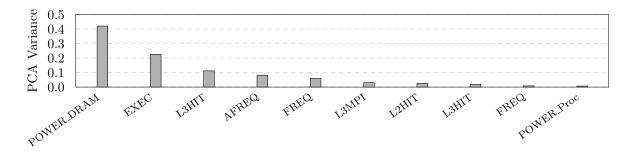

| PCA explained variance ratio for the top 10 performance counters, accounting for 99% of variance                                                           | 90                                                                             |

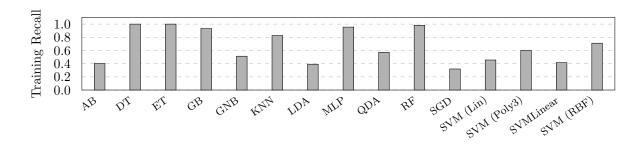

| Training data recall for 15 classification algorithms (higher is better, 1 is optimal).                                                                    | 92                                                                             |

|                                                                                                                                                            |                                                                                |

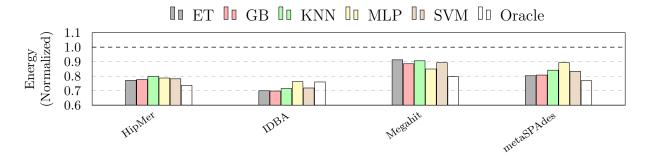

| - ,                                                                                                                                                        | 93                                                                             |

|                                                                                                                                                            | ~~                                                                             |

| • \ / /                                                                                                                                                    | 95                                                                             |

|                                                                                                                                                            | 96                                                                             |

| , and the second se                                             | 50                                                                             |

|                                                                                                                                                            | 97                                                                             |

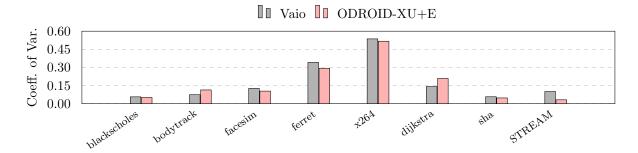

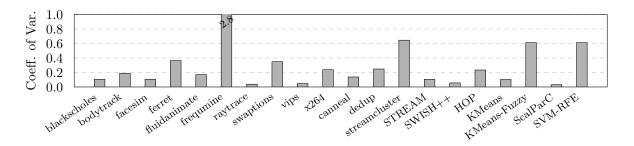

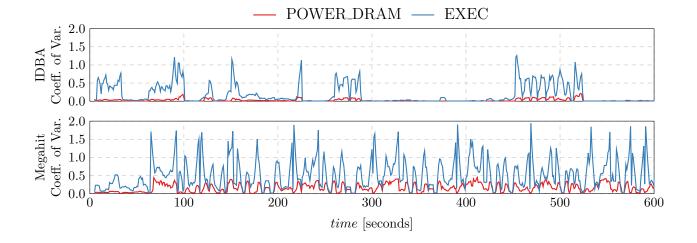

| Runtime coefficient of variation over a 5 second sliding window (lower values                                                                              |                                                                                |

| indicate more stable application behavior)                                                                                                                 | 99                                                                             |

| Training data and learned decision boundaries for SVM when classifying for                                                                                 |                                                                                |

| ı                                                                                                                                                          | 102                                                                            |

|                                                                                                                                                            |                                                                                |

| knobs (lower is better)                                                                                                                                    | 103                                                                            |

|                                                                                                                                                            | out a gain limit, under interference by a second application (lower is better) |

## LIST OF TABLES

| 3.1 | Two embedded platforms with different configurable components                     | 18  |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.2 | System power characteristics                                                      | 31  |

| 3.3 | Embedded systems evaluation inputs and configuration details                      | 32  |

| 3.4 | Server-class system evaluation inputs and configuration details                   | 33  |

| 4.1 | Application inputs and configuration details                                      | 67  |

| 4.2 | Energy efficiency of CoPPer with gain limits of 0.0 and 0.5 compared to the       |     |

|     | sophisticated DVFS controller (higher is better)                                  | 72  |

| 4.3 | Energy efficiency of CoPPer with gain limits of 0.0 and 0.5 compared to the       |     |

|     | sophisticated DVFS controller for memory-bound applications (higher is better).   | 74  |

| 4.4 | Average energy efficiency for unachievable performance targets, normalized to the |     |

|     | sophisticated DVFS controller                                                     | 75  |

| 5.1 | Overview of system-level performance counters                                     | 88  |

| 5.2 | Frequency of settings changes for ET classifier in the All configuration          | 99  |

| 5.3 | Classification runtime overheads                                                  | 100 |

| B.1 | Project code URLs                                                                 | 118 |

| B.2 | Tool code URLs                                                                    | 118 |

#### ACKNOWLEDGMENTS

There are so many people to thank, I cannot hope to list them all here.

My family... Your unwavering support, both before and during graduate school, made my endeavors possible. Through the ten years and living in five different states since college, time and distance have only heightened my appreciation for everything you have given me. Thank you.

Those who aided my journey getting here... Professor Michael Crowley at the University of Southern California, for a letter of recommendation five years after I graduated. My coworkers from Lockheed Martin, especially Gerald Nostrand for also writing a letter of recommendation.

My advisor, Professor Hank Hoffmann... Thanks for the exceptional mentoring and support, and for sending me *everywhere*, especially Portugal, Hong Kong, Greece, and France. I wish you could have joined in the global adventures, but thanks also for trusting me to "spread the gospel" and defend our work on my own. Now that you have tenure, my work here is done!

Others at the University of Chicago... Professors Andrew Chien and Haryadi Gunawi, for being on my Master's committee. Professor Shan Lu, for being on my doctoral dissertation committee. Nikita Mishra and David Kim, for collaborations and co-authorships. Huazhe (Harper) Zhang and Kevin Zhao, for helping with the grunt work. Ivana Marinčić, for being well-connected and helping me with my job hunt. The department technical and administrative staff, especially Bob Bartlett, Margaret Jaffey, Nita Yack, and Sandy Quarles—nothing would ever get done with you, you are all great!

Those who supported my research outside the university... Lars Bergstrom, for the summer position at Mozilla Research. Steve Hofmeyr, for research collaboration, hosting me at Lawrence Berkeley National Laboratory, and being on my dissertation committee. Our Proteus project collaborators at Rice, UT Austin, and MIT, especially Professors Krishna

Palem and Don Fussell.

Those providing support beyond research... Saeid Barati, for long chats, and for finding volleyball and softball groups where we can unwind, and sometimes even win. Rhys Povey (Physics), for organizing so many social events, barbecues, and our intramural volleyball team. Neville Eclov (Medical Physics), for having us on the Ionizers softball team and hosting classy parties in the off-season. Will Kong, Joe Wingerter, Kavon Farvardin, and Saeid Barati (again), for all the home brewing and other social activities. Roselyne Tchoua, for sharing in first-year struggles—it was nice having another adult to talk with! Gökalp Demirci, for casual drinks, and being the only one to show up for my first-year Thanksgiving potluck. Anne Farrell, for cookies, a bicycle, and impressively silent socialization. All the PSD Happy Hour regulars from the department, for banter over cheap pizza and beverages.

All members of Hank's group, past and present, especially those not yet mentioned but equally important to me—Zhixuan Zhou, Bernard Dickens, and Muhammad Husni Santriaji... Thanks for putting up with the sarcastic old guy in the room. I hope I managed to drop a little wisdom along the way—if you find it, I might need it back.

#### **ABSTRACT**

This dissertation addresses challenges in balancing performance and power/energy consumption in computing systems. Systems are often underutilized, meaning applications do not require all of a system's resources in order to achieve desired behavior, e.g., an application performance goal or reasonable system energy consumption. Modern systems expose knobs for tuning resources, like processor frequency or core allocation, which have a quantifiable impact on application performance and system power consumption. The result is a tradeoff space that can be navigated by resource schedulers to achieve desired behavior, sacrificing one dimension in favor of another, e.g., increased performance at the cost of increased power or energy consumption. The optimal knob settings required to achieve desired behavior depend on both the application and system, even changing during the course of execution as applications progress through different processing phases. The challenge in designing general and portable solutions to these problems arises from the diversity in both hardware and software systems.

We first address the problem of meeting application performance goals while minimizing energy consumption with two projects—POET and CoPPer. Both projects use control theory, which provides a formal framework for reasoning about dynamic systems, including convergence guarantees and robustness to model inaccuracies. In contrast, commonly used heuristic techniques cannot provide these guarantees, nor are they always portable. POET is a general solution that is portable between applications and systems—it is independent of different knob types and their allowable settings. POET produces resource schedules to exactly meet performance goals while achieving optimal energy consumption. CoPPer leverages recent power capping technology in place of software-managed Dynamic Voltage and Frequency Scaling (DVFS), which is being deprecated by hardware vendors. CoPPer overcomes challenges presented by the non-linear relationship between performance and power to meet performance goals while leaving the energy optimization to hardware, which responds

more rapidly to changes in application resource requirements than software.

Finally, we address the problem of optimizing energy efficiency to minimize the execution cost of running applications with the CEES project. CEES uses machine learning classifiers, driven by low-level hardware performance counters, to predict the most energy-efficient knob settings at runtime based on current application resource utilization. By using performance counters, no application modifications are necessary. We evaluate this approach in the High Performance Computing (HPC) domain, more aggressively trading performance for energy savings than has historically been done, reducing the cost of scientific insight. Extrapolating from empirical single-node performance and power results, scaling the solution to hardware over-provisioned, power-constrained clusters could increase total cluster throughput by up to 24%.

The three projects presented in this dissertation dynamically adapt to changing application and system behavior at runtime, and are thus able to provide more optimal results than commonly used static resource scheduling techniques. Furthermore, the project designs are independent of particular applications and systems, making them portable to a wide range of computing platforms.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Thesis Statement

This dissertation explores two problems in balancing software performance and system energy consumption in computing systems: (1) meeting application performance goals while minimizing energy consumption, and (2) running applications as energy-efficiently as possible. We address the first problem using control theory to meet performance goals by tuning system knobs such as DVFS frequencies, core allocations, and hardware power caps. We treat the second as a classification problem, using machine learning classifiers, driven by low-level hardware counter metrics, to predict the most energy-efficient system knob settings at runtime.

#### 1.2 Problem Description

Performance and energy consumption are conflicting goals in computing systems and must be appropriately balanced to satisfy user requirements. As power and energy become first-class concerns in systems ranging from low-power embedded platforms to large-scale High Performance Computing (HPC) environments, there is an increasing need for software to manage hardware resource allocations to achieve a desirable balance in performance and power/energy consumption. Fortunately, modern systems expose knobs to support trading performance and power.

For example, Dynamic Voltage and Frequency Scaling (DVFS) trades processor clock rate and power consumption for changes in throughput, and is ubiquitous in modern systems. Dynamic power P is proportional to the effective capacitance C of a processor, the applied

voltage V, and the clock frequency f [49]:

$$P \propto \frac{1}{2}CV^2f \tag{1.1}$$

Higher clock frequencies typically result in higher performance, e.g., for compute-bound applications. However, voltage and frequency are correlated, meaning their values in Equation 1.1 cannot be adjusted independently [79]. Higher clock frequencies require higher voltage to maintain stable circuit operation; conversely, lower frequencies can maintain operation at lower voltages. Reducing the voltage and frequency can offer significant power savings due to this non-linear relationship. Newer technologies allow specifying power caps for hardware resources and letting the components optimize their own behavior subject to the power constraint, e.g., Intel's Running Average Power Limit (RAPL) tunes DVFS much faster than software [25]. Another common knob setting is the allocation of compute cores on multicore systems, allowing unallocated cores to enter low-power sleep states, or even shut down altogether to save power/energy.

If we consider each allowable combination of knob values to be a system setting or configuration, we can explore the impact of different knob combinations on performance and power consumption. Therefore, to understand the behavior of a particular application on a system, we can perform a characterization by testing the application in each system configuration and recording the behavior. The result is a tradeoff space, where each system configuration produces unique application performance and system power values. Often only a subset of the available configurations are actually desirable—it is straightforward to derive the Pareto-optimal configurations, or even those that lie on the (upper or lower) convex hull of the tradeoff space.

A significant amount of software is subject to performance requirements. Power or energy can then be optimized under the performance constraint to increase battery life or reduce power costs. Until recently, heuristic approaches were often sufficient to meet performance

Figure 1.1: A self-aware computing (SEEC) runtime model – observe, decide, and act.

goals while achieving near-minimal energy consumption. However, heuristic approaches to balancing performance and power/energy rely on assumptions about the performance/power tradeoff space of an application and system that we have found are not portable between applications and modern systems. For example, the classic race-to-idle heuristic can achieve low energy consumption on one system, but high energy consumption on another compared with a pace-to-idle or never-idle approach [61]. While performance/power tradeoff spaces were mostly linear on older systems, advances in technology are making them more convex on modern systems. An important observation by Kim et al. is, "Unless the function of a given machine is a straight line originating from the idle state,  $(0, P_{idle})$ , an idling heuristic is never optimal for all instances" [73]. In short, the more convex the tradeoff space, the further from optimal any idling approach is.

A more optimal tradeoff in balancing performance and power is to maximize energy efficiency, i.e., the amount of work completed per unit of energy consumed (analogous to maximizing the ratio of performance to power). Sometimes it is desirable simply to reduce the energy cost of a computation at the expense of slower execution. In the High Performance Computing (HPC) domain, maximizing energy efficiency can maximize the throughput of power-constrained, hardware over-provisioned clusters [104]. As with meeting performance goals, a similar problem with heuristics arises—the optimal approach varies between applications and systems.

The lack of both portability and optimality of heuristics demand that we develop more general approaches to addressing the problems in balancing performance and power/energy.

In his PhD dissertation, Hoffmann proposes a "self-aware" computing model (SEEC) that uses a closed-loop feedback design to observe, decide, and act [54]. Figure 1.1 demonstrates this concept. The SEEC model is more portable than many heuristics because it includes an observation step that measures behavior at runtime rather than relying strictly on assumptions made offline. We build on this high-level model and use feedback systems that measure application and system behavior during runtime to make informed changes to resource allocations as new information becomes available. Furthermore, our general feedback system designs do not depend on extremely accurate or complete models. Instead, they rely on runtime measurements to fine-tune their decisions.

#### 1.3 Contributions

This dissertation addresses two common goals in managing software performance and system energy consumption. The first is the constrained optimization problem of meeting an application performance goal while minimizing energy consumption. Software performance constraints are common in applications that run on platforms ranging from embedded to server-class. The second addresses the problem of running software as energy-efficiently as possible, *i.e.*, maximizing the ratio of work completed to energy consumed. We address these two problems with three distinct projects:

- POET, the Performance with Optimal Energy Toolkit: A portable, control-theoretic framework for meeting soft application performance goals while optimizing energy consumption, which we demonstrate by tuning DVFS settings and core allocations.

- CoPPer, Control Performance with Power: A model-free, control-theoretic approach for meeting soft application performance constraints by tuning processor power caps and allowing the hardware to optimize energy consumption.

- CEES, Classification of Energy-efficient Settings: A machine learning classification framework for predicting energy-efficient system settings based on low-level hardware

performance counter metrics, which we demonstrate by tuning DVFS, socket allocations, and the use of HyperThreads.

Appendix A describes portable tools created to support these projects that we believe are useful to other researchers and developers. Appendix B provides open-source release information for POET, CoPPer, and supporting tools.

#### 1.3.1 POET

POET addresses the problem of meeting soft real-time application performance goals while minimizing energy consumption. A significant amount of software is subject to performance constraints, from applications running on low-power embedded platforms to those in high-performance, high-power environments like on servers in datacenters. Optimizing energy consumption increases the usable runtime of battery-powered systems like tablets, smart-phones, and smaller devices we now classify as Internet of Things; for always-on devices, it reduces the runtime energy costs.

Kim et al. prove that an optimal solution to this constrained optimization problem requires, at most, two system configurations from the convex hull of the tradeoff space [73]. POET uses control theory to meet the performance goal and linear optimization to select the optimal pair of system configurations that satisfy the performance constraint. While POET was originally designed for embedded systems [63], we later evaluated it on a server-class system [64].

POET's evaluation uses DVFS and core allocation as the system knobs to control performance and energy consumption. While significant prior work has used these knobs, their solutions tend to be restricted to particular applications and systems, limiting their portability. In contrast, POET's design is independent of any particular application or platform and their performance/power tradeoff spaces.

We find that POET achieves:

- Ease of Use: Integrating POET with applications only requires a few additional lines of code.

- **Predictable Performance**: POET meets a range of performance targets, minimizing the error between the goal and the achieved performance.

- Energy Savings: Using an offline oracle, we verify that POET achieves near-optimal energy consumption (e.g., 1.3% over optimal on an Intel-powered tablet, 2.9% on an ARM big.LITTLE system), which includes POET's runtime overhead.

- Adaptability: POET adapts to phases in application and input behavior, achieving increased energy savings during periods of low computational demand. Additionally, POET adapts to noise in the system introduced by co-scheduled applications to ensure that performance goals are still met when feasible, and makes a best effort otherwise.

#### 1.3.2 CoPPer

CoPPer also addresses the problem of optimizing energy consumption under a soft performance constraint, but does so by tuning hardware power caps. Recent trends suggest that software control of DVFS is being deprecated, making all prior software approaches that depend on DVFS obsolete. Linux kernel developers have acknowledged this trend [108]. In fact, the Linux kernel documentation notes, "the idea that frequency can be set to a single frequency is fictional for Intel Core processors. Even if the scaling driver selects a single P-State, the actual frequency the processor will run at is selected by the processor itself" [33].

However, hardware is not aware of application-level performance requirements, so a software component is still needed to ensure that performance constraints are respected. Fortunately, emerging interfaces let software set *power caps* on hardware, with hardware free to determine what DVFS frequencies should be used and when, so long as the average power over some time window is respected. For example, Intel's Running Average Power Limit (RAPL) allows software to set power limits on hardware [25]. This poses a new challenge. Meeting performance constraints with DVFS is easy: simple linear models map changes in processor clock frequency to changes in application performance. Meeting performance requirements with power capping is harder: power and speedup have a non-linear relationship (Equation 1.1) and most applications exhibit diminishing performance returns with increasing clock frequency (and thus power), *i.e.*, are not entirely compute-bound.

CoPPer proposes to leverage hardware power capping to control performance, leaving the energy optimization to the hardware. Its evaluation uses Intel RAPL, which manages DVFS in hardware at finer-grained intervals than software can, while strictly respecting the imposed power limit. CoPPer makes the following contributions:

- Demonstrates the need for a DVFS alternative that allows software to manage performance/power tradeoffs.

- Proposes software-defined power capping as a replacement for software-managed DVFS.

- Presents CoPPer, a feedback controller that meets performance goals by manipulating hardware power caps, handles non-linearity in power cap/performance tradeoffs, and introduces adaptive gain limits to further reduce power when it does not increase performance.

- Evaluates CoPPer using Intel RAPL on a dual-socket, 32-core server. We find that CoPPer achieves performance guarantees similar to software DVFS control, but with better energy efficiency. Specifically, CoPPer improves energy efficiency by 6% on average with a 12% improvement for memory-bound applications. At the highest performance targets, CoPPer's gain limit saves even more energy: 8% on average and 18% for memory-bound applications.

#### 1.3.3 CEES

In other scenarios, it is desirable to maximize energy efficiency, *i.e.*, complete a fixed-size computation using the least energy possible without a performance constraint. It is becoming well-established that the *race-to-idle* heuristic is not energy-efficient. It may then seem reasonable to simply run in the lowest-power system configuration, but this approach fails to account for elapsed time, so energy consumption may still exceed optimal even when consuming low power. Identifying the most energy-efficient system setting is challenging since the optimal setting varies depending on varying application resource demands.

We address this problem in the High Performance Computing (HPC) domain. It has historically been desirable in HPC to run software as fast as possible. The motivation behind this approach is either to: (1) get an answer to a scientific question as fast as possible, or (2) for the HPC cluster to complete as much work as possible, *i.e.*, maximize the cluster throughput. The goal of completing an application as fast as possible leaves little room for power/energy optimization, although some work has been done in this area (see Chapter 2). Until recently, maximizing application performance also solved the latter problem. Now we are moving toward the era of exascale systems with strict power budgets [74]. Hardware over-provisioning, which allows more systems to operate in a cluster than can actually be supported if each were consuming their maximum power budget, has been proposed as an approach to improve cluster throughput [104]. It works because systems do not usually require their maximum allowable power budget. In these new hardware over-provisioned, power-constrained clusters, maximizing energy efficiency instead of application performance will both decrease the cost of per-application scientific insight and maximize the throughput of the cluster.

Our solution is to treat this challenge as a classification problem, using samples from low-level hardware performance counters to drive machine learning algorithms that predict the most energy-efficient configuration to use. This approach does not require the software to provide its own instrumentation, nor does the classifier need to know anything about the application in advance. Using classification instead of estimation reduces the computational overhead of the software solution, at the cost of less insight into the resource predictor's decision. We tune DVFS, socket allocation, and the use of HyperThreads.

This work makes the following contributions:

- Proposes optimizing *energy efficiency* instead of *runtime* to decrease the cost of scientific computation.

- Establishes the problem complexity—of 15 different machine learning classification techniques evaluated, only some are suitable for optimizing energy efficiency.

- Demonstrates that sufficiently powerful classifiers can dramatically reduce energy consumption by accurately predicting energy-efficient system settings at runtime.

- Extrapolates from empirical results to posit that optimizing energy efficiency can improve the throughput of hardware over-provisioned, power-constrained systems by up to 24%.

#### CHAPTER 2

#### RELATED WORK

This chapter discusses work related to performance, power, and energy awareness. We first discuss work relating to POET and CoPPer—meeting performance constraints and optimizing energy consumption. We then discuss power and energy-aware work in the High Performance Computing domain, where trading performance for power/energy savings is less common. Finally, we describe research projects by other researchers that build off work in this dissertation.

#### 2.1 Timing Constraints and Energy Awareness

Computing systems are often underutilized, leading to significant portions of time where application performance requirements can be met using less than the full system capacity [9, 95]. This trend has led to flourishing scheduling research that tailors resource usage to meet performance requirements, often while optimizing another dimension like power or energy consumption. Modern systems expose a variety of configurable resources, which energy-aware schedulers can tune to adjust performance and power behavior. This flexibility allows the system to adapt to different circumstances or different application needs, but also increases software complexity. The problem is exacerbated when approaches must achieve portability across a range of different systems, which expose different resources to software and exhibit diverse performance/power tradeoffs.

Software-based DVFS management is essential for many energy-aware scheduling algorithms [4, 75, 137]. At the processor level, DVFS has been used to meet performance requirements [88, 134] and implement power capping [81]. Allowing DVFS to be set separately on different cores provides further benefits [69, 113]. Similarly, managing DRAM DVFS increases energy efficiency [29, 31]. Recent survey papers devote entire sections to

the various ways DVFS has been used in scheduling systems [98, 142]. In modern multicore systems, allocating a subset of cores and sockets (with aggressive clock-gating to save power) is also common, and more recently comes with the additional challenge of scheduling for heterogeneous architectures [107].

One simple heuristic for minimizing energy is race-to-idle, which allocates all resources until a job completes and then idles the system until the next job arrives [9]. This heuristic is portable since it does not require knowledge about the system, but empirical studies show that it is not optimal [9, 22, 136, 138]. Kim et al. demonstrate that an optimal solution requires knowledge of how the different configurable resources in a system affect the specific application under control—information which race-to-idle does not use [73]. The same study shows that race-to-idle is dominated by a pace-to-idle heuristic, i.e., pace-to-idle is theoretically never worse than race-to-idle and can be much better.

It is not surprising that a number of different frameworks have arisen for intelligently controlling multiple resources to minimize energy. Many empirical studies have shown that it is more energy-efficient to coordinate multiple resources than to manage any one alone [9, 22, 136, 138]. Examples include systems that coordinate DVFS with core usage [23, 91, 114], coordination of processor and DRAM DVFS [21, 28, 38, 84], and DVFS with thread scheduling [113, 133]. Several other approaches coordinate processor-wide DVFS with adaptations to the memory system and processor pipeline [15, 35, 120]. For example, Dubach et al. coordinate several microarchitectural features [35], Petrucci et al. coordinate thread scheduling and the use of heterogeneous cores [107], while Maggio et al. coordinate core allocation and clock speed [91]. Bertini et al. coordinate tiers of a multi-tier webserver for e-commerce [13]. AbouGhazaleh et al. coordinate the speed of the processor and cache [1], while Yun et al. also coordinate the speeds of multiple on-chip components [138]. Liu et al. coordinate job scheduling and clock speed on clusters [87]. Bitirgen et al. coordinate clock speed, cache, and memory bandwidth in a multicore [15]. The METE system manages

clock speed, memory bandwidth, and core usage [120]. Sinangil et al. co-design a processor architecture which exposes both monitoring and configurable resources with an operating system that dynamically manages those resources [122]. All of these approaches coordinate multiple resources, but do so using system-specific implementations, e.g., METE's controller would have to be redesigned to work with Bitirgen et al.'s architecture.

Other frameworks have been proposed to meet real-time constraints by managing multiple resources. These approaches are typically implemented as middleware that take a specification of available resources and a performance goal, and then meet that goal. Rajkumar et al. propose a general framework (with system-specific implementation) for allocating resources to achieve real-time requirements, but this approach is not energy-aware [112]. Sojka et al. propose a portable middleware layer for allocating resources to meet soft real-time constraints, but this system does not minimize energy [123]. ControlWare is another middleware approach that uses control theory to meet quality-of-service constraints, but does not address energy concerns [140].

These approaches provide portable real-time guarantees, which is itself a hard problem, but they do not provide energy savings. LEO is a machine learning system that can meet performance constraints with minimal energy consumption [97]. LEO is very accurate and provides high energy savings, even with no prior knowledge of the application currently running. Its approach is extremely portable, but also incurs very high overhead. Interestingly, LEO and POET have complementary weaknesses—POET has low runtime overhead, but requires prior knowledge in the form of a configuration model while LEO has high overhead, but requires no prior knowledge. Follow-up work to LEO addressed this issue with CALOREE (discussed further in Chapter 2.3) [96]. PTRADE also uses control theory to manage general collections of resources [58], and is perhaps the most similar to POET. PTRADE minimizes power consumption, but not necessarily energy. In addition, PTRADE uses heuristic optimizations, which are not portable, while POET uses a true minimal-energy

scheduling algorithm.

We also note two approaches that are complementary to POET. Zhao et al. manage processor speed to meet both reliability and timing constraints with minimal energy [141]. This problem is complicated by the effect DVFS scaling has on hardware reliability. It is possible that POET's general approach to resources other than DVFS might allow additional energy savings if incorporated in Zhao et al.'s work. He et al. propose adaptive energy management in the power circuitry itself to meet timing constraints while adapting the delivered energy to increase battery efficiency [47]. It is possible that combining POET's runtime-level resource management with this supply-level approach would further increase efficiency.

In the time since POET and CoPPer were developed, more recent works have focused on making it easier to create and use self-adaptive systems. Filieri et al. discuss a general approach to the controller design process [41] while Maggio et al. describe automatic methods for generating multiple-input multiple-output (MIMO) controllers [92]. Recent works leverage MIMO controllers to efficiently use system resources [109, 111] and could even be combined with approaches like CoPPer. Furthermore, software-level knobs (instead of system-level) are becoming more common. While the concept is not new, it still seems to be in its infancy—Shevtsov et al. perform a systematic literature review on software self-adaptation in order to outline current challenges and begin to generalize approaches [121]. One such general approach is SmartConf, which automatically adjusts software knobs to meet performance-sensitive application configurations and provide other optimizations [130].

## 2.2 High Performance Computing

Power and energy in HPC systems is a growing concern, though prior work in the area has often not allowed trading performance for power or energy savings. For example, Adagio uses DVFS to save energy with less than 1% increase in runtime [116]. Other work depends

on accurate prediction of a code's critical path to reduce power where it will not slow down an application [70, 93]. Patki et al. propose to better utilize available power with hardware over-provisioning to increase total system throughput [104]. Sarood et al. have shown similar results: hardware over-provisioning increases performance given a power cap [118]. Hardware over-provisioning acknowledges that compute resources are no longer the primary factor limiting cluster size—power is—allowing us to more aggressively trade performance and power/energy consumption.

Other works demonstrate that low-level hardware performance counters can drive solutions for modeling and improving power/energy consumption [85, 119, 128, 135]. Using Dynamic Concurrency Throttling and DVFS to reduce energy consumption without performance loss, Curtis-Maury et al. use hardware events to create an energy-aware logistic regression model for predicting performance and power [24].

As the number of system settings increases and their interaction becomes more complicated, several approaches have turned to machine learning to manage them. Paragon [26] and Quasar [27] guarantee quality-of-service constraints in heterogeneous data centers using a scheduler based on the learning system that won the Netflix prize [10]. LEO (mentioned previously) uses a Hierarchical Bayesian Model to minimize energy for different system utilization requirements [97]. These approaches all estimate the performance and power of every possible system configuration, then search those estimates to find the best configuration that meets their operating constraints. The need to estimate every configuration's behavior is expensive, requiring half a second [97] to several seconds [26] of overhead. In contrast, our proposed classification approach simply returns the best system settings without predicting their actual energy efficiency, which requires orders of magnitude less overhead. Ferroni et al. use classification based on hardware events to select the best power model for an application from a predetermined set, and then assign resources to that application in a multi-tenant virtualized infrastructure [39]. This approach and our proposed approach are complementary,

in that Ferroni et al. assign nodes as resources, while our proposed approach can fine-tune resource usage within a node.

Our approach for maximizing energy efficiency is most closely related to other node-level approaches for managing performance and energy. PUPiL maximizes node performance given a power cap by adjusting system settings to the particular needs of an application [139]. Chasapis et al. maximize performance for power-capped NUMA nodes by recognizing the effect that manufacturing variability can have on individual core performance [20]. Both of these approaches maximize performance for a given power constraint, but neither is capable of minimizing energy, which requires changing both power and performance. ParallelismDial is a node-level approach for managing application-level parallelism to increase energy efficiency [124]. ParallelismDial has similar goals to our proposed approach, but they are complementary—it works at the application level, while our approach operates at the system level. In future work, it would likely be beneficial to combine the two to further reduce overhead and improve energy savings.

#### 2.3 Inspired Projects

Research in this dissertation, and POET in particular, has been used as the foundation for projects by other researchers.

Farrell and Hoffmann build on POET to create MEANTIME, which provides hard realtime guarantees instead of soft performance guarantees [36]. They use the concept of approximate computing to tune application accuracy when their runtime determines that a performance constraint may not be met. The approach usually only requires small changes to application accuracy, e.g., peak signal-to-noise ratio and the bitrate of a video encoder, while still tuning system-level knobs, like in POET, to save energy.

Aforementioned work by Mishra et al. combines POET with machine learning in a project called CALOREE, which reduces the amount of offline work needed to generate the controller's resource specification [96]. CALOREE uses transfer learning, taking information from both previously seen applications and the current application, to model how interacting resources affect the current application's speedup. It then makes online updates to the controller's resource specification and pole value using more accurate models.

POET and follow-on work called Bard were also the starting point in an ongoing project called Proteus. Proteus is developing the FAST programming language which allows programmers to provide *intent specifications* that instruct the runtime about desired constraints and optimizations. FAST satisfies these intents by tuning both application and system knobs, e.g., to manage application performance, application accuracy, and system power or energy consumption.

#### CHAPTER 3

# POET: THE PERFORMANCE WITH OPTIMAL ENERGY TOOLKIT

This chapter describes POET (the Performance with Optimal Energy Toolkit). Chapter 2 discussed existing work in managing performance and power/energy awareness. Like POET, a number of these approaches use feedback control to manage timing constraints [13, 43, 55, 58, 82, 84, 90, 91, 129, 140]. POET is most related to prior approaches that abstract resource management into a middleware or runtime [58, 112, 123, 140]. POET uses control techniques, which provide a formal framework for reasoning about the dynamic behavior of systems. POET is unique in its design for portability, its energy awareness, and the incorporation of a true minimal-energy resource allocation algorithm.

#### 3.1 Motivation

To motivate the need for POET, we summarize prior work [61]. We evaluate timing and energy tradeoffs on two embedded platforms: a Sony Vaio SVT11226CXB tablet system with an Intel Haswell processor and an ODROID-XU+E ARM big.LITTLE development board. The two platforms have: (1) different configurable resources for performance/power management, and (2) timing/energy tradeoffs with different topologies. Resource allocation strategies that save energy on one are wasteful on the other.

Table 3.1 presents each system's configurable resources. The Vaio allows configuring the number of active cores, the use of HyperThreads, processor clock speed, and the use of TurboBoost. The ODROID supports configuring the number of active cores, whether the application uses the "big" (Cortex-A15 high-performance, high-power) or "LITTLE" (Cortex-A7 low-performance, low-power) cores, and the independent clock speeds of the big and LITTLE clusters.

Table 3.1: Two embedded platforms with different configurable components.

| Platform    | Processor      | Cores | Core Types  | Speeds (GHz)             | TurboBoost | HyperThreads | Num. Configs |

|-------------|----------------|-------|-------------|--------------------------|------------|--------------|--------------|

| SVT11226CXB | Intel Haswell  | 2     | 1           | 0.6-1.5                  | yes        | yes          | 46           |

| ODROID-XU+E | ARM big.LITTLE | 8     | 2 (A15, A7) | $0.8 - 1.6, \ 0.5 - 1.2$ | no         | no           | 70           |

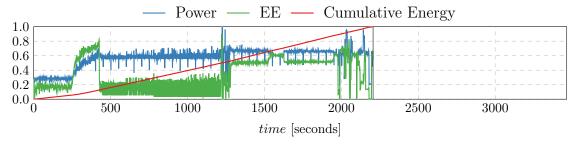

(a) Latency/Energy tradeoffs. (b) Heuristic energy consumption.

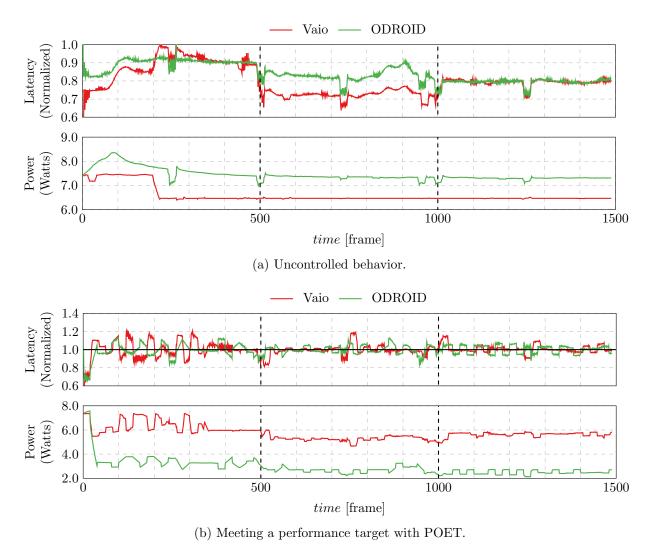

Figure 3.1: Timing and energy behavior for encoding video on the Vaio and ODROID.

Our example features a video encoder, composed of jobs, where each job encodes a frame. We instrument the encoder to report the latency and platform energy consumption for each job. Figure 3.1a shows the tradeoffs between job latency and system energy consumption for each platform, where each point represents the average behavior of a different configuration. The x-axis shows latency, normalized to 1—the empirically determined worst case. The y-axis shows energy, normalized to 1—the highest measured energy. The tradeoffs are obviously very different for the Vaio and the ODROID. For the Vaio, energy increases as frame latency increases; *i.e.*, a slower job wastes energy. For the ODROID, energy decreases as frame latency increases; *i.e.*, slower encodings save energy.

The different shapes of these tradeoff spaces lead to different optimal resource allocation strategies. Empirical studies show that the *race-to-idle* heuristic, which makes all resources available and then idles after completing a job, is near-optimal on systems like the Vaio [9, 52, 53, 61, 99]. On systems like the ODROID, recent approaches save energy by keeping the system constantly busy, like the *never-idle* heuristic [19, 53, 61, 80, 86].

To demonstrate the importance of choosing the right strategy, we analyze the two heuris-

tics on both platforms and compare their energy consumption to optimal (found by measuring every possible resource configuration). We set a latency target equal to twice the minimum latency and measure the energy consumption of encoding 500 video frames using each heuristic. Figure 3.1b shows the results, normalized to optimal. Both heuristics meet the latency target, but their energy consumptions vary tremendously. On the Vaio, race-to-idle is near-optimal, but never-idle consumes 13% more energy. Conversely, never-idle is near-optimal for the ODROID, but race-to-idle consumes 2× more energy.

These results demonstrate that resource allocation strategy greatly affects energy consumption, and more importantly, that heuristic solutions are not portable across systems. These two points motivate the need for an approach like POET, which provides near-optimal resource allocation while remaining platform-independent.

#### 3.2 General and Portable Resource Allocation

The goal of POET's resource allocation framework is twofold. First, it must provide predictable timing so application jobs meet their deadlines. Second, it should minimize energy consumption given the timing requirement. While these two subproblems are intrinsically connected, they can be decoupled to provide a general solution. The complexity arises from the need to keep resource allocation general with respect to the running application and the hardware platform. We tackle the problem of providing predictable timing using control theory by computing a generic control signal. Using the computed control signal, we then solve the energy minimization problem using mathematical optimization.

Figure 3.2 illustrates our approach. The **application** informs the runtime of its job performance goal. Measuring each job start and completion time (performance feedback), POET's runtime computes the performance error and passes it to the **controller**. The controller uses the error to calculate a generic control signal, indicating how much the application speed should be altered. This signal is used by the **optimizer**, together with the

Figure 3.2: Overview of the POET runtime.

resource specification, to produce a resource schedule that achieves the desired performance goal while minimizing energy consumption. Both the controller and the optimizer are designed independently of any particular application and system. The only assumption made is that applications are composed of repeated jobs with a soft real-time performance goal.

#### 3.2.1 Controller

The application provides a performance goal (work rate)  $R_{ref}$ , which is easily computed from a workload size (number of jobs)  $\omega$  and desired latency goal (deadline)  $\tau$  for those  $\omega$  jobs:

$$R_{ref} = \frac{\omega}{\tau} \tag{3.1}$$

The controller cancels the error between the desired performance,  $R_{ref}$ , and the measured performance,  $r_m(t)$ , which it models as:

$$r_m(t) = s(t-1) \cdot b_r(t-1)$$

(3.2)

The error  $e_r(t)$  is then easily computed as:

$$e_r(t) = R_{ref} - r_m(t) \tag{3.3}$$

The controller performs its calculations at discrete work (job) intervals to produce a new desired speedup, s(t), implementing the *integral control law* [48]:

$$s(t) = s(t-1) + (1-\alpha) \cdot \frac{e_r(t)}{b_r(t)}$$

(3.4)

where  $\alpha$  is a *pole* of the closed loop characteristic equation [40] such that  $\alpha$  lies within the unit circle:

$$0 \le \alpha < 1 \tag{3.5}$$

The pole is configurable. Small  $\alpha$  values make the controller highly reactive, while large values make it slow to respond to external changes. However, a large  $\alpha$  ensures robustness with respect to transient fluctuations and may be beneficial for very noisy systems. A small  $\alpha$  will cause the controller to react quickly, potentially producing a noisy control signal.

The parameter  $b_r(t)$  represents the application's base speed, which directly influences the controller. Different applications will have different base speeds. Applications may also experience *phases*, where base speed changes over time. To accommodate these situations, POET continually estimates base speed using a Kalman filter [131], which adapts  $b_r(t)$  of Equation 3.4 to the current application behavior. Assuming minimal measurement variance (*i.e.*, even if an application is noisy, the signaling framework does not add additional noise) and denoting the application timing variance as  $q_b(t)$ , the Kalman filter formulation is standard:

$$\begin{cases}

\hat{b}^{-}(t) &= \hat{b}(t-1) \\

e_{b}^{-}(t) &= e_{b}(t-1) + q_{b}(t) \\

k_{b}(t) &= \frac{e_{b}^{-}(t) \cdot s(t)}{[s(t)]^{2} \cdot e_{b}^{-}(t)} \\

\hat{b}(t) &= \hat{b}^{-}(t) + k_{b}(t) \left[ r_{m}(t) - s(t) \cdot \hat{b}^{-}(t) \right] \\

e_{b}(t) &= \left[ 1 - k_{b}(t) \cdot s(t-1) \right] e_{b}^{-}(t)

\end{cases} (3.6)$$

This formulates Kalman gain for job latency as  $k_b(t)$ , the a priori and a posteriori estimates

of the base speed as  $\hat{b}^-(t)$  and  $\hat{b}(t)$ , and the *a priori* and *a posteriori* estimates of the error variance as  $e_b^-(t)$  and  $e_b(t)$ . The Kalman filter produces a statistically optimal estimate of the system's parameters and is provably exponentially convergent [18].

Unlike prior work, the POET controller does not reason about a particular set of resources, but computes a generic control signal s(t). The advantage of using the Kalman filter is that POET's formulation is independent of particular applications and systems. POET provides formal guarantees about its steady-state convergence and robustness without requiring users to understand control theory or Kalman filtering—s(t) is computed by the controller,  $r_m(t)$  and  $q_b(t)$  are measured, and all other parameters are derived.

#### 3.2.2 Optimizer

The optimizer turns the generic control signal computed by the controller into a systemspecific resource allocation strategy, translating the speedup s(t) computed with Equation 3.4 into a *schedule* for the available resources. The *schedule* is computed for the next  $\omega$  work units (jobs).

As shown in Figure 3.2, the optimizer takes, as input, a resource specification containing the set of available system configurations. There are C possible configurations in the system and by convention, we number the configurations from 0 to C-1. We use c=0 to indicate the configuration where the least amount of resources is given to the application. In contrast, configuration C-1 maximizes the resource availability. Each configuration c is associated with performance and power values, speedup  $s_c$  and powerup  $p_c$  respectively, which are normalized to c=0.

Given this information, POET solves the following optimization problem:

minimize

$$\sum_{c=0}^{C-1} \tau_c \cdot p_c$$

$$s.t. \quad \sum_{c=0}^{C-1} \tau_c \cdot s_c \cdot b_r(t) = \omega$$

$$(3.7)$$

$$s.t. \qquad \sum_{c=0}^{C-1} \tau_c \cdot s_c \cdot b_r(t) = \omega \tag{3.8}$$

$$\sum_{c=0}^{C-1} \tau_c = \tau$$

$$0 \le \tau_c \le \tau, \qquad \forall c \in \{0, \dots, C-1\}$$

$$(3.9)$$

$$0 \le \tau_c \le \tau, \qquad \forall c \in \{0, \dots, C - 1\} \tag{3.10}$$

Equation 3.7 minimizes the total energy consumption. Equation 3.8 constrains all jobs to complete in the next control period. Equation 3.9 ensures that the time is fully scheduled and Equation 3.10 imposes that a non-negative time is assigned to each configuration. Solving linear optimization problems is, in general, hard, but this particular problem has a structure that makes it practical to solve. Feasible solutions are confined to a polytope in the positive quadrant defined by the two constraints Equations 3.8 and 3.9. Thus, linear programming theory states an optimal solution exists for this problem when all the  $\tau_c$  are equal to zero except for (at most) two configurations [16].

Algorithm 1 takes the set of configurations C, the controller's speedup s(t), and the number of work units  $\omega$  in a control period. It then divides the configurations in two distinct subsets. The first subset contains all configurations with a speedup less than or equal to the target. The second contains the remaining configurations, i.e., those with speedups greater than required. Subsequently, Algorithm 1 loops over all feasible pairs of configurations, with one from each subset, to determine how much time should be spent in each configuration given speedup constraint. If the energy of the pair is lower than any previous energy, the algorithm stores the current best pair, its energy, and its schedule. When the algorithm terminates, its output is the pair of chosen configurations and their assigned times. The algorithm tests all possible pairs from the two subsets, each of which contains at most C

#### **Algorithm 1** Finding a Minimal-Energy Schedule.

```

Require: C

> system configurations, given by user

Require: \omega

by discrete work units, given by application

Require: s(t)

⊳ speedup, given by Equation 3.4

U = \{c \mid s_c \le s(t)\}

O = \{c \mid s_c > s(t)\}

candidates = U \times O = \{ \langle u, o \rangle \mid u \in U, o \in O \}

energy = \infty

optimal = \langle -1, -1 \rangle

schedule = \langle -1, -1 \rangle

for \langle u, o \rangle \in candidates do

▷ loop over all pairs

\omega_u = \omega \cdot \frac{s_u \cdot (s_o - s(t))}{s(t) \cdot (s_o - s_u)}

▷ compute the work units to spend in each configuration in pair

\omega_o = \omega - \omega_u

\begin{array}{l} newEnergy = \frac{\omega_u}{s_u} \cdot p_u + \frac{\omega_o}{s_o} \cdot p_o \\ \textbf{if } newEnergy < energy \textbf{ then} \end{array}

▷ compare energy to best found so far

energy = newEnergy

optimal = \langle u, o \rangle

schedule = \langle \omega_u, \omega_o \rangle

end if

end for

return optimal

▷ pair of configurations with minimal energy

return schedule

▶ work units to spend in each configuration

```

elements, so an upper bound to the algorithm complexity is  $O(C^2)$ . We know that there is an optimal solution to the linear program with at most two non-zero  $\tau_c$  (as the dual problem has two dimensions [16]). Therefore, Algorithm 1 will find a minimal-energy schedule.

#### 3.2.3 Generality and Robustness

The controller and the optimizer both reason about speedup instead of absolute performance or latency. The absolute performance of the application, measured by the average latency of its jobs, will vary as a function of the application itself and the platform it executes on. However, speedup is a general concept and can be applied to any application and system, providing a more general metric for control. Moreover, the controller customizes the behavior of a specific application using the estimate of its base speed produced by the Kalman filter The optimizer operates in a platform-independent manner, using the available configurations provided as input to find the optimal solution, without relying on a particular

heuristic that may be system-specific or application-dependent. Finally, the customizable pole  $\alpha$  in Equation 3.4 allows for flexibility and robustness to inaccuracies and noise.

The ability to control robustness to inaccuracies and model errors is a major advantage of feedback control systems [40]. In particular, POET is stable and converges to the desired latency without oscillations provided that  $0 \le \alpha < 1$ . Formal analysis of this behavior can be obtained by applying standard control techniques—see the original POET publication for further details [63].

In addition to provable convergence, the control formulation allows us to analyze POET's robustness to user error. In particular, suppose  $\Delta$  is a multiplicative error term, indicating the largest error in the speedup values provided in the system configurations. That is, if the provided speedup is  $s_p$ , the real value is  $s_p \cdot \Delta$ . POET cancels the error despite inaccurate information if and only if  $0 < \Delta < \frac{2}{1-\alpha}$ . The value of  $\alpha$  therefore determines how robust POET is to errors in speedup specifications. For example, when  $\alpha = 0.1$ ,  $s_p$  can be off by a factor of 2 and the system is still guaranteed to converge. Users who can provide good system models will therefore use a small  $\alpha$ , while less confident users can select a larger  $\alpha$ . All the experiments in our evaluation use  $\alpha = 0$  to test our implementation in the least forgiving setting. A detailed analysis of POET's robustness is presented in the original POET publication [63].

# 3.3 Implementation

We now describe how the POET framework is implemented as a C library. We specify the information that must be provided by POET's users, describe the library interface, and then discuss the implementation of the runtime engine.

| #id | speedup | powerup | #id | frequency | cores |

|-----|---------|---------|-----|-----------|-------|

| 0   | 1       | 1       | 0   | 250000    | 0     |

| 1   | 1.20    | 1.09    | 1   | 300000    | 0     |

| 2   | 1.40    | 1.16    | 2   | 350000    | 0     |

| 3   | 1.60    | 1.30    | 3   | 400000    | 0     |

| 4   | 2.12    | 1.35    | 4   | 250000    | 1     |

| 5   | 2.53    | 1.50    | 5   | 300000    | 1     |

| 6   | 2.88    | 1.64    | 6   | 350000    | 1     |

| 7   | 3.18    | 1.69    | 7   | 250000    | 2     |

Listing 3.1: System-agnostic.

Listing 3.2: System-specific.

Figure 3.3: Snippets of POET configuration files.

### 3.3.1 External Inputs

POET requires three pieces of information from users. First, it needs the **resource specification**—system configurations and their associated speedup and powerup (timing and power) characteristics. Second, it needs *performance feedback*—timing and power measurements during runtime. Third, it requires the application to specify its *performance goal*.

The first input is the specification of available system configurations. POET separates the system configurations into two data structures. The first is system-agnostic and contains a configuration identifier along with **speedup** and **powerup** values. The second is system-specific and can take any form a developer considers appropriate to define a system configuration. POET includes a default format for this second structure which contains a configuration identifier, the DVFS frequency to apply, and the number of cores to use. Figure 3.3 presents snippets of actual configuration files representing both data structures. Speedup and powerup values are derived from an application characterization, *i.e.*, running a representative application in all configurations and measuring the behavior.

To measure both performance and power, we modify the Heartbeats API [58] to record power data along with timing statistics (see also Appendices A.1 and A.2). We then modify applications to issue heartbeats at appropriate points during processing, typically after the completion of every job. POET can then use this captured timing and power data at runtime.

The third necessary input is a performance target. Performance goals can change during runtime, and POET automatically adapts.

### 3.3.2 Software Interface

Note that this interface described here has changed slightly from the original POET publication, primarily to decouple POET and the Heartbeats API [63]. Users typically interact with only three POET functions. poet\_init initializes POET and returns a poet\_state data structure reference, which stores the control state required to implement the framework described in Chapter 3.2. poet\_apply\_control executes the controller, runs Algorithm 1, and configures the platform. poet\_destroy cleans up the poet\_state data structure.

The poet\_init function takes as parameters: the performance goal, the window period over which the controller operates, the system's configurations, and a reference to the function that applies the given system configurations. It also receives an optional reference to the function that determines the system's current state and a log file name. The first system configuration data structure (system-agnostic) is of type poet\_control\_state\_t, and the second (system-specific) has type void. The two functions passed by reference are the only ones that need to know the format of the second data structure and are therefore passed the void type reference given to poet\_init as parameters. The first of these two functions must have a signature that matches the poet\_apply\_func definition and the second must match the poet\_curr\_state\_func definition.

The poet\_apply\_control function takes as parameters: the poet\_state reference, a unique identifier (for logging purposes), and the measured performance and power values (e.g., as recorded by the Heartbeats API). The poet\_destroy function just takes the poet\_state reference as a parameter. An additional function, poet\_set\_performance\_goal, allows changing the performance goal at runtime.

A separate header exposes auxiliary functions to load system configurations from files, discover the initial system configuration, and apply system configurations. These are for the default file formats and system knobs described in the previous section. The latter two of these functions meet the poet\_curr\_state\_func and poet\_apply\_func definitions, respec-

tively, and can be passed to poet\_init. These auxiliary functions are platform-dependent and thus kept separate to maintain portability, allowing users to easily substitute their own versions. They are, however, generic enough that most Linux users do not need to write their own unless they want to tune different knobs.

#### 3.3.3 Runtime

After an application measures its performance and power, e.g., with a heartbeat, it makes a call to poet\_apply\_control, which contains POET's core logic. When a window period completes, the POET runtime calculates the estimated base speed with Equation 3.6, then computes the performance error with Equation 3.3. It subsequently computes the control signal from Equation 3.4 to determine the speedup necessary to eliminate the error. Finally it determines the energy-minimal resource schedule that achieves the necessary speedup using Algorithm 1 and applies the first configuration in the schedule by executing the provided poet\_apply\_func function.