## THE UNIVERSITY OF CHICAGO

# PRACTICAL VARIATION-AWARE DESIGNS IN QUANTUM COMPUTING

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF COMPUTER SCIENCE

BY

SOPHIA LIN

CHICAGO, ILLINOIS AUGUST 2024

Copyright © 2024 by Sophia Lin All Rights Reserved

# TABLE OF CONTENTS

| LI | ST O         | F FIGURES                                                                   | v               |

|----|--------------|-----------------------------------------------------------------------------|-----------------|

| LI | ST O         | F TABLES                                                                    | ix              |

| A  | CKNC         | OWLEDGMENTS                                                                 | х               |

| Al | BSTR         | ACT                                                                         | xi              |

| 1  | INT          | RODUCTION                                                                   | 1               |

| 2  | NON          | NSTANDARD TWO-QUBIT BASIS GATES FOR QUBIT VARIATIONS $$ .                   | 4               |

|    | 2.1          | Introduction                                                                | 4               |

|    | 2.2          | Background                                                                  | 9               |

|    |              | 2.2.1 Qubits and gates                                                      | 9               |

|    |              | 2.2.2 Geometric characterization of 2Q gates                                | 9               |

|    |              |                                                                             | 10              |

|    | 2.3          | · · · · · ·                                                                 | 11              |

|    | 2.4          |                                                                             | 12              |

|    | 2.5          |                                                                             | 15              |

|    | 2.0          |                                                                             | 15              |

|    |              |                                                                             | 16              |

|    |              |                                                                             | 18              |

|    |              | * 8                                                                         | $\frac{10}{20}$ |

|    |              | <i>y</i> 0                                                                  |                 |

|    | 0 C          |                                                                             | 20              |

|    | 2.6          | • 0                                                                         | 21              |

|    | 2.7          | 1 0 <b>v</b> 0                                                              | 24              |

|    | 2.8          | Case study: entangling fixed frequency far-detuned transmons with a tunable |                 |

|    |              | 1                                                                           | 26              |

|    |              | 2 0 0 0                                                                     | 26              |

|    |              |                                                                             | 28              |

|    |              | 07                                                                          | 30              |

|    |              |                                                                             | 32              |

|    | 2.9          | Conclusion                                                                  | 34              |

|    | 2.10         | Appendices                                                                  | 34              |

|    |              | 2.10.1 Hamiltonian of 2 qubits coupled with a tunable coupler               | 34              |

|    |              | 2.10.2 SWAP synthesis in 2 layers                                           | 35              |

| 3  | COL          | DESIGN OF QUANTUM ERROR-CORRECTING CODES AND MODULAR                        |                 |

|    |              |                                                                             | 37              |

|    | 3.1          |                                                                             | 37              |

|    | $3.1 \\ 3.2$ |                                                                             | 41              |

|    | 0.4          | ÷                                                                           | 41              |

|    |              | 5.2.1 Fabrication errors and variations on transmon-based quantum devices   | 41              |

| 3.2.2 Surface code                                                                       |                                                                               |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 3.3 Deforming boundary and forming super-stability                                       | ilizers $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 44$          |

| 3.4 Building a device with defective qubits                                              |                                                                               |

| 3.4.1 A modular architecture for rotated su                                              | $ rface code \dots 47 $ |

| 3.4.2 Post-selection criterion: assessing the                                            | quality of defective chiplets 48                                              |

| 3.5 Impact on resource overhead                                                          |                                                                               |

| 3.5.1 Resource overhead and sensitivity and                                              | alysis                                                                        |

| 3.5.2 Limit of the monolithic architecture .                                             |                                                                               |

| 3.5.3 Resource overhead and fidelity estima                                              | tion for an example application 60                                            |

| 3.6 What counts as a fabrication error                                                   |                                                                               |

| 3.7 Related work                                                                         |                                                                               |

| 3.8 Conclusion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   |                                                                               |

|                                                                                          |                                                                               |

| 4 SPATIALLY PARALLEL DECODING FOR FAUL                                                   | •                                                                             |

| ICAL OPERATIONS                                                                          |                                                                               |

| 4.1 Introduction $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ |                                                                               |

| 4.2 Background                                                                           |                                                                               |

| 4.2.1 Surface code, lattice surgery, and deco                                            | 8                                                                             |

| 4.2.2 Real time decoding with FPGA<br>4.3 Related work                                   |                                                                               |

|                                                                                          |                                                                               |

| 4.4 Framework of the decoding scheme                                                     |                                                                               |

| 4.4.1 Connecting decoder modules 4.4.2 Metrics                                           |                                                                               |

|                                                                                          |                                                                               |

| 4.4.3 Window configuration for hardware de                                               | 0                                                                             |

| 4.5 Logical error rates                                                                  |                                                                               |

| 4.5.1 Methodology for simulations                                                        |                                                                               |

| 4.5.2 Logical errors along the short edge .                                              |                                                                               |

| 4.5.3 Logical errors along the long edge                                                 |                                                                               |

| 4.5.4 Generalizing to 2D configurations                                                  |                                                                               |

| 4.5.5 Implications                                                                       |                                                                               |

| 4.6 Throughput $\dots$ $\dots$ $\dots$ $\dots$ $\dots$                                   |                                                                               |

| 4.6.1 Inter-window communication                                                         |                                                                               |

| 4.6.2 Inner decoders                                                                     |                                                                               |

| 4.7 Conclusion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                     |                                                                               |

| 5 CONCLUSION AND OUTLOOK                                                                 |                                                                               |

| REFERENCES                                                                               |                                                                               |

# LIST OF FIGURES

| 2.1 | The Weyl chamber of 2Q quantum gates, explained in Sec 2.2.2. The non-local part of a 2Q gate is fully described by its position in the Weyl chamber. As the                       |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | duration of an entangling gate pulse increases, the 2Q gate evolves, traversing a                                                                                                  |    |

|     | Cartan trajectory in the Weyl chamber. CNOT and CZ are both represented by                                                                                                         |    |

|     | $(\frac{1}{2}, 0, 0)$ . The SWAP gate is at the top vertex $(\frac{1}{2}, \frac{1}{2}, \frac{1}{2})$ . On the bottom surface,                                                      |    |

|     | $(t_x, t_y, 0)$ and $(1 - t_x, t_y, 0)$ represent the same equivalent class of gates. For                                                                                          |    |

|     | example, the two points $I_0 = (0,0,0)$ and $I_1 = (1,0,0)$ both represent the 2Q                                                                                                  |    |

|     | identity gate $I$                                                                                                                                                                  | 5  |

| 2.2 | Experimental data showing a nonstandard Cartan coordinate trajectory. An ex-                                                                                                       | 0  |

| 2.2 | perimental implementation [52] of the iSWAP gate with the entangler architecture                                                                                                   |    |

|     | proposed in [96] yielded a nonstandard Cartan coordinate trajectory close to the                                                                                                   |    |

|     |                                                                                                                                                                                    |    |

|     | plane of $I_0$ , SWAP, and iSWAP. The first instance of a perfect entangler was at<br>an entangler duration of 12 ng. In this penetendend trajectory, the 12 ng entangler          |    |

|     | an entangler duration of 13 ns. In this nonstandard trajectory, the 13 ns entan-                                                                                                   |    |

|     | gler is offset from the Cartan coordinate for the square root of iSWAP and the                                                                                                     |    |

|     | 26 ns entangler is likewise offset from the Cartan coordinate for iSWAP. Note                                                                                                      |    |

|     | that due to an experimental hardware constraint the shortest possible entangling                                                                                                   | 14 |

| 0.9 | pulse duration was 4 ns, so the measured Cartan trajectory begins there                                                                                                            | 14 |

| 2.3 | Gate decompositions                                                                                                                                                                | 15 |

| 2.4 | Weyl chamber illustrations of gates                                                                                                                                                | 17 |

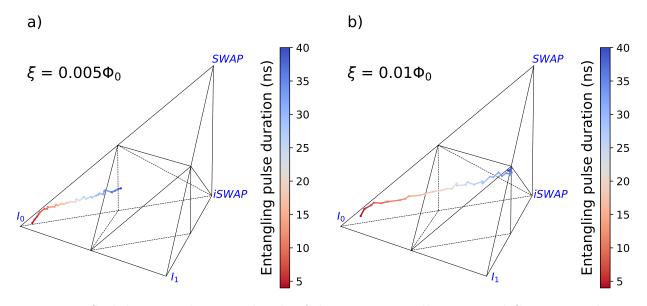

| 2.5 | Stability over drive amplitude of the experimentally measured Cartan coordinate                                                                                                    |    |

|     | trajectories. In the same experimental implementation from Figure 2.2, as the entangling pulse drive emplitude (increased from $0.005\Phi$ , to $0.01\Phi$ , the Center            |    |

|     | entangling pulse drive amplitude $\xi$ increased from $0.005\Phi_0$ to $0.01\Phi_0$ , the Cartan accordinate trajectories were found to double in gread but still be qualitatively |    |

|     | coordinate trajectories were found to double in speed but still be qualitatively                                                                                                   |    |

|     | similar. The data was collected over a two day period. As in Figure 2.2, due to an                                                                                                 |    |

|     | experimental hardware constraint the shortest possible entangling pulse duration                                                                                                   | าว |

| ົງເ | was 4 ns, so the measured Cartan trajectories begin there                                                                                                                          | 23 |

| 2.6 | (a) Optical image of the device presented in [52] shows two fixed frequency trans-                                                                                                 |    |

|     | mons coupled via a tunable coupler. (b) Schematic for modelling the device                                                                                                         | 97 |

| 07  | adapted from [96].                                                                                                                                                                 | 27 |

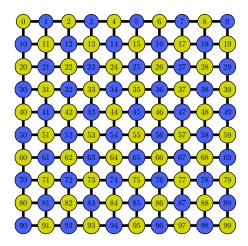

| 2.7 | Device simulation. The high and low frequency qubits are shown in different                                                                                                        | 20 |

|     | colors. Each edge connects two qubits with different colors                                                                                                                        | 30 |

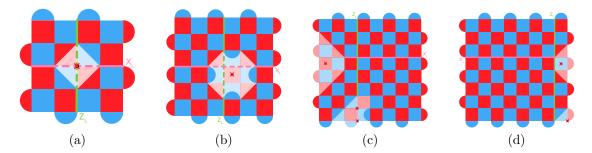

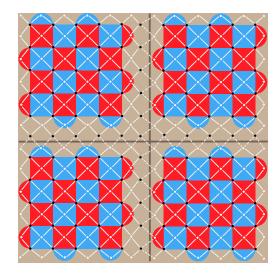

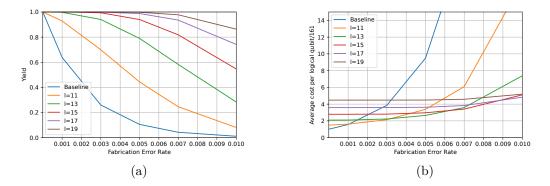

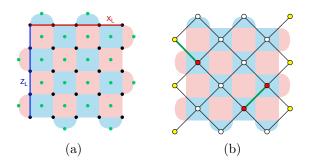

| 3.1 | Examples of super-stabilizers and boundary deformations. The faulty qubits are                                                                                                     |    |

|     | marked with a red 'x', and the excluded part in a patch is represented by lighter                                                                                                  |    |

|     | color. (a) One broken data qubit in the interior, handled by a super-stabilizer. (b)                                                                                               |    |

|     | One broken syndrome qubit in the interior, handled by larger super-stabilizers.                                                                                                    |    |

|     | (c)(d) Broken qubits near the boundary require boundary deformations                                                                                                               | 39 |

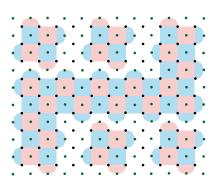

| 3.2 | Rotated surface code with $d=3$ . The black dots represent the data qubits, and                                                                                                    |    |

|     | each red (blue) face represents an X (Z) stabilizer. Each stabilizer requires an                                                                                                   |    |

|     | ancilla qubit.                                                                                                                                                                     | 43 |

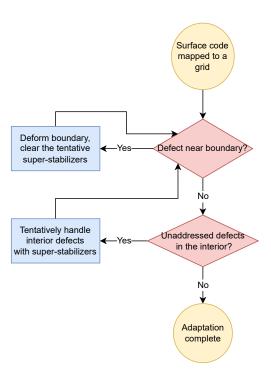

| 3.3 | Algorithm for mapping rotated surface code to a defective grid by deforming                                                                                                        |    |

|     | boundaries and forming super-stabilizers                                                                                                                                           | 44 |

|     | ~ <b>.</b>                                                                                                                                                                         |    |

| 3.4  | Schematic of a chiplet architecture                                                                                                                                     | 48 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

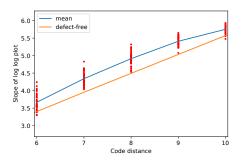

| 3.5  | Slopes of the log-log LER v.s. $p$ plots, from randomly sampled defective rotated surface code patches with $l = 11$ . For each value of $d$ , 50 defective patches are |    |

|      | sampled, with the same probability for link failure and qubit failure. $\ldots$                                                                                         | 50 |

| າເ   |                                                                                                                                                                         | 50 |

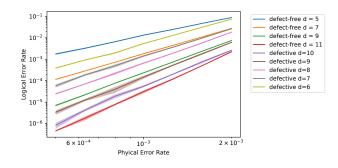

| 3.6  | Logical error rate v.s. physical error rate at low physical error rates $(5 \times 10^{-4})$                                                                            |    |

|      | to $2 \times 10^{-3}$ ), for defect-free patches of rotated surface code, and examples of                                                                               |    |

|      | defective patches with $l = 11$ . The shaded regions represent the 95% confidence                                                                                       | -  |

| ~ -  | intervals for each value.                                                                                                                                               | 50 |

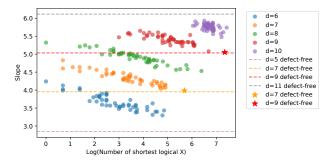

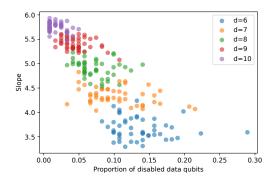

| 3.7  | Slopes of LER v.s. $p$ , from the same defective patches used in Fig. 3.5, grouped                                                                                      |    |

|      | by $d$ and plotted against the log of the number of shortest logical X                                                                                                  | 51 |

| 3.8  | Slopes of LER v.s. $p$ , from the same defective patches used in Fig. 3.5, grouped                                                                                      |    |

|      | by $d$ and plotted against the proportion of disabled physical qubits on a patch                                                                                        | 51 |

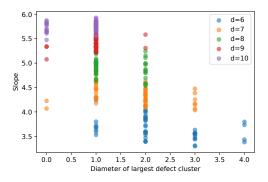

| 3.9  | Slopes of LER v.s. $p$ , from the same defective patches used in Fig. 3.5, grouped                                                                                      |    |

|      | by $d$ and plotted against the diameter of largest cluster of disabled qubits                                                                                           | 52 |

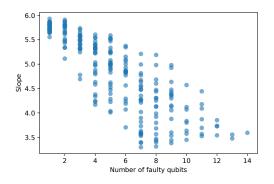

| 3.10 | Slopes of LER v.s. $p$ , from the same defective patches used in Fig. 3.5, plotted                                                                                      |    |

|      | against the number of faulty qubits on a patch.                                                                                                                         | 52 |

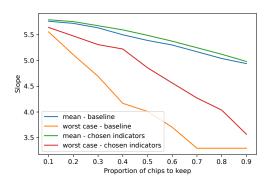

| 3.11 | Mean and worst slopes of selected patches, when the proportion selected is varied.                                                                                      |    |

|      | The baseline only uses the number of faulty qubits (Fig. 3.10); the "chosen                                                                                             |    |

|      | indicators" use $d$ as primary indicator and the number of shortest logical operators                                                                                   |    |

|      | to break ties.                                                                                                                                                          | 52 |

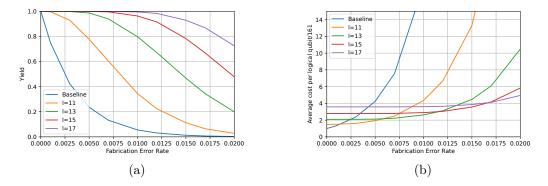

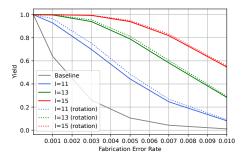

| 3.12 | Defective links only. (a) Proportion of chiplets that support a rotated surface                                                                                         |    |

|      | code patch that performs as well as a defect-free patch of distance 9, evaluated                                                                                        |    |

|      | with the two metrics in 3.7. (b) As for (a) but showing the average number of                                                                                           |    |

|      | fabricated physical qubits per logical qubit scaled by the number in the no-defect                                                                                      |    |

|      | case                                                                                                                                                                    | 54 |

| 3.13 | Links and qubits are assigned faulty at the same rate. (a) Proportion of chiplets                                                                                       |    |

|      | that support a rotated surface code patch that performs as well as a defect-free                                                                                        |    |

|      | patch of distance 9, evaluated with the two metrics in 3.7. (b) The same as for (a)                                                                                     |    |

|      | but showing the average number of fabricated physical qubits per logical qubit                                                                                          |    |

|      | scaled by the number in the no-defect case                                                                                                                              | 55 |

| 3.14 | An example where the code distance drops after a merge                                                                                                                  | 55 |

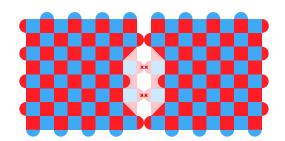

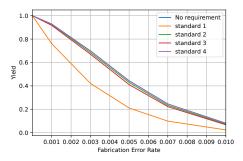

|      | The change in yield after imposing different standards on boundaries of patches.                                                                                        | 00 |

| 0.10 | Standard 1: No deformation on any boundary; standard 2: at least 2 boundaries                                                                                           |    |

|      | of different types have no deformation; standard 3: all 4 boundaries support                                                                                            |    |

|      | lattice surgery without decreasing distance; standard 4: at least 2 boundaries of                                                                                       |    |

|      | different types support lattice surgery without decreasing distance                                                                                                     | 56 |

| 3 16 | Improvement in yield when there is freedom to rotate the chiplets. Links and                                                                                            | 50 |

| 0.10 | qubits are assigned faulty at the same rate                                                                                                                             | 57 |

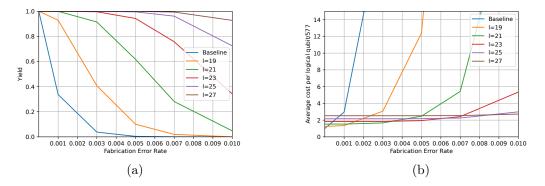

| 3 17 | Yields for larger chiplets. Defective links only. (a) Proportion of chiplets that                                                                                       | 51 |

| J.17 | support a rotated surface code patch that performs as well as a defect-free patch                                                                                       |    |

|      |                                                                                                                                                                         |    |

|      | of distance 17, evaluated with the two metrics in 3.7. (b) The same as for (a) but<br>showing the average number of fabricated physical cubits per logical cubit scaled |    |

|      | showing the average number of fabricated physical qubits per logical qubit scaled                                                                                       | ۳o |

|      | by the number in the no-defect case                                                                                                                                     | 58 |

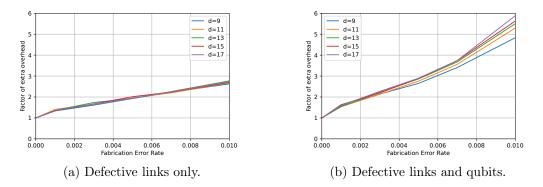

| 3.18       | The extra resource overhead due to defects, for different target logical error rates.<br>The y-axis is the average number of fabricated qubits for a logical qubit, scaled<br>by the number in the ideal no-defect case. The target logical error rate is the                                                                                                                                                                          | - 0      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

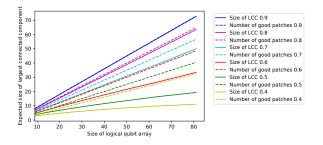

| 3.19       | fidelity of the defect-free rotated surface code of code distance $d. \ldots \ldots$ .<br>Limit of a monolithic architecture. The figure shows the expected size of largest<br>connected component of the good patches on a square array of surface code<br>patches allocated on a monolithic device, where each patch is randomly assigned                                                                                            | 59       |

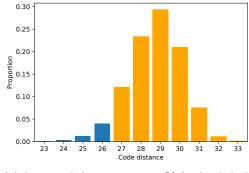

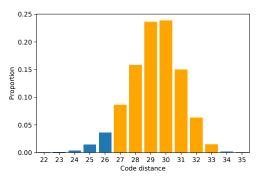

| 3.20       | to be good/bad. The label of each line is the proportion of the good patches Distribution of code distance. In orange: proportions of patches with $d \ge 27$ ; in                                                                                                                                                                                                                                                                     | 60       |

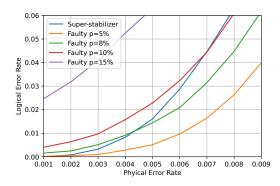

| 3.21       | blue: proportions of patches with $d < 27$ Stability experiment results from keeping/disabling a bad data qubit on a $d = 5$ surface code. The x-axis is the physical error rate of the good qubits                                                                                                                                                                                                                                    | 62<br>65 |

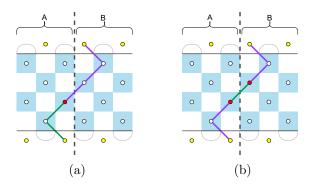

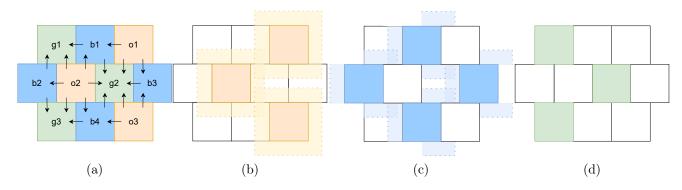

| 4.1<br>4.2 | A merge operation in lattice surgery, specifically, a logical $Z \otimes Z$ measurement.<br>(a) A square patch of surface code. The red and blue faces are the X and Z stabilizers, respectively. The blue and red lines mark $\hat{Z}_L$ and $\hat{X}_L$ , the Z and X logical operators. (b) An example decoding graph for the X errors. The vertices are the Z stabilizers, augmented by the virtual boundary node (in yellow). The | 69       |

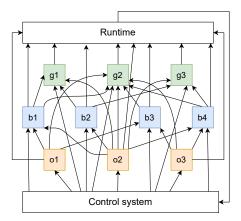

| 4.3        | stabilizers that are flipped are marked in red, and a minimum weight matching<br>is denoted by the green edges                                                                                                                                                                                                                                                                                                                         | 73       |

| 4.4        | disallowed                                                                                                                                                                                                                                                                                                                                                                                                                             | 78<br>79 |

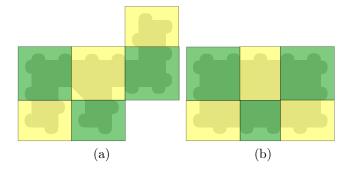

| 4.5        | (a) A patch with a tree structure is 2-colorable. (b) A patch that arises during a                                                                                                                                                                                                                                                                                                                                                     | 82       |

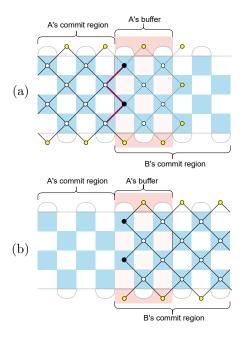

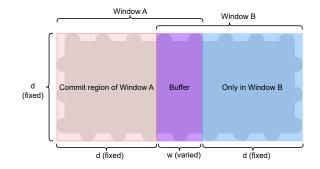

| 4.6        | $Y \otimes Y$ logical measurement. Not 2-colorable                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 4.7        | this figure is chosen to improve readability                                                                                                                                                                                                                                                                                                                                                                                           | 83<br>85 |

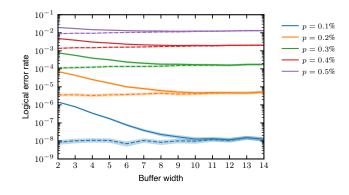

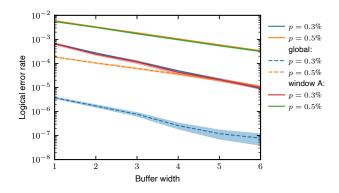

| 4.8  | Logical error rate v.s. buffer width, using the setup in Figure 4.7 with $d = 15$ ,            |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | counting the logical errors along the short edge (that connect the top and bottom              |    |

|      | boundaries). The dashed lines are the baseline results from using a <i>global</i> decoder      |    |

|      | on the same underlying patch. The shaded regions indicate the 95% confidence                   |    |

|      | intervals. Each data point at $p = 0.1\%$ is obtained with 8B shots                            | 86 |

| 4.9  | The data in Figure 4.8 represented differently. (a) Logical error rate v.s. physical           |    |

|      | error rate, for parallel decoding with different buffer width $w$ . (b) The slopes of          |    |

|      | the lines in (a) and (b), plotted against $w$                                                  | 87 |

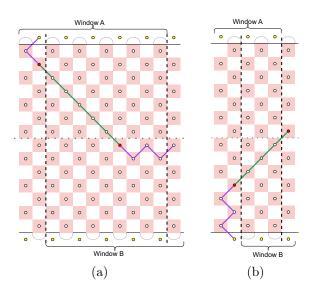

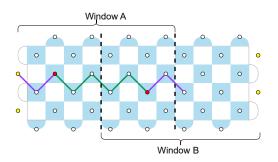

| 4.10 |                                                                                                |    |

| -    | global decoder. Left: $w = 9$ . Right: $w = 3$ . In each example, the region between           |    |

|      | the two dashed vertical lines is the overlap of windows A and B. Window A is                   |    |

|      | decoded first. The flipped stabilizers are in red. The error strings are in green.             |    |

|      | The purple edges are wrong decoder outputs by A. The dotted horizontal line                    |    |

|      | marks the middle of the patch.                                                                 | 87 |

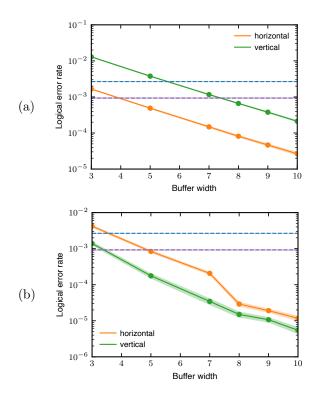

| 4.11 | Logical error rate v.s. buffer width, using the setup in Figure 4.7 with $d = 7$ ,             |    |

|      | counting the logical errors along the long edge. The dashed lines are the baseline             |    |

|      | results from using a <i>global</i> decoder on the same patch. The results from applying        |    |

|      | the global decoder on a patch that is the size of window A are also shown                      | 91 |

| 4.12 | An example error string that causes a logical error along the long edge, when                  | -  |

|      | the parallel decoder is used. As in Figure 4.10, window A is applied before B,                 |    |

|      | the buffer is between the vertical dashed lines, the error string is in green, and a           |    |

|      | wrong decoder output by A is in purple.                                                        | 91 |

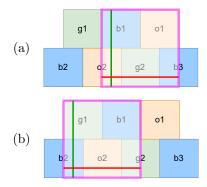

| 4.13 | Setups for simulations with 5 windows stacked in 2 rows. The area of the under-                |    |

|      | lying patch is enclosed by the pink square. The vertical and horizontal logical                |    |

|      | operators are in green and red. In (a) the two original patches that are merged                |    |

|      | are labelled b1 and o1, while in (b) they are labelled g1 and b1                               | 92 |

| 4.14 | LER v.s. buffer width at $p = 0.4\%$ over 15 rounds, using the setups in Fig. 13a              |    |

|      | and 13b respectively, with horizontal and vertical logical operators. The size of              |    |

|      | each smaller square (e.g. the commit region of b1) is chosen to be $15 \times 15$ . The        |    |

|      | blue (purple) baseline is the LER of two isolated patches, each with size $15 \times 29$       |    |

|      | $(15 \times 15)$ , taken over 15 rounds and with logical errors along the edge with $d = 15$ . | 93 |

| 4.15 | A flowchart of the parallel decoding scheme, the colored squares correspond to                 |    |

|      | the windows in Figure 4.6.                                                                     | 95 |

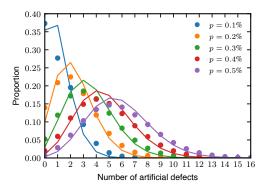

| 4.16 | The number of artificial defects, from the same simulations as Figure 4.8. The                 |    |

|      | curves are fit to the Poisson distribution                                                     | 97 |

# LIST OF TABLES

| 2.1 | Average duration (top) and coherence-limited gate fidelity (bottom) of the 2Q                                                                              |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | basis gates and the synthesized SWAP and CNOT gates, from baseline, Criterion                                                                              |    |

|     | 1, and Criterion 2. $\ldots$                                              | 32 |

| 2.2 | The decoherence-limited fidelities of benchmark circuits, transpiled using the standard 2Q basis gates from baseline, and the nonstandard ones selected by |    |

|     | Criterion 1 and 2. The QAOA benchmarks all have $p = 1$ where p is the number                                                                              |    |

|     | of times the protocol is repeated. The fractions 0.1 and 0.33 are the probabilities                                                                        |    |

|     | that an edge is created between a pair of nodes                                                                                                            | 33 |

| 3.1 | Resource estimation for building a device that supports a $226.63$ grid of distance-                                                                       |    |

|     | 27 surface code patches, for a defect rate of 0.001 on both qubits and links. No-                                                                          |    |

|     | <i>defect</i> is the ideal setting without fabrication defects, not an approach to handle                                                                  |    |

|     | defects. Both the <i>defect-intolerant</i> and the <i>super-stabilizer</i> approaches here post-                                                           |    |

|     | select chiplets to make a modular device. Overhead is the factor of resource                                                                               |    |

|     | overhead, determined by the yield and the size of each chiplet; <i>Qubits</i> is the total                                                                 |    |

|     | number of physical qubits fabricated for the application.                                                                                                  | 61 |

| 3.2 | Same as Table 3.1 but for a defect rate of 0.003.                                                                                                          | 61 |

| 3.3 | Application fidelity estimated with the topological error. Baseline1: modular,                                                                             | 01 |

| 0.0 | defect-intolerant. Baseline2: monolithic, uses super-stabilizers to handle defects.                                                                        | 63 |

| 3.4 | Same as Table 3.3 but for a defect rate of 0.003                                                                                                           | 63 |

| 0.4 |                                                                                                                                                            | 05 |

# ACKNOWLEDGMENTS

Throughout my PhD journey I have been fortunate to meet many people who have offered encouragement, valuable advice, and inspiration. First I would like to thank my advisor Fred Chong for his guidance and support throughout my PhD. I would also like to thank my committee members Ben Brown and Bill Fefferman for their time. My three summer internships were enriching experiences, thanks to the mentorship of Dan, Andrew, Drew, Eric, Prashant, and Krishanu. I am grateful to my labmates and other collaborators, including Andy, Casey, Charles, Charlie, Chris, Gokul, Jason, Jonathan, Josh, Kate, Max, Michael, Natalia, Pranav, Ryan, Sam, Sara, Siddarth, Teague, Wei, Yongshan, and Yunong. Lastly, I am grateful for the support of my family and friends.

## ABSTRACT

Variations are prevalent in all aspects of quantum computing. On solid state quantum devices, fabrication errors lead to variations in device connectivity. Among the qubits that are available for use, there are still variations in multiple properties. Other than hardware variations, different algorithms and operations impose different requirements on the devices and systems. In order to bridge the gap between the theory and implementation of quantum computing, we need practical designs that are aware of variations and system-level tradeoffs. This thesis includes three examples of adapting to variations: choosing two-qubit basis gates based on individual qubits' properties, adapting error correction codes and using modular architecture to support fault-tolerant computation in the presence of fabrication defects, and adapting real time decoding protocols to support large patches of topological codes that arise during lattice surgery operations.

# CHAPTER 1 INTRODUCTION

Quantum computing is an interdisciplinary field that encompasses diverse research areas. Its advancement requires both highly abstract theory research, like the high-level design of quantum algorithms and error correction codes, and experimental efforts that focus on the development and implementation of quantum hardware. Theory works make simplifying assumptions about the underlying hardware, which allow them to focus on the core concepts. For example, it is common for a paper that proposes a novel quantum algorithm to assume that it runs on an ideal noiseless quantum device, and for a paper on quantum error correction to use a simplified phenomenological noise model. In addition to ignoring noises, another common assumption is uniformity, including but not limited to uniformity across physical qubits on a device.

While simplification is necessary for research, various complications arise when it comes to practically implementing quantum applications on hardware. Qubits are not only susceptible to a variety of noises that require mitigation, but some of them, including the superconducting qubits that are the currently leading candidates, also exhibit inhomogeneity. This leads to variability in performance and characteristics, even among qubits on the same device. In the worst case, a qubit or link between qubits could have severely limited functionality, reducing the connectivity of the device. The design of quantum computing architectures must be flexible enough to accommodate these variations in qubit behavior and performance.

Research in software and computer architecture should also meet the various demands imposed by quantum algorithms. For example, fault-tolerant quantum algorithms require real time decoding of syndromes. For superconducting devices with fast syndrome measurement cycles, it is hard for a software decoder designed to run on a CPU to meet the requirement for real time decoding. In recent years, there have been real time decoders based on FPGAs, ASICs, or SFQ circuits. Different quantum error correction codes also impose distinct requirements on quantum computers. Topological codes like the surface code and the color code only require nearest-neighbor interactions, but their low encoding rates leads to a high qubit overhead. On the contrary, some qLDPC codes have high encoding rates but require long range connectivity.

This dissertation presents three examples of adapting to variations that are often overlooked. Specifically, Chapter 2 and 3 address different aspects of the variations in qubit characteristics, and Chapter 4 involves a variation in quantum application.

Chapter 2 introduces a framework for selecting different "nonstandard" two-qubit basis gates for each link on a superconducting quantum device. Conventionally, it is assumed that the same two-qubit basis gate (typically an XX- or XY-type gate) is implemented between every pair of neighboring qubits on a quantum device. This assumption is prevalent in quantum compiler research, and the research that studies the expressivity of different twoqubit gates. However, if the same target two-qubit gate is selected as basis gate for the entire device, even a small amount of coherent crosstalk between two qubits will cause a gate to have a deviation from the target. We instead studied how to select the most efficient "nonstandard" two-qubit basis gate, given the systematic deviations in the Cartan trajectory of an interaction.

Chapter 3 considers the problem of implementing quantum error correction codes on defective arrays of qubits. Prior work had proposed techniques that deforms the surface code in the presence of defective qubits and links. We proposed to implement surface codes on modular chiplets, and use the flexibility of a modular design to mitigate the resource overhead caused by fabrication defects. Our work addressed several practical challenges that need to be solved before one can build a large scale fault-tolerant device that implements surface code. We developed an automated protocol for adapting the rotated surface code to a grid with an arbitrary defect distribution. With this tool, we performed numerical simulations to identify the key metrics that characterize the fidelity of a surface code on a defective array of qubits. These metrics serve a dual purpose: firstly, as post-selection criteria for the strategic selection and arrangement of chiplets; secondly, they facilitate the simulations to assess the resource overheads. We also determine cutoff fidelity values that help identify whether a qubit should be disabled or kept as part of the error correction code.

The topic in Chapter 4 is adapting real time decoders to the large patches of codes that arise during lattice surgery. This is accomplished by dividing the device into multiple overlapping windows and assigning a decoder module to each window. We refer to this approach as spatially parallel windows. While previous work has explored similar ideas, none have addressed the unique hardware constraints and system-specific considerations pertinent to the task. We show how to configure spatially parallel windows, so that the scheme (1) is compatible with hardware accelerators, (2) supports general lattice surgery operations, (3) maintains the fidelity of the logical qubits, and (4) meets the throughput requirement for real time decoding. Furthermore, our results reveal the importance of optimally choosing the buffer width to achieve a balance between accuracy and throughput — a decision that should be influenced by the device's physical noise.

These examples demonstrate the need for quantum computer architecture research that bridges theory and hardware, both for physical operations and logical operations. Chapter 5 concludes with a discussion of future work in this direction.

# CHAPTER 2 NONSTANDARD TWO-QUBIT BASIS GATES FOR QUBIT VARIATIONS

## 2.1 Introduction

Quantum computers have the potential to solve problems currently intractable for conventional computers [107], but current computations are limited by errors [99], particularly when interacting two qubits to perform a quantum gate operation. This is not surprising, as qubits are engineered to preserve quantum state and be isolated from the environment, but a quantum operation is a moment in time where external control is applied from the environment to deliberately alter a qubit's state. To accomplish low-error gates, the control mechanisms are carefully designed and the control signals are calibrated for each qubit or pair of qubits.

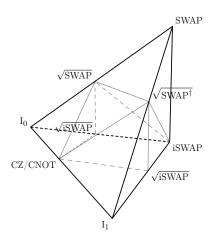

Similar to how classical computers use a small set of classical logic gates (AND, OR, NOT, XOR...) as building blocks for larger circuits, current superconducting quantum devices typically only directly support a universal gate set consisting of a few two-qubit (2Q) gates and a continuous set of single-qubit (1Q) gates. This paper will refer to the set of directly supported quantum gates as *basis gates*. In the space of 2Q gates (see Fig.2.1), any point that does not coincide with SWAP or Identity has nonzero entangling power. Any of these 2Q entangling gates can achieve universal computation when added to a continuous set of 1Q gates [20].

Using the minimal set of gates needed for universal computing is rarely a desirable thing to do. For example, while the NAND is universal in classical computing, building circuits from it alone is less efficient than using a larger set of logic gates. However, the intensive calibrations necessary for high fidelity 2Q gates between qubits in a large quantum computer make it impractical to support a large set of 2Q basis gates. All logical 2Q gates scheduled to

Figure 2.1: The Weyl chamber of 2Q quantum gates, explained in Sec 2.2.2. The non-local part of a 2Q gate is fully described by its position in the Weyl chamber. As the duration of an entangling gate pulse increases, the 2Q gate evolves, traversing a Cartan trajectory in the Weyl chamber. CNOT and CZ are both represented by  $(\frac{1}{2}, 0, 0)$ . The SWAP gate is at the top vertex  $(\frac{1}{2}, \frac{1}{2}, \frac{1}{2})$ . On the bottom surface,  $(t_x, t_y, 0)$  and  $(1 - t_x, t_y, 0)$  represent the same equivalent class of gates. For example, the two points  $I_0 = (0, 0, 0)$  and  $I_1 = (1, 0, 0)$ both represent the 2Q identity gate I.

run on a quantum computer have to be decomposed by its compiler into alternating layers of pre-calibrated 1Q and 2Q basis gates. Thus, the choice of which 2Q gates to directly support is critical to enabling high-performance quantum computing. On the hardware side, the 2Q basis gates must have high-fidelity hardware implementations. On the software side, they must enable the low-depth decomposition of other 2Q gates.

Superconducting qubits support XX- and XY-type 2Q interactions [6, 72]. The strength of each of these interactions depends on the type of coupling, the coupling strength, and the frequency detuning between the qubits [72]. The Weyl chamber space of 2Q gates (Fig. 2.1) is a useful way to visualize these interactions: the coordinates of a gate correspond to its non-local part in Cartan's KAK decomposition (see Section 2.2.2). In the Weyl chamber, gates in the XX family form a straight trajectory from Identity to CNOT/CZ, while gates in the XY family form a trajectory from Identity to iSWAP. Cartan trajectories are generated by increasing the duration of an entangling gate pulse, which evolves the 2Q gate.

Section 2.4 describes the various difficulties associated with reliably performing standard

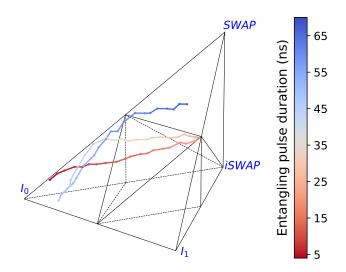

2Q gates like CZ and iSWAP on today's superconducting quantum computers. Whether a deviation from a standard Cartan trajectory is a 2Q error depends on what the target 2Q gate is. If the target 2Q gate has to be a certain standard gate (e.g. iSWAP), even a small amount of coherent crosstalk between the two qubits will cause the gate to have a small CZ component, and so the gate will not be identically iSWAP. However, if that coherent crosstalk is a stable systematic that does not add noise or cause decoherence, the gate could still be an effective, high fidelity entangler that is useful for computing; the target 2Q gate would just have to be a nonstandard unitary rather than the standard iSWAP. In Section 2.4 we also show an example of an experimentally measured Cartan trajectory of 2Q gates on a superconducting qubit device. The measured Cartan trajectory includes very fast nonstandard 2Q gates with high entangling power, but it does not pass through traditional basis gates like iSWAP and CZ. This example motivates us to develop methods that enable the use of nonstandard 2Q gates for quantum computing. If we allow for deviations from standard 2Q gates, we can use high fidelity, non-standard quantum hardware for practical quantum computing.

Using nonstandard 2Q basis gates requires methods for identifying good basis gates on a general 2Q gate trajectory, calibrating a nonstandard gate, and compiling with nonstandard basis gates. The primary focus of our work is to construct and demonstrate a framework for efficiently identifying a "good" set of 2Q basis gates from a nonstandard trajectory. But we also propose solutions for calibration and compilation.

What are our standards for a good set of 2Q basis gates? Following the principle of Amdahl's Law, we pay most attention to the SWAP gate as a target for synthesis because of its importance for communication within programs executing on superconducting devices. To mitigate crosstalk and satisfy other hardware constraints, superconducting devices usually have the sparse connectivity of a grid lattice or a hexagonal lattice. Therefore, the compiler has to schedule a series of SWAP gates before it can interact two qubits that are not adjacent to each other. Although clever mapping from logical to physical qubits can result in a smaller number of inserted SWAP gates, we still observe a high proportion of SWAP gates in postmapping quantum circuits. Besides efficient synthesis of the SWAP gate, our framework also allows one to prioritize other target gates, including but not limited to CNOT, iSWAP, and the B gate. It also enables the simultaneous prioritisation of multiple target gates.

The calibration of a non-standard 2Q basis gate requires identifying a gate duration that gives an ideal basis gate and then accurately characterizing the corresponding gate so that we use the right unitary for compiling. Our proposed calibration protocol address both without causing a long downtime on a quantum device. However, we point out that in order to *precisely* characterize a non-standard gate, one should consider using gate set tomography (GST) as opposed to quantum process tomography (QPT). The data collected from GST experiments may require several hours of classical processing. Before that finishes, one would have to use the calibration results from the previous cycle. The speedup of GST's classical processing, which is an active field of research [4], would help reduce the cost of calibrating non-standard gates. In addition, we observed that the systematic deviations are stable over days (Fig. 2.5). If the change in deviation is negligible, one may not need to apply GST in every calibration cycle.

Compiling with non-standard 2Q basis gates requires a conversion from arbitrary 2Q gates into the basis gates. There isn't a general analytical formula that works for arbitrary target and basis gate, so a numerical search is needed. However, we can analytically obtain information on the minimum circuit depth needed for a perfect synthesis and use it to facilitate the numerical search. Besides, the circuits that synthesise common gates from the basis gates can be pre-computed after each calibration cycle, so that one wouldn't need to re-compute them for every program.

Our contributions are summarized below.

• Our work is the first to consider using 2Q basis gates from general non-standard gate

trajectories that are not parametrized by a simple function.

- We provide a theoretical framework for identifying and visualizing the set of good 2Q basis gates, given a set of target 2Q gates to prioritize. With an emphasis on SWAP, we characterize the sets of gates that enable the synthesis of SWAP in 1, 2, and 3 layers, respectively. As another example, we visualize the gates that are able to both synthesize SWAP in 3 layers and CNOT in 2 layers. After identifying the volume of desirable basis gates in the Weyl chamber, one can select the first intersection of the trajectory with the volume as the 2Q basis gate. (Section 2.5)

- We propose a practical calibration protocol that is agnostic as to whether a 2Q gate is standard or non-standard. (Section 2.6)

- We discuss a practical approach to compiling with non-standard 2Q basis gates. (Section 2.7)

- We apply our methods to a case study entangling gate architecture with far-detuned transmon qubits [96]. First, we use our theoretical framework to select 2Q basis gates from simulated nonstandard Cartan trajectories that are realistic for this case study architecture. By increasing the entangling pulse drive amplitude we get a significant 2Q basis gate speedup but introduce a deviation into the Cartan trajectory. Then we use these 2Q basis gates to run a variety of benchmark circuits including BV[12], QAOA[38], the QFT adder[103], and the Cuccaro Adder[28], and compare to the results from using the √*iSWAP* gate on the standard XY-type trajectory. (Section 2.8)

#### 2.2 Background

## 2.2.1 Qubits and gates

Unlike a classical bit that is either 0 or 1, a quantum bit (qubit) can exist in a linear superposition of  $|0\rangle$  and  $|1\rangle$ ; A general quantum state can be expressed as  $\alpha|0\rangle + \beta|1\rangle$  where  $\alpha, \beta$  are complex amplitudes that satisfy  $|\alpha|^2 + |\beta|^2 = 1$ . Thus, the state of one qubit can be represented by a 2-vector of the amplitudes  $\alpha$  and  $\beta$ . A system of *n* qubits can exist in a superposition of up to  $2^n$  basis states, and its state can be represented by a  $2^n$ -vector of complex amplitudes. A quantum gate that acts on *n* qubits can be represented by a  $2^n \times 2^n$  unitary matrix.

# 2.2.2 Geometric characterization of 2Q gates

Two 2Q quantum gates  $U_1, U_2 \in SU(4)$  are *locally equivalent* if it is possible to obtain one from the other by adding 1Q operations. In other words, 2Q operations  $U_1$  and  $U_2$  are locally equivalent if there exist  $k_1, k_2 \in SU(2) \otimes SU(2)$  such that  $U_1 = k_1 U_2 k_2$ . For example, CNOT and CZ are locally equivalent via Hadamard gates.

Any 2Q quantum gate  $U \in SU(4)$  can be written in the form of

$$U = k_1 \exp(-i\frac{\pi}{2}(t_x X \otimes X + t_y Y \otimes Y + t_z Z \otimes Z))k_2$$

(2.1)

where X, Y, Z are the Pauli gates. This is called the Cartan decomposition.

The space of two-qubit quantum gates can be represented geometrically in a Weyl chamber (Fig. 2.1), where each point stands for a set of gates that are locally equivalent to each other [136]. The Cartan coordinates  $(t_x, t_y, t_z)$  in Eq. (2.1) are the coordinates of U in the Weyl chamber. They fully characterize the *non-local* part of a 2Q gate. On the bottom surface,  $(t_x, t_y, 0)$  and  $(1 - t_x, t_y, 0)$  represent the same equivalent class of gates. The other points in the Weyl chamber each represent a different equivalence class of 2Q gates. We refer the interested readers to [27] for a more thorough introduction to the Weyl chamber. Note that other conventions of the Cartan coordinates are also common. They usually differ from ours by a constant factor of  $\pi$  or  $2\pi$ .

In this paper, when we talk about some gate G in the Weyl chamber, we usually mean the local equivalence class of 2Q gates that includes G.

# 2.2.3 Entangling power of 2Q gates

The entangling power [135] is a widely accepted quantitative measure of the capacity of a 2Q gate to entangle the qubits that it acts on. It is typically a good indicator of the ability of a specific 2Q gate to synthesize arbitrary 2Q gates. For a unitary operator U, the entangling power  $e_p(U) \in [0, \frac{2}{9}]$  is defined as the average linear entropy of the states produced by U acting on the manifold of all separable states [135]. It is solely based on the non-local part of U, which is characterized by the position of U in the Weyl chamber.

A 2Q gate has 0 entangling power if and only if it is locally equivalent to the Identity or the SWAP gate. Conversely, 2Q gate U is called a *perfect entangler* if it can produce a maximally entangled state from an unentangled one[136]. Perfect entanglers (PE) have entangling power no less than  $\frac{1}{6}$ . They constitute a polyhedron in the Weyl chamber that is exactly half of the total volume. The 6 vertices of the PE polyhedron are CZ(CNOT), iSWAP,  $\sqrt{SWAP}$ ,  $\sqrt{SWAP}^{\dagger}$ , and the 2 points that both represent  $\sqrt{iSWAP}$ . The perfect entanglers with maximal entangling power of  $\frac{2}{9}$  are also called *special perfect entanglers*[102]. In the Weyl chamber, they are on the line segment from CNOT to iSWAP. The B gate (Berkeley gate), which is at the midpoint of this line segment, has the property that it can synthesize any arbitrary 2Q gates within 2 layers[137]. However, there has been no proposal to directly implement the B gate in hardware.

#### 2.3 Related work

To the best of our knowledge, no prior work involves using 2Q basis gates from arbitrary nonstandard gate trajectories. In parallel with this work, Lao et al. [73] propose to mitigate coherent parasitic errors in 2Q gates by software and present methods of compilation. Our work is more general then [73], although we share the insight that coherent errors in 2Q gates can be treated as part of the gate for compilation. While our framework works for general irregular trajectories and select basis gates on them using the approach detailed in Section 2.5, they focus on iSWAP-like (XY) gates with an unwanted CPHASE (XX) component (which belongs to the FSim gate set so is not truly non-standard) and always use CPHASE( $\psi$ )iSWAP( $\pi/4$ ) because it has similar expressivity as iSWAP( $\pi/4$ ) for small deviation  $\psi$ . They do not discuss calibration. Their baseline for evaluation is similar to the baseline in our case study, which is to make the trajectory more standard by lengthening the gate duration.

Recent research from both the experimental [42, 86, 132, 57] and theory sides has utilized 2Q (and 3Q) basis gates from a continuous set of standard gates, as opposed to only building and compiling with the best-known gates like CNOT and iSWAP. The works that are most relevant to this project are those that look for a small set of 2Q basis gates (from a continuous standard gate set) that are the most valuable to calibrate. Lao et al. [74] use a numerical approach to test the performance of different gates from the fSim and XY gate sets on a range of application circuits, with the overall circuit success rate as the objective. Peterson el al. [94] from IBM use analytic techniques to find that the gate set { $CX, CX^{1/2}, CX^{1/3}$ } is almost as good as the entire continuous set of XX gates in implementing random 2Q gates. They try to minimize the expected (average) infidelity in implementing random 2Q gates under an experimentally motivated error model. Huang et al. [61] proposes using the  $\sqrt{iSWAP}$  as 2Q basis gate, instead of using iSWAP or CNOT, and implement it using a 2-fluxonium qubit device. Recent proposals for novel nonstandard 2Q gates in the supercon-

ducting qubit literature that are informed by the current experimental challenges in scaling up with standard 2Q gates include [93, 133].

## 2.4 Systematic deviations in 2Q gates

The 2Q gate is a critical building block that must be well-engineered before it is used to construct a quantum computer with many qubits. In practice, engineering 2Q gates in the lab involves iterating prototypes of the devices to minimize any and all systematic errors that result from imperfect device design or control along with nonuniformities in device fabrication.

Even if unwanted crosstalk between the qubits is successfully reduced and the 2Q gate is shown to be an effective entangler with a consistent identity, if the gate's identity is somehow nonstandard, one would normally assume it is not useful. The constraint of requiring 2Q gates to be standard is most burdensome for the superconducting qubit platform, where device Hamiltonians are engineered from scratch and there is no 2Q gate that is truly native to the platform - unlike, for instance, the SWAP gates that are native to atomic qubits [124].

Today's multi-qubit superconducting devices are not able to perform perfectly identical 2Q gates between every pair of qubits because of device-level imperfections, tradeoffs and uncertainties. Experimentalists model the expected rate of information leakage between on-chip elements using microwave circuit design software [3, 2], but it is inevitable that irregularities arise during device fabrication and packaging. The devices are at least partially handmade and every fabrication tool has a finite precision. Also, the various materials that make up the layers of the superconducting device can host physical two-level systems that act as sources of noise and even can coherently interact with qubits [105, 112]; reducing the effect of these two-level systems is an active field of research [125]. Another active field of research is reducing irregularities in the fabrication of Josephson junctions, which are critical on-chip elements [68, 54]. For a given device, it can be difficult for the experimentalist to

determine whether a systematic 2Q gate deviation is caused by an imperfection in the device design or in its control. For example, a common source of systematic 2Q gate deviation is the imperfect mitigation of the static ZZ crosstalk which is a dominant source of 2Q gate error for transmon qubits [88, 71, 117, 91, 64, 138]. Devices can be designed to suppress the static ZZ crosstalk but unless the device is properly fabricated, packaged, biased and controlled there will be nonzero static ZZ crosstalk which will cause the 2Q gate to deviate from the target unitary.

Superconducting devices can also have higher order Hamiltonian terms that result in the experimentally measured Cartan trajectory of 2Q gates deviating from the expected Cartan trajectory. This deviation is particularly significant for fast gates enabled by large coupling or large drive strength [96, 84, 63]. Experimentalists have historically tried to suppress these deviations by reducing the 2Q gate drive strength, which has the negative consequence of slowing the 2Q gate down. It is in general difficult to accurately model the effect of the strong drives that perform fast 2Q gates on the Hamiltonian level, and this is an active field of research [96].

Plotting measured 2Q gates in Cartan coordinates is a valuable tool experimentalists can use to easily visualize and study any deviations their gates may have from the expected Cartan trajectory. For example, Figure 2.2 shows a measured Cartan trajectory that is nonstandard. This experimental data was collected from one of the first iterations of a superconducting device [52] that was designed to implement a recently proposed entangling gate architecture [96]. The data includes a very fast (13 ns) perfect entangler. Since the measured trajectory was systematically offset from the predicted one (XY), the experimentalists investigated potential sources of that systematic offset. Since this source of deviation could be eliminated with better device and control engineering, the experimentalists began to optimize their next device iteration accordingly. But in this work we suggest that there is nothing inherently unusable about measured Cartan trajectories that are nonstandard due

Figure 2.2: Experimental data showing a nonstandard Cartan coordinate trajectory. An experimental implementation [52] of the iSWAP gate with the entangler architecture proposed in [96] yielded a nonstandard Cartan coordinate trajectory close to the plane of  $I_0$ , SWAP, and iSWAP. The first instance of a perfect entangler was at an entangler duration of 13 ns. In this nonstandard trajectory, the 13 ns entangler is offset from the Cartan coordinate for the square root of iSWAP and the 26 ns entangler is likewise offset from the Cartan coordinate for iSWAP. Note that due to an experimental hardware constraint the shortest possible entangling pulse duration was 4 ns, so the measured Cartan trajectory begins there.

to this kind of coherent systematic offset, and that the 13 ns nonstandard perfect entangler identified in Figure 2.2 could be treated as a native 2Q basis gate by the compiler.

Our work seeks to enable the use of the nonstandard 2Q gates that can be native to superconducting devices. If 2Q gate calibration and compiling protocols became more flexible, usable superconducting 2Q gate yield would increase considerably, enabling more rapid and effective prototyping of 2Q gates which could be scaled to a computer. Furthermore, any number of novel superconducting devices with very fast 2Q gates that happen to be nonstandard could be effectively utilized for computing.

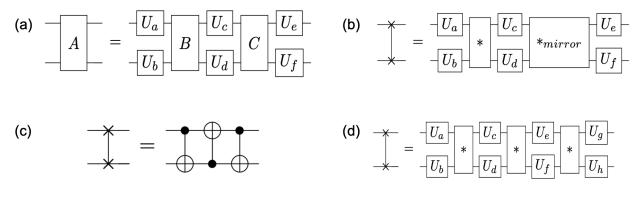

Figure 2.3: (a) Gate A, decomposed into 2 layers with 2Q gates B, C and 1Q gates  $U_a, U_b, U_c, U_d, U_e, U_f$ . (b) A general 2-layer decomposition of the SWAP gate. Here  $*, *_{mirror}$  can be replaced by any pair of 2Q gates capable of synthesizing a SWAP in 2 layers. (c) The SWAP gate, decomposed into 3 CNOT gates. (d) A general 3-layer decomposition of the SWAP gate. Here the \* can be replaced by any 2Q gate capable of synthesizing a SWAP in 3 layers.

## 2.5 Identifying good 2Q basis gates

## 2.5.1 Fidelity of a synthesized gate

If a 2Q quantum gate is not directly supported on a device, it needs to be implemented by alternating layers of 1Q and 2Q gates from the set of basis gates that are directly supported. See Figure 2.3 for examples. We say that a decomposition is n-layer if it contains n layers of 2Q gates. Besides the errors that come from noises in the quantum hardware, a synthesized gate also suffers from the approximation error in gate decomposition. Thus the total fidelity of a gate should be the product of the hardware-limited fidelity and the decomposition fidelity. In this work, the decomposition errors are negligible compared to the hardware errors.

In our error model, decoherence is the dominant source of hardware error. So two factors determine whether a 2Q gate set is ideal for synthesizing a target gate: the duration of the basis gates, and the depth of the decomposition circuit. We need to take both into account when deciding on a strategy for selecting basis gates.

#### 2.5.2 An analytic method for determining 2Q circuit depth

When deciding whether a potential basis gate is ideal for synthesizing a target gate, we consider the depth of the decomposition circuit as one of the factors. Given a 2Q target gate A, and a 2Q gate B (or a gate set S), how to determine the minimum circuit depth required for a decomposition of A into B (or S) and 1Q gates? One can take a practical, numerical approach to finding this decomposition. For a given number of layers, one can fix the 2Q gates and then numerically search for the 1Q gates that can minimize the discrepancy between the target unitary and the synthesized gate. One can start the numerical search from 1 layer, and increment the number of layers until the decomposition error gets below a threshold. But a more efficient and accurate way to determine the circuit depth is to apply the analytic method developed by Peterson et al. [95].

Without going into the technical details, here we summarize a key result from [95] that we adapt and apply in Section 2.5.3 and 2.5.4.

**Theorem 2.5.1.** There exists a 2-layer decomposition of 2Q gate A into B, C, and 1Q gates as in Figure 2.3(a), if and only if any of the 1 to 8 sets of 72 inequalities that depend on the non-local parts of A, B, C is all satisfied.

For details of the theorem, the readers can look at Theorem 23 of [95] or the implementation of the function in our code <sup>1</sup>. Note that Reference [95] characterizes the space of 2Q gates with LogSpec instead of the Cartan coordinates (see [95] for the definition of LogSpec). Both are valid ways to represent the non-local part of a 2Q gate, but care must be taken when converting between the two. A gate U usually maps to 1 point in the Weyl chamber, but it usually maps to 2 points in the LogSpec space: LogSpec(U) = (a, b, c, d)and  $\rho(LogSpec(U)) = (c + \frac{1}{2}, d + \frac{1}{2}, a - \frac{1}{2}, b - \frac{1}{2})$ . If  $LogSpec(U) = \rho(LogSpec(U))$  for all A, B, and C, we only need to check one set of inequalities. If  $LogSpec(U) \neq \rho(LogSpec(U))$

<sup>1.</sup> Our code can be found at https://github.com/SophLin/nonstandard\_2qbasis\_gates

for 1, 2, or all 3 of A, B, and C, we need to plug in different versions of the LogSpec and check 2, 4, or 8 versions of the 72 inequalities, respectively.

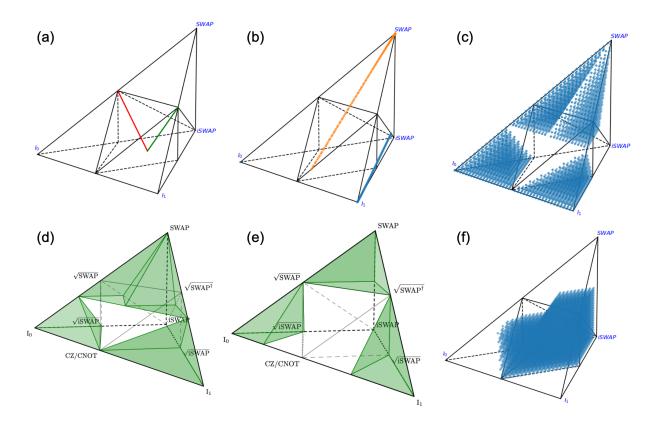

Figure 2.4: (a) Gates that are able to synthesize SWAP in 2 layers form 2 line segments in the Weyl chamber. The red one is from the B gate to  $\sqrt{SWAP}$ , and the green one is from the B gate to  $\sqrt{SWAP}^{\dagger}$ . (b) Pairs of gates that are able to synthesize a SWAP in 2 layers. In blue is an example trajectory that deviates from the standard XY interaction, in orange are the points that would complement the blue ones in synthesizing a SWAP in 2 layers. (c) Gates that are NOT able to synthesize a SWAP in 3 layers. (d) Gates that are NOT able to synthesize a SWAP in 3 layers. The 4 tetrahedra are defined by vertices  $\{I_0, CZ, (\frac{1}{4}, \frac{1}{4}, 0), (\frac{1}{6}, \frac{1}{6}, \frac{1}{6}), (\frac{3}{4}, \frac{1}{4}, 0), (\frac{5}{6}, \frac{1}{6}, \frac{1}{6})\}, \{SWAP, (\frac{1}{2}, \frac{1}{6}, \frac{1}{6}), (\frac{1}{3}, \frac{1}{3}, \frac{1}{6})\}$ , and  $\{SWAP, (\frac{1}{2}, \frac{1}{6}, \frac{1}{6}), (\frac{2}{3}, \frac{1}{3}, \frac{1}{6})\}$ . (e) Gates that are NOT able to synthesize CNOT in 2 layers. The 3 tetrahedra in the plot are defined by vertices  $\{I_0, (\frac{1}{4}, 0, 0), (\frac{1}{4}, \frac{1}{4}, 1), \sqrt{SWAP}\}, \{I_1, (\frac{3}{4}, 0, 0), (\frac{3}{4}, \frac{1}{4}, 0), \sqrt{SWAP}^{\dagger}\}$ , and  $\{SWAP, \sqrt{SWAP}, \sqrt{SWAP}, \sqrt{SWAP}^{\dagger}, (\frac{1}{2}, \frac{1}{2}, \frac{1}{4})\}$ . (f) Gates that are able to decompose SWAP in 3 layers.

# 2.5.3 Synthesis of the SWAP gate

On bounded connectivity architectures, SWAPs make up a significant portion of all twoqubit gates. A SWAP gate exchanges the quantum states of two neighboring qubits. A 2Q gate in a quantum program can be directly scheduled if it acts on two physical qubits that are connected to each other, but this is not the case in general. Superconducting devices are usually designed to have sparse connectivity, because otherwise crosstalk errors would be difficult to suppress. As a result, quantum programs usually contain a large proportion of SWAP gates after they are compiled to run on a superconducting device.

When we select the 2Q basis gate set for each pair of qubits, a top priority is to optimize the fidelity of the SWAP gate that is built from the gate set. We discuss three approaches towards synthesizing a SWAP gate: decompose it into 1, 2, or 3 layers of hardware 2Q gates.

**SWAP in 1 layer:** This requires a basis gate that is locally equivalent to SWAP. In other words, the trajectory of the available native gates needs to pass through the top vertex of the Weyl chamber.

SWAP in 2 layers: We consider 2 cases: 2-layer decomposition of SWAP using a single 2Q basis gate, and using two different 2Q basis gates.

In the first case, the set of 2Q gates that are capable of synthesizing SWAP in 2 layers are represented by 2 line segments in the Weyl chamber as shown in Figure 2.3(b). One is from the B gate to  $\sqrt{SWAP}$  and the other is from B to  $\sqrt{SWAP}^{\dagger}$ . We denote them by  $L_0$ and  $L_1$ , respectively.

In the second case, for each point \* in the Weyl chamber, (as derived in 2.10.2) there is exactly one point  $*_{mirror}$  such that they together enable a 2-layer decomposition of SWAP (see Figure 2.3(b)). The line segment from \* to  $*_{mirror}$  always has one of  $L_0, L_1$  as its perpendicular bisector. Thus, given \*, we can locate  $*_{mirror}$  by rotating \* by  $\pi$  around the closer one of  $L_0, L_1$ . One example pair of such points is CNOT and iSWAP. For a trajectory that deviates from the standard XY trajectory (goes from Identity to a point near iSWAP), its "mirror" is a trajectory from SWAP to a point near CNOT (Figure 2.4(b)). Since there's no overlap between the example trajectory and the "mirror", we conclude that the trajectory does not contain any pair of points that is able to synthesize SWAP together in 2 layers.

**SWAP in 3 layers:** It is a well-known result that 3 invocations of CNOT are required to implement a SWAP [106]. We show the circuit in Figure 2.3(c). In fact, CNOT and iSWAP share the property that they can synthesize any arbitrary 2Q gate in 3 layers but only a 0-volume set of gates (in the Weyl chamber) in 2 layers [95].

For our purpose, we need to know what other gates are capable of decomposing SWAP in 3 layers. We only consider 3-layer decomposition of SWAP using a single 2Q basis gate as in Figure 2.3(d). Let  $S_{SWAP,3}$  denote the set of gates that satisfy our requirement. To determine whether a 2Q basis gate G is in  $S_{SWAP,3}$ , we first locate the corresponding  $G_{mirror}$  such that G and  $G_{mirror}$  together can provide a 2-layer decomposition of SWAP. Then we apply Theorem 2.5.1 with  $G_{mirror}$  as target and G as basis gate to check if there exists a 2-layer decomposition of  $G_{mirror}$  into G.