### THE UNIVERSITY OF CHICAGO

## LARGE-SCALE TENSOR NETWORK QUANTUM ALGORITHM SIMULATOR

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES DIVISION IN CANDIDACY FOR THE DEGREE OF MASTERS

### DEPARTMENT OF COMPUTER SCIENCE

BY

DANYLO LYKOV

CHICAGO, ILLINOIS FEBRUARY 2024

Copyright © 2024 by Danylo Lykov All Rights Reserved

# TABLE OF CONTENTS

| 4  | PAR  | ALLEL COMPUTATION                          | 44 |

|----|------|--------------------------------------------|----|

|    | 4.1  | Introduction                               | 44 |

|    | 4.2  | Related Work                               | 44 |

|    | 4.3  | Methodology                                | 46 |

|    |      | 4.3.1 QAOA introduction                    | 46 |

|    |      | ·                                          | 47 |

|    | 4.4  |                                            | 48 |

|    |      | <u> </u>                                   | 48 |

|    |      | v                                          | 49 |

|    | 4.5  | 1                                          | 52 |

|    |      | 0 1                                        | 52 |

|    | 4.6  | 0 0                                        | 54 |

|    | 2.0  |                                            | 55 |

|    |      | 1                                          | 56 |

|    |      | 0 1                                        | 59 |

|    |      |                                            | 62 |

|    | 4.7  | 1 1                                        | 65 |

|    | 4.8  | 1                                          | 66 |

|    | 4.9  |                                            | 67 |

|    | _    |                                            | 68 |

|    | 1.10 | remowledgements                            | 00 |

| 5  | GPU  | ACCELERATION OF TENSOR NETWORK CONTRACTION | 70 |

|    | 5.1  | Introduction                               | 70 |

|    | 5.2  |                                            | 71 |

|    |      | Ot                                         | 71 |

|    |      | ·                                          | 73 |

|    |      |                                            | 74 |

|    |      | <u> </u>                                   | 75 |

|    |      |                                            | 76 |

|    | 5.3  | · ·                                        | 79 |

|    |      |                                            | 79 |

|    |      |                                            | 81 |

|    |      |                                            | 82 |

|    |      |                                            | 83 |

|    |      |                                            | 84 |

|    | 5.4  | ·                                          | 88 |

|    | J. 1 |                                            |    |

| 6  | CON  | CLUSIONS AND OUTLOOK                       | 91 |

| RE | EFER | ENCES                                      | 93 |

# LIST OF FIGURES

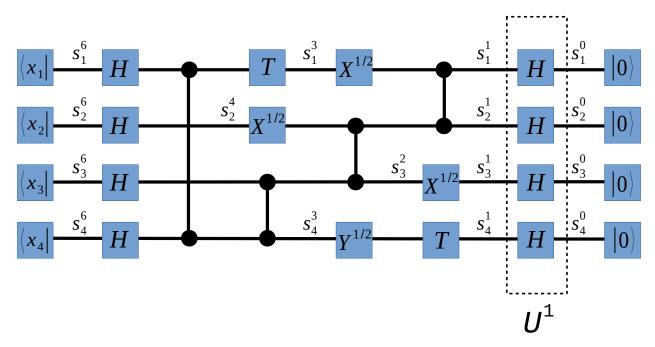

| 2.1        | Example of quantum circuit drawn as a tensor network. The state of <i>i</i> -th qubit at <i>t</i> -th clock cycle is denoted by $\{s\}_{i}^{t}$ (only unique states are shown, e.g. $s_{1}^{2} = s_{1}^{1}$                                    | 1.4 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | is omitted). The time flows from right to left                                                                                                                                                                                                 | 14  |

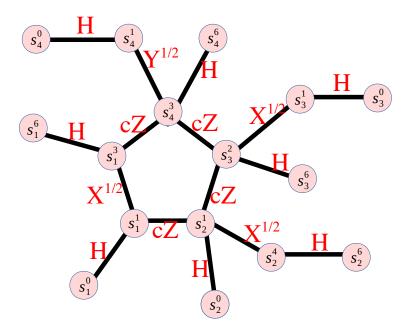

| 2.2<br>2.3 | The mapping between two graph-based notations of tensor networks Alternative representation (graphical model) of the circuit in Fig. 2.1. Gate                                                                                                 | 15  |

| 2.4        | tensors are shown in red, self-loops are omitted                                                                                                                                                                                               | 16  |

| 2.5        | contractions $\pi$ is the same as in Eq. 2.6. Labels of tensors are shown in red Alternative contraction of a tensor network in Eq. 2.5. The maximal clique of                                                                                 | 17  |

| 2.6        | size 4 is highlighted in red. This sequence of contractions is not optimal Evaluation of amplitude subsets. Top - extended amplitude expression to evaluate                                                                                    | 18  |

| 0.7        | all amplitudes of qubits 2, 3, 4; Bottom - resulting amplitude tensor                                                                                                                                                                          | 20  |

| 2.7<br>2.8 | Building a chordal graph from the elimination order                                                                                                                                                                                            | 22  |

| 2.9        | on the number of qubits                                                                                                                                                                                                                        | 28  |

|            | size. Estimated number of floating point operations for the simulation of the full subset of amplitudes of $ C $ qubits (there are $2^{ C }$ amplitudes). In case of one                                                                       |     |

| 2.10       | amplitude at a time simulation a combined cost of all tasks is drawn                                                                                                                                                                           | 28  |

|            | varying size                                                                                                                                                                                                                                   | 29  |

| 2.11       | Floating point to memory access ratio during the simulation of random circuits of varying size                                                                                                                                                 | 30  |

| 3.1        | Quantum circuit that generates QAOA ansatz state for MaxCut problem on a 4-node complete graph. This widely used decomposition of QAOA into common set of basis gates is not optimal for the classical simulation of the output state          | 32  |

| 3.2        | Line graphs of tensor networks for calculating QAOA ansatz state using different optimizations. "Default" and "diagonal" show line graphs of tensor network                                                                                    | 52  |

|            | for the circuit shown in Figure 3.1, using a full-matrix gates and diagonal gates approach, respectively. "ZZ gates + diagonal" is obtained by using the diagonal gates approach on a simplified quantum circuit obtained by applying Equation |     |

|            | 3.4. This figure demonstrates how improving the conversion of a quantum algorithm to a tensor network can reduce the complexity of the network, providing                                                                                      |     |

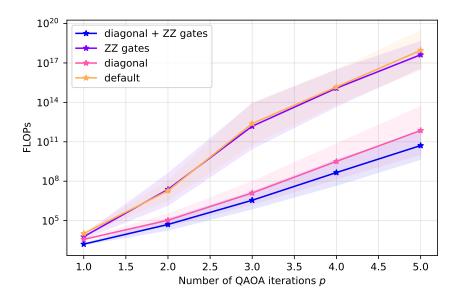

| 3.3        | speedups for both finding contraction order and the contraction itself Number of FLOPs to calculate a single amplitude of QAOA ansatz state for Max-                                                                                           | 33  |

|            | Cut using a different number of QAOA iterations. Each line shows a combination of optimization techniques, with "diagonal + ZZ gates" being the most advanced                                                                                  |     |

|            | one. The shaded region shows 1- $\sigma$ interval over 5 random graphs                                                                                                                                                                         | 39  |

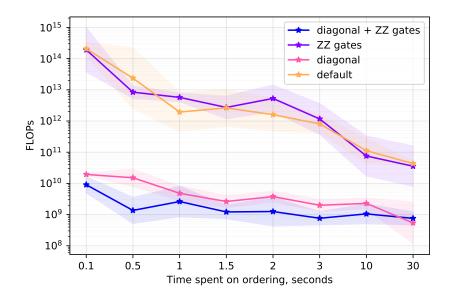

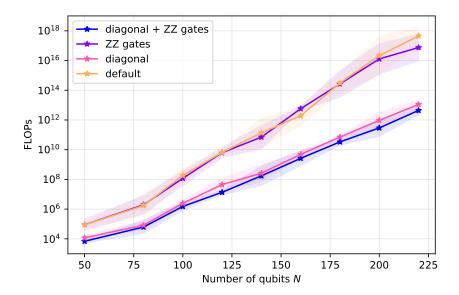

| 3.4        | Number of FLOPs to calculate a single amplitude of QAOA ansatz state with $p=1$ for MaxCut on random 3-regular graphs with 160 nodes. The shaded region shows 1- $\sigma$ interval over 5 random graphs                                                          | 39         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | random graphs.                                                                                                                                                                                                                                                   | 41         |

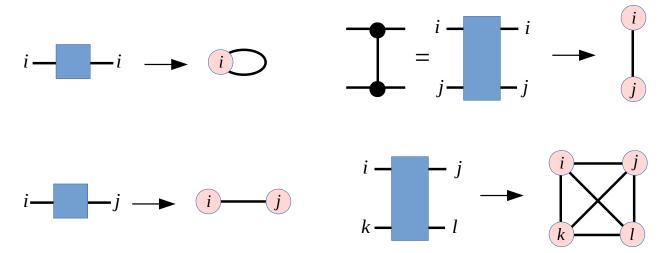

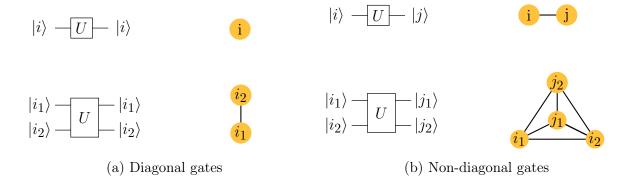

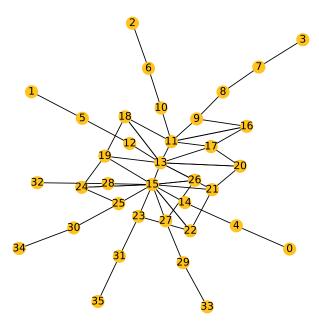

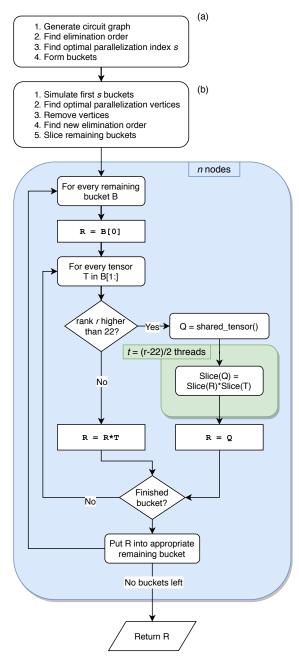

| 4.1<br>4.2 | Correspondence of quantum gates and graphical representation                                                                                                                                                                                                     | 49         |

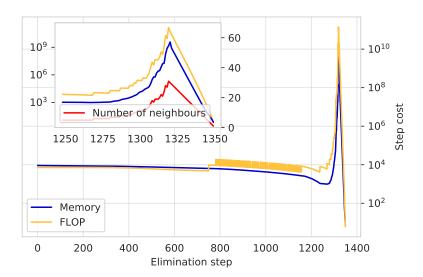

| 4.3        | statevector. Self-loop edges are not shown (in particular $Z^{2\gamma}$ , which is diagonal). Cost of contraction for every vertex for a circuit with 150 qubits. Inset shows the peak magnified and the number of neighbors of the vertex contracted at a given | 50         |

|            | step (right y-axis).                                                                                                                                                                                                                                             | 51         |

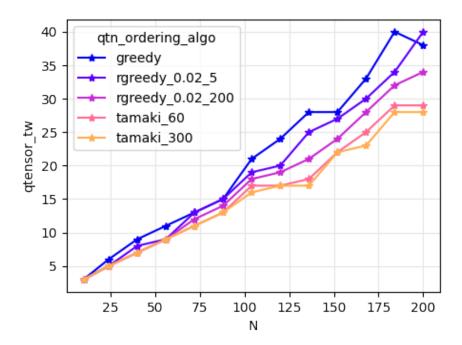

| 4.4        | Comparison of different ordering algorithms for single amplitude simulation of                                                                                                                                                                                   | 50         |

| 4.5        | QAOA ansatz state                                                                                                                                                                                                                                                | 52         |

|            | On the lower level of a single node, we use thread-based parallelization with a                                                                                                                                                                                  |            |

| 4.6        | shared resulting tensor                                                                                                                                                                                                                                          | 57         |

|            | of the bucket processing is omitted for simplicity                                                                                                                                                                                                               | 60         |

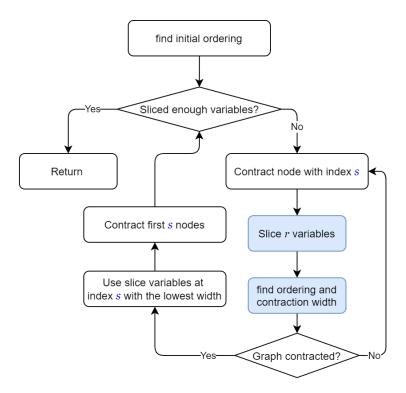

| 4.7        | Step-based slicing algorithm. The blue boxes are evaluated for each graph node                                                                                                                                                                                   | 0.4        |

| 4.0        | and are the main contributions to time                                                                                                                                                                                                                           | 64         |

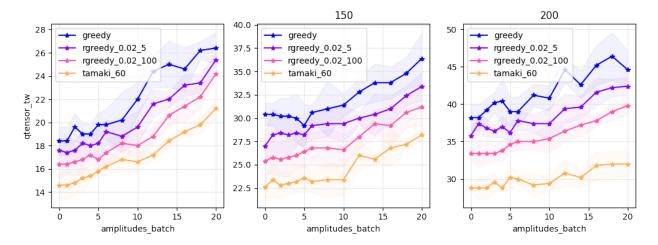

| 4.8        | Simulation cost for a batch of amplitudes. The calculations are done for 5 random instances of degree-3 random regular graphs and the mean value is plotted. The                                                                                                 | <b>6</b> 7 |

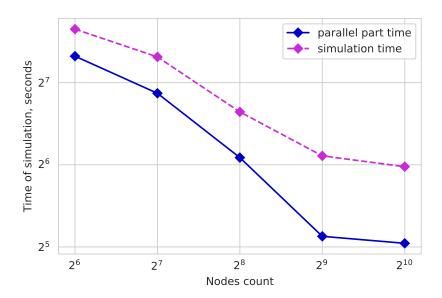

| 4.9        | three plots are calculated for different number of qubits: 100, 150 and 200 Experimental data of simulation time with respect to the number of Theta nodes.                                                                                                      | 65         |

|            | The circuit is for 210 qubits and 1,785 gates.                                                                                                                                                                                                                   | 66         |

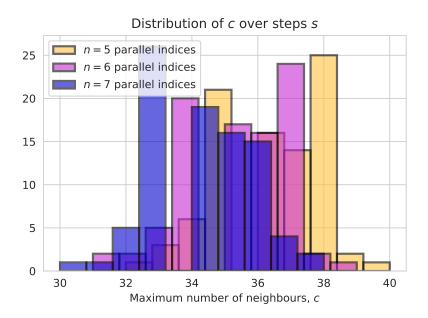

| 4.10       | Distribution of the contraction width (maximum number of neighbors) $c$ for different numbers of parallel indices $n$ . While variance of $c$ is present, showing that it is sensible to the parallelization index $s$ , we are interested in the minimal value  |            |

|            | of $s$ , which, in turn, generally gets smaller for bigger $n$                                                                                                                                                                                                   | 69         |

|            |                                                                                                                                                                                                                                                                  |            |

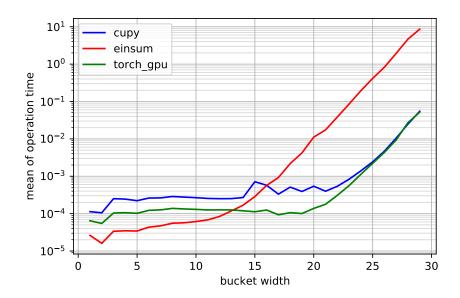

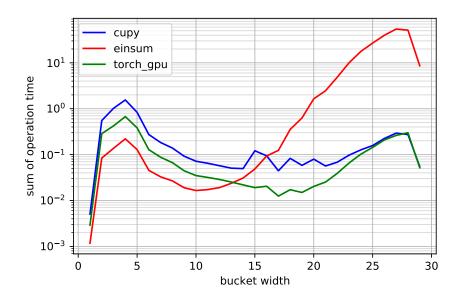

| 5.1 | Breakdown of mean time to contract a single bucket by bucket width. The test is performed for expectation value as described in 5.3.1. CPU backends are faster     |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | for buckets of width $\leq 13 - 16$ , and GPU faster are better for larger buckets.                                                                                |     |

|     | This picture also demonstrates that every contraction operation spends some                                                                                        |     |

|     | time on overhead which doesn't depend on bucket width, and actual calculation                                                                                      |     |

|     | that scales exponentially with bucket width                                                                                                                        | 79  |

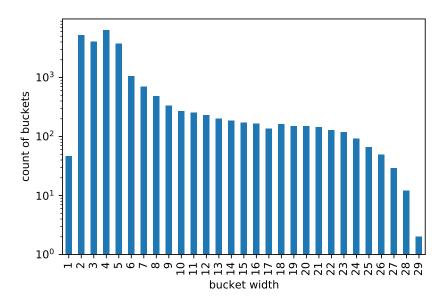

| 5.2 | Distribution of bucket width in the contraction of QAOA full circuit simulation.                                                                                   | 13  |

| 0.2 | The y-axis is log scale; 82% of buckets have width $\leq 6$ , which have relatively                                                                                |     |

|     | large overhead time                                                                                                                                                | 80  |

| 5.3 | Breakdown of total time spent on bucket of each size in full QAOA expectation                                                                                      |     |

|     | value simulation. The y-value on this plot is effectively one in Figure 5.1 multi-                                                                                 |     |

|     | plied by one in Figure 5.2. This figure is very useful for analyzing the bottlenecks                                                                               |     |

|     | of the simulation. It shows that most of the time for CPU backend is spent on                                                                                      |     |

|     | large buckets, but for GPU backends the large number of small buckets results                                                                                      |     |

|     | in a slowdown.                                                                                                                                                     | 80  |

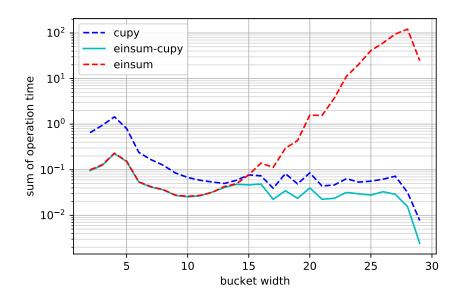

| 5.4 | Breakdown of total contraction time by bucket width in full expectation value                                                                                      |     |

|     | simulation of problem size 30. Lines with the same color use the same type of                                                                                      |     |

|     | backends. The solid lines represent the merged version of backends, and the                                                                                        |     |

|     | dashed lines denote the baseline backends. The merged GPU backends are better                                                                                      |     |

|     | for buckets of width $\geq 20$                                                                                                                                     | 82  |

| 5.5 | Breakdown of sum contraction time by bucket width for merged backends. CPU                                                                                         |     |

|     | backends are better for buckets of width $\leq 15$ , and GPU backends are better                                                                                   |     |

|     | for larger buckets. The hybrid backend's GPU backend spends outperforms the                                                                                        | 0.5 |

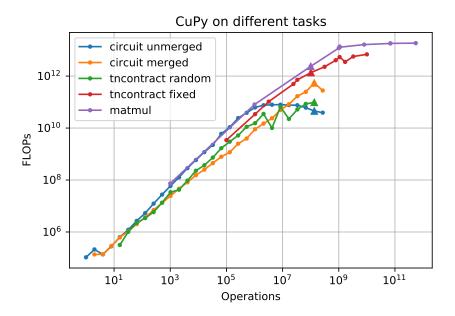

| 5.6 | regular GPU backend for buckets of width $\geq 15$                                                                                                                 | 85  |

| 5.6 | FLOPs vs. the number of operations for all tasks on the CuPy backend. "circuit unmerged" and "circuit merged" are results of expectation value of the full circuit |     |

|     | simulation of QAOA MaxCut problem on a 3-regular graph of size 30 with depth                                                                                       |     |

|     | p=4. "tncontract random" tests on tensors of many indices where each index has                                                                                     |     |

|     | a small size. "theontract fixed" uses the contraction sequence "abcd,bcdf $\rightarrow$ acf"                                                                       |     |

|     | for all contractions. "matmul" performs matrix multiplication on square matrices.                                                                                  |     |

|     | All groups use complex128 tensors in the operation. We use the triangles to                                                                                        |     |

|     | denote the data at $\sim 100$ million operations, which is shown in Table 5.3                                                                                      | 88  |

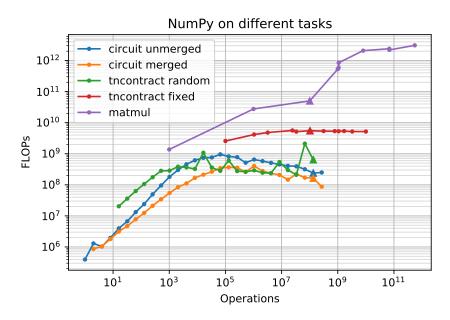

| 5.7 | FLOPs vs. the number of operations for all tasks on NumPy backend. Same                                                                                            |     |

|     | problem setting as Fig. 5.6. "tncontract random" outperforms "tncontract fixed"                                                                                    |     |

|     | as the ops value increases. Merged backend does not have an advantage on CPU                                                                                       |     |

|     | compared to the unmerged backend. We use the triangles to denote the data at                                                                                       |     |

|     | $\sim 100$ million operations, which is shown in Table 5.3                                                                                                         | 89  |

# LIST OF TABLES

| 3.1 | The maximum number of QAOA iterations $p$ for which one can simulate a single amplitude of ansatz state for MaxCut on a 40-node random regular graph                                                                                                                                                                                                                                                                     | 42 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | The maximum number of nodes of a 3-regular graph for which one can simulate a single amplitude of the MaxCut QAOA ansatz state                                                                                                                                                                                                                                                                                           | 42 |

| 4.1 | Comparison between different notations of quantum circuits                                                                                                                                                                                                                                                                                                                                                               | 49 |

| 4.2 | Hardware and software specifications                                                                                                                                                                                                                                                                                                                                                                                     | 56 |

| 5.1 | Time for full QAOA expectation value simulation using backend that utilize GPUs or CPUs. The expectation value is MaxCut on a 3-regular graph of size 30 and QAOA depth $p=4$ . <b>Speedup</b> shows the overall runtime improvement compared with the baseline CPU backend "NumPy". "Mixed" device means the backend uses both CPU                                                                                      |    |

|     | and GPU devices                                                                                                                                                                                                                                                                                                                                                                                                          | 83 |

| 5.2 | Time for full QAOA expectation value simulation using different Merged backends, as described in Section 5.2.3. The expectation value is MaxCut on a 3-regular graph of size 30 and QAOA depth $p = 4$ . <b>Speedup</b> shows the overall runtime improvement                                                                                                                                                            |    |

|     | compared with the baseline CPU backend "NumPy"                                                                                                                                                                                                                                                                                                                                                                           | 84 |

| 5.3 | Summary of GPU and CPU FLOPs for different tasks at around 100 million operations. Matrix Multiplication and Tensor Contraction tasks are described in Section 5.3.5. "Bucket Contraction" groups record the maximum number of FLOPs for a single bucket. "Lightcone Contraction" groups contain the FLOPs data on a single lightcone where the sum of operations is approximately 100 millions, small and large buckets |    |

|     | combined                                                                                                                                                                                                                                                                                                                                                                                                                 | 86 |

## **ABSTRACT**

As quantum computing field is starting to reach the realm of advantage over classical algorithms, simulating quantum circuits becomes increasingly challenging as we design and evaluate more complex quantum algorithms. In this context, tensor networks, which have become a standard method for simulations in various areas of physics, from many-body quantum physics to quantum gravity, offer a natural approach. Despite the availability of efficient tools for physics simulations, simulating quantum circuits presents unique challenges, which I address in this work, specifically using the Quantum Approximate Optimization Algorithm as an example.

The main results of this work span several steps of the problem. For the step of creating a tensor network, I demonstrate that applying the diagonal representation of quantum gates leads to a complexity reduction in tensor network contraction by one to four orders of magnitude.

For large-scale contraction of tensor networks, I propose a step-dependent parallelization approach which performs slicing of partially contracted tensor network. Finally, I study tensor network contractions on GPU and propose an algorithm of contraction which uses both CPU and GPU to reduce GPU overhead. In our benchmarks, this algorithm reduces time to solution from 6 seconds to 1.5-2 seconds.

### CHAPTER 1

#### INTRODUCTION

The science of classically simulating quantum many-body physics involves exponential scaling of memory resources. The fact that quantum many-body systems are hard to simulate classically is the basis for the idea of quantum computing as first suggested by Richard Feynman [Feynman, 1982].

Growing interest in quantum computing in recent years led to the increase of size and capabilities of experimental quantum computers. Promising physical realizations of quantum computing devices were implemented in recent years [Intel, 2018; IBM, 2018], which bolsters the expectations that a long thought quantum supremacy will be reached [Harrow and Montanaro, 2017; Boixo et al., 2018; Neill et al., 2018].

Quantum information science has a tremendous potential to speed up calculations of certain problems over classical calculations [Alexeev et al., 2021; Shor, 1994]. To continue the advances in this field, however, often requires classically simulating quantum circuits. Such simulation is done by using classical simulation algorithms that replicate the behavior of executing quantum circuits on classical hardware such as personal computers or high-performance computing (HPC) systems. These algorithms play an important role and can be used to (1) verify the correctness of quantum hardware, (2) help the development of hybrid classical-quantum algorithms, (3) find optimal circuit parameters for hybrid variational quantum algorithms, (4) validate the design of new quantum circuits, and (5) verify quantum supremacy and advantage claims.

Tensor networks are an invaluable tool for the classical simulation of both quantum computers and general physical systems. For example, in the domain of molecular quantum dynamics the Multi-layer multi-configuration time-dependent Hartree (ML-MCTDH) [Wang and Thoss, 2003] algorithm, which is an extension of MCTDH [Meyer et al., 1990] algorithm, achieved significant recognition. This algorithm uses tensor networks to represent quantum

states and then solve the underlying dynamics equations.

Moreover, tensor networks can be used to exactly calculate the partition function of quantum many-body systems [Vanderstraeten et al., 2018]. The partition function can then be used to extract useful information about the system, such as energy or specific heat capacity.

#### 1.1 Tensor networks introduction

## 1.1.1 Tensors and quantum states

A vector is an entity with magnitude and direction, often used to represent physical quantities such as velocity or force. In contrast, a covector (or one-form) is a linear map from vectors to scalars. Both can be represented as an array of numbers in a given basis, but when the basis is changed they transform oppositely to ensure that all scalars are invariant, a key principle in physics and geometry.

Expanding to two dimensions, we distinguish between bilinear forms and linear maps from one vector space to another. A bilinear form takes two vectors as input and returns a scalar. Interestingly, a linear map can also be viewed as a bilinear map taking a covector and a vector as input, producing a scalar. Similarly to vectors and covectors, both bilinear forms and linear maps can be represented as matrices, and special rules are used to change the representation when changing the basis.

A tensor generalizes these ideas further. A tensor of rank n is a n-linear map from a mix of n vectors and covectors to a scalar. To specify a tensor, one has to provide a representation in some basis and the rules for changing the representation under a change of basis. Examples of tensors in physics include the electromagnetic tensor  $F_{\mu\nu}$  and the Levi-Civita tensor, among many others.

In the context of quantum computing and computer science, the basis is often fixed

forever, and a tensor is just a representation: an array of numbers that is indexed by several indices. The number of indices is called *order* or sometimes rank or mode of a tensor and the index is sometimes called the dimension. The number of values that an index can have is usually called the size of the index. For instance, a scalar, is a single number is labeled by zero indices, so a scalar is considered to be a 0th-order tensor. A vector is a tensor of first order and a matrix is a tensor of second order. In the case of quantum physics, tensors can be used for the representation of states. For example, a first-order tensor can be used to represent the state vector of a spin- $\frac{1}{2}$  particle in some basis:

$$|\psi_1\rangle = C_0 |0\rangle + C_1 |1\rangle = \sum_{s=0,1} C_s |s\rangle.$$

(1.1)

The  $|0\rangle$  and  $|1\rangle$  are basis vectors that correspond to, for instance, spin-up and spin-down states. The vector  $C_s$  is a first-rank tensor that represents this state given the basis  $|0\rangle$ ,  $|1\rangle$ . This approach can be extended to a tensor of two particles:

$$|\psi_2\rangle = C_{00}|00\rangle + C_{01}|01\rangle + C_{10}|10\rangle + C_{11}|11\rangle = \sum_{s_1, s_2=0}^{1} C_{s_1, s_2}|s_1 s_2\rangle,$$

(1.2)

where a common notation is used  $|ab\rangle = |a\rangle \, |b\rangle = |a\rangle \otimes |b\rangle$ .

In quantum physics, it is common to use a state vector with a dimension of size 4 to represent a state of such a system. The difference in representing it as a second-order tensor as above is just the way of labeling the numbers, but such notation is the first step towards impressive advantages for classical simulation of tensor networks.

As a natural extension for a system of N spins, one can use the following representation of the state:

$$|\psi_N\rangle = \sum_{s_1...s_N=0}^{1} C_{s_1...s_N} |s_1...s_N\rangle.$$

(1.3)

Similarly, the tensor  $C_{s_1...s_N}$  can be reshaped into a vector of size  $2^N$ . The above ex-

amples were for spin- $\frac{1}{2}$  systems, but the approach is the same for collections of quantum systems with larger state space.

It is important to note that since the basis is fixed, there is no classification of indices into covariant and contravariant, e.g. there is no distinction between indices for bra- and ket-states, which is a common distinction in tensors used in physics.

### 1.1.2 Tensor networks

As described above it may seem that tensors are not more useful than just vectors, after all the difference lies only in labeling the numbers. It is when tensors are combined with each other into a tensor network, that the true usefulness appears. A tensor network is a product of tensors, which can share indices between each other. For example, the expression  $A_{ij}B_{jk}$  is a tensor network. This tensor network can be viewed as a tensor itself, which is indexed by indices ijk. Each value of the tensor is a product of two elements from tensors A and B:

$$T_{ijk} = A_{ij}B_{jk}. (1.4)$$

Tensor networks are widely used to represent a linear mathematical model of the studied system. The fact that the model is linear means that the values of interest are a sum of products of numbers, which are input parameters to the model. For example, when modeling rotation of a solid, to obtain coordinates of the rotated geometry, one uses a linear map on a 2-D vector space. The first component of resulting coordinates will be  $u_0 = A_{00}v_0 + A_{01}v_1$ , and the second  $u_1 = A_{10}v_0 + A_{11}v_1$ , where  $v_i$  are the initial coordinates and  $A_{ij}$  are the rotation parameters. The initial  $v_i$  and rotated  $u_i$  vectors and the matrix  $A_{ij}$  are all tensors, so we can use a summation over a tensor network to represent such a linear model:

$$u_i = \sum_{j=0,1} A_{ij} v_j = \sum_{j=0,1} K_{ij}.$$

(1.5)

The example in the Equation (1.4) can be used to represent a matrix multiplication:

$$C_{ik} = \sum_{j=0,1} T_{ijk} = \sum_{j=0,1} A_{ij} B_{jk}.$$

(1.6)

In order to compute the values for the tensor C it is not required to store all the elements of tensor T in memory at the same time. Instead it is possible to evaluate each element  $C_{ij}$  by evaluating corresponding entries  $T_{ijk}$ , then performing the summation, and finally discarding the used entries, thus saving memory. The process of evaluating a sum is called a *contraction* of a tensor network. For example, in equation (1.6) the tensor network is contracted over index j.

More complex tensor networks can have summation over many indices and have hundreds or thousands of tensors and indices. They can be used to represent more complex models, such as hidden Markov chains [Gillman et al., 2020] or probabilistic graphical models [Miller et al., 2021; Carrasquilla et al., 2019]. They are also remarkably efficient at representing quantum circuits and states of many-body quantum systems. In addition to exact representations, tensor networks are widely used in algorithms for approximately calculating quantum many-body systems of large size or infinite size. The most popular algorithm is known as Density Matrix Renormalization Group (DMRG) [Schollwöck, 2011] which uses the representation of Matrix Product State (MPS) in case of a chain of a quantum system to approximately calculate the ground state or arbitrary observables of the systems [Orús, 2014].

## 1.2 Quantum computing introduction

Quantum computers are physical systems that allow the implementation of arbitrary transformations of a quantum state. A quantum computer consists of several qubits, which can interact with each other. In a classical computer, computation is performed by taking input

information represented as bits of data, then applying some operations to it to calculate some useful output data. The operations are composed of elementary logic gates that calculate some output value from input bits. Examples of classical logic gates are  $NOT(b_0)$  which flips the input bit, and  $AND(b_0, b_1)$  which outputs a binary sum of input bits.

Each qubit in a quantum computer is conceptually similar to a bit in a classical computer. Usually, it is a two-level quantum system, analogous to spin- $\frac{1}{2}$  particle. In order to describe computation on a quantum computer, we use quantum gates. Each quantum gate acts on one or several qubits and transforms the corresponding state. For example, when a one-qubit gate is applied to a single qubit in the state  $|0\rangle$ , the transformation is described as

$$\hat{U}|s\rangle = U_{0s}|0\rangle + U_{1s}|1\rangle = |\psi\rangle, \qquad (1.7)$$

where s is a binary variable that labels the qubit basis. Examples of quantum gates are Pauli rotations  $\hat{\sigma}_x$ ,  $\hat{\sigma}_y$ , and  $\hat{\sigma}_z$ . Another widely used gate is called Hadamard gate:

$$\hat{H} = \frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 1\\ 1 & -1 \end{pmatrix} \tag{1.8}$$

If a quantum gate is applied to i-th qubit in a quantum computer with N qubits, the change of state is following:

$$\hat{U}^{i} |0_{0}0_{1} \dots s_{i} \dots 0_{N}\rangle = c_{0s} |0_{0}0_{1} \dots 0_{i} \dots 0_{N}\rangle + c_{1s} |0_{0}0_{1} \dots 1_{i} \dots 0_{N}\rangle = |\psi\rangle.$$

(1.9)

Now we can apply the framework of tensor networks to describe such operation:

$$\hat{U}^{i} \sum_{s_{1}...s_{N}=0}^{1} C_{s_{1}...s_{N}} |s_{1}...s_{N}\rangle = \sum_{s_{1}...s_{N}=0}^{1} C_{s_{1}...s_{N}} \hat{U}^{i} |s_{1}...s_{N}\rangle$$

(1.10)

$$= \sum_{s_1...s_N=0}^{1} C_{s_1...s_N} \sum_{s_{N+1}} U_{s_{N+1}s_i} |s_1...s_N\rangle$$

(1.11)

$$= \sum_{s_m=0, m \in \{1...N+1\}, m \neq i}^{1} D_{s_1...s_{N+1}} |s_1...s_N\rangle.$$

(1.12)

The last summation is performed over all indices  $s_i$  for i = 1...N + 1 except index  $s_i$  which was contracted. We can omit the basis kets and the summation over those and concentrate on just the tensors that represent the states.

$$\sum_{s_j} U_{s_{N+1}s_j} C_{s_0 s_1 \dots s_j \dots s_N} = D_{s_0 s_1 \dots s_{N+1} \dots s_N}. \tag{1.13}$$

In a case of a two-qubit gate, we can represent the resulting state in a similar way, using a 4-th order tensor instead

$$\sum_{i_j i_k} W_{i_{N+2} i_{N+1} i_j i_k} C_{s_0 s_1 \dots s_j \dots s_k \dots s_N} = D_{s_0 s_1 \dots i_{N+2} \dots i_{N+1} \dots s_N}.$$

(1.14)

#### 1.3 Structure

In this work, I start with Chapter 2 on using tensor networks for the classical simulation of quantum circuits. I describe how a quantum circuit may be converted to a tensor network and how its contraction is used to obtain different properties of the quantum circuit. In particular, this chapter describes an efficient method for simulating a batch probability amplitudes in one tensor network contraction.

The conversion of quantum circuit to a tensor network may be tweaked to produce significant reductions in tensor network complexity and its computational cost. In Chapter 3 I

demonstrate a significant improvement when using the diagonal gates approach in application to circuits for Quantum Approximate Optimization Algorithm (QAOA).

Next, in Chapter 4 I discuss how to efficiently contract a tensor network, given a set of classical hardware resources. In particular, I explore various parallelization approaches based on slicing the tensor networks that are crucial for large-scale simulations. In Chapter 5 I explore using GPU for tensor network contraction and propose an algorithm for dynamic balancing of tensor contraction steps between CPU and GPU.

Finally, Chapter 6 summarizes the work in this thesis and provides possible avenues for future research.

## CHAPTER 2

## TENSOR NETWORK SIMULATION OF QUANTUM CIRCUITS

This chapter is adapted from the publication by Schutski, Lykov, and Oseledets [2020].

### 2.1 Introduction

Substantial progress has been made in understanding quantum computation and developing classical simulators of quantum circuits. Efficient simulators were developed for highly parallel computers, such as Sunway Taihulight [Li et al., 2018]. At the moment the simulation software is aimed at either one of two tasks. The first one is predicting the probability of measuring a particular binary string as the result of a quantum program, or single amplitude simulation. The second is obtaining the full distribution of quantum circuit outputs, or full state simulation. The first approach was found more economical in terms of memory a classical computer has to use, thus allowing the simulation of few amplitudes of larger quantum circuits on up to 100 qubits [Chen et al., 2018b]. On the other hand, the second approach may be preferred when the full state information is needed, such as in Shor's algorithm [Shor, 1994].

In this chapter, we present a unified approach to quantum circuit simulation. The user can choose the number of probabilities of bitstrings to simulate in a single pass. Our algorithm allows one to balance between the amount of available computational resources and the overall time of the simulation. We build our work on the connection between graphical models and quantum circuits introduced by Markov and Shi [2008] and later developments by [Boixo et al., 2017] and other authors. A relevant research work was presented by Pednault et al. [2017]. We find that our approach is more straightforward, as it disentangles the problem of multiple amplitude simulation from the parallelization. We defer a more detailed comparison to a later section. An overview of the chapter is as follows.

In Section 2.2 we compare our approach to existing techniques. In Sec. 2.3, we review the connection of quantum circuits, tensor diagrams, and statistical graphical models. We then proceed by describing a basic algorithm for circuit simulation based on [Markov and Shi, 2008; Boixo et al., 2017]. In Sec. 2.4 we formulate the main problem solved in this work, which is batch simulation of amplitudes. To solve it, we recall the tree decomposition of graphs and its connection to the problem of ordering of graph nodes. We then propose a new algorithm to transform graph orderings while preserving treewidth (which is the measure of quality) of the given ordering. To achieve a proper transformation we use the connection of tree decomposition and chordal graphs, as explained in 2.4.2 and 2.4.3. Numerical experiments are listed in Sec. 2.4.4. Finally, we conclude in Sec. 2.5 with final remarks and outline possible future research.

#### 2.2 Related work

The problem of efficient tensor contraction was approached multiple times in the field of many-body physics and quantum computing. Some older works are based on the sequential application of sparse matrices to the state vector, such as in [De Raedt et al., 2007]. The authors issued a follow-up paper recently [De Raedt et al., 2019]. Their simulator can evaluate both full sets and subsets of amplitude tensor. This direct simulation procedure, however, requires a lot of non-trivial techniques to make it efficient, especially if parallel operation is considered. Another problem is that it is hard to analyze the effectiveness of the algorithm compared to theoretical bounds on the numerical cost [Aaronson and Chen, 2016]. The latter fact has lead to the previously believed threshold of 50 qubits for "quantum supremacy".

The seminal work of Markov and Shi [2008] introduced tensor networks for quantum algorithm simulations and showed that treewidth is a natural measure of simulation hardness.

The graph-based notation became standard in tensor network literature a decade ago [Bridge-

man and Chubb, 2017]. Following Markov and Shi, several groups developed highly efficient algorithms for quantum circuit simulation based on this representation, see [Pfeifer et al., 2014; Chen et al., 2018c; Pednault et al., 2017; Li et al., 2018] for more details. The previous threshold of 50 qubits was raised, as is demonstrated by multiple authors [Chen et al., 2018c; Pednault et al., 2017; Li et al., 2018]. Usually, these simulators are capable of evaluating full state vectors as well as some subsets of the amplitudes. A similar program was created for contraction of tensors emerging in the many-body physics community [Pfeifer et al., 2014]. The drawback of the approaches based on tensor diagrams is the hardness of the development of efficient codes and the theoretical performance analysis, especially if parallelization is involved. To see why, let us note that classical tensor networks were developed to represent pairwise contractions. Quantum circuits often involve multiple diagonal gates, which allows for significant computational savings. The treewidth of classical diagram's graphs is higher than optimal (see Appendix in [Boixo et al., 2017]). Traditional network notation can be understood as a hypergraph to eliminate this drawback, as was done in [Pednault et al., 2017]. However, the theory of hypergraphs is less known to the general scientific community.

Recently Boixo et al. [2017] proposed to consider line graphs of the classical tensor networks, which has multiple benefits. First, it establishes the connection of quantum circuits with probabilistic graphical models, allowing for knowledge transfer between the fields. Second, these graphical models avoid the overhead of traditional diagrams for diagonal tensors. Moreover, treewidth is a universal measure of complexity for these models, and links the complexity of quantum states to the well-studied problems in graph theory, a topic we hope to explore in future works. Additionally, simple parallelization of the simulator is possible, as demonstrated in the work of Chen et al. [2018b]. The only disadvantage of the line graph approach was that it is limited usability to simulate subtensors of amplitudes, which we are going to address in this chapter.

Lastly, we have to mention that multiple approximate methods are currently being de-

veloped for circuit simulation. Very recent work of Carrasquilla et al. [2019] presents a neural-network based approach. Pan et al. [2019] devised an approximate algorithms based on tensor network transformation. Extension of our approach with approximation techniques may be a prospective direction of research.

## 2.3 Quantum circuit simulation algorithm

In this section we describe a procedure for efficient quantum circuit evaluation. We first set up the notation, and then review the current state of the art method for numerical simulation of quantum circuits.

## 2.3.1 Tensor networks and graphical models

A quantum program describes an evolution of the initial state  $|0\rangle$  of a system of n qubits. Any evolution of a physical system corresponds to a unitary operator. Thus, the result of a quantum circuit is a state  $|\psi\rangle$ , which is a linear transformation of the input state:  $|\psi\rangle = \mathcal{U}|0\rangle$ . Usually, the transformation  $\mathcal{U}$  is performed in several steps corresponding to clock cycles of a quantum computer. Suppose the transformation is described by a depth d circuit. We introduce the following notation:

$$\mathcal{U}|0\rangle = \mathcal{U}^d \dots \mathcal{U}^2 \mathcal{U}^1 |0\rangle$$

$$|s^{t+1}\rangle = \mathcal{U}^t |s^t\rangle, \quad |s^0\rangle = |0\rangle$$

(2.1)

Here  $\mathcal{U}^t$  are unitary matrices acting at the t-th clock cycle and  $|s^t\rangle$  is the state vector. In the simplest case the initial state is taken to be a product of single qubit states  $|0\rangle = |0_0\rangle \otimes \cdots \otimes |0_n\rangle$ . A naive simulation algorithm would take the initial vector  $|0\rangle$  and apply matrices  $\mathcal{U}^t$  to it. This procedure lays behind full state circuit simulation. To calculate an

amplitude of a bit string x, one would evaluate a dot product  $\langle x|s^d\rangle$ :

$$\sigma(x) = \langle x|s^d \rangle = \sum_{i=1}^n \langle x_i|s^d \rangle \tag{2.2}$$

The probability of x is then the modulus squared of the amplitude. Note, however, that it is hard to perform full state simulation efficiently. A naive algorithm would need to operate on vectors of size  $2^n$ . Also, the matrices  $\mathcal{U}^t$  are highly sparse, at least if they represent transformations achievable with single and two-qubit gates in modern experimental hardware. Here and later in the chapter, we chose to work with the following universal set of one and two-qubit gates:  $\{X^{1/2}, Y^{1/2}, CZ, T, H\}$ ; the same reasoning, however, applies to any quantum gates.

An alternative to full state simulation would be the evaluation of one or several amplitudes from Eq. 2.2 without explicitly forming  $|s^d\rangle$ . The latter approach provides several benefits. First of all, we can avoid storing the high dimensional state vector  $|s^d\rangle$  in computer memory. Second, it may be easier to use the internal structure of the operators  $\mathcal{U}^t$  to perform calculations efficiently. Let us introduce a set of variables to denote the state at different cycles of the circuit.

$$\{s\}_{i}^{t}, \quad s \in [0, 1], \quad i \in [1, n], \quad t \in [0, d]$$

(2.3)

We slightly abuse notation here, as  $|s_i^t\rangle$  denotes a state of the *i*-th qubit at *t*-th cycle, and  $s_i^t$  is a binary variable indexing this state. The same notation is used for the initial and final states, e.g.  $|s_i^0\rangle = |0_i\rangle$  and  $|s_i^d\rangle = |x_i\rangle$ . Consider a circuit shown in Fig. 2.1.

We start with a product state  $|0\rangle$  on the right. As the program proceeds the states of individual qubits are changed by gates application. Note that the gates T and cZ do not change the basis of the single-qubit subspaces they act on (they only multiply basis vectors by constants), and hence  $|s_i^t\rangle = |s_i^{t+1}\rangle$  for those qubits. In contrast, non-diagonal gates

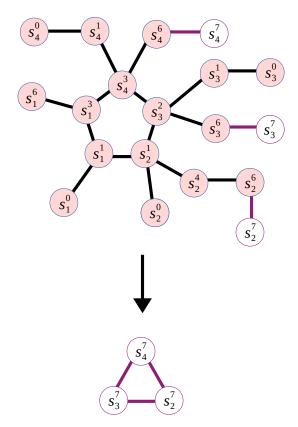

Figure 2.1: Example of quantum circuit drawn as a tensor network. The state of *i*-th qubit at *t*-th clock cycle is denoted by  $\{s\}_i^t$  (only unique states are shown, e.g.  $s_1^2 = s_1^1$  is omitted). The time flows from right to left.

$\{X^{1/2},Y^{1/2},H\}$  mix basis vectors of the appropriate qubit subspaces, and new variables  $|s_i^{t+1}\rangle$  have to be introduced for the resulting bases. On Fig. 2.1 only unique variables are shown. The expression for the single amplitude in Eq. 2.2 can be rewritten as

$$\sigma(x) = \langle x | \mathcal{U} | 0 \rangle =$$

$$\sum_{\{s_i^t\}} \langle x_i | \mathcal{G}_i^d | s_i^{d-1} \rangle \dots \langle s_i^{t+1} s_j^{t+1} | \mathcal{G}_{ij}^t | s_i^t s_j^t \rangle \dots \langle s_i^1 | \mathcal{G}_i^1 | 0_i \rangle$$

$$\mathcal{G}_i^t \in \{X^{1/2}, Y^{1/2}, T, H\}, \qquad \mathcal{G}_{ij}^t = cZ$$

$$(2.4)$$

The Eq. 2.4 can be interpreted as a discrete Feynman path integral as it represents a sum over all 'paths' to go from  $|0\rangle$  to  $|x\rangle$ . On the other hand, one can easily see that the evaluation of the amplitude  $\sigma(x)$  in Eq. 2.4 is equal to the contraction of a tensor network shown in Fig. 2.1. For the introduction to the graphical notation used for tensor networks please refer to [Cichocki et al., 2016]. It is well known, however, that the numerical cost of tensor

Figure 2.2: The mapping between two graph-based notations of tensor networks.

contractions dramatically depends on the order of operations. Following Markov and Shi [2008] let us introduce another type of graphical models to denote quantum circuits, which better suits for the estimation of numerical costs.

In traditional notation, a tensor network is represented by a graph with nodes standing for tensors and edges denoting their indices. In the new notation, we use nodes to denote unique indices, and tensors are denoted by cliques (fully connected subgraphs). Note that tensors, which are diagonal along some of the axes and hence can be indexed with fewer variables, are depicted by cliques of size lower than the dimension of the corresponding tensor. For a special case of vectors or diagonal matrices, self-loop edges are used. Fig. 4.1 lists the notation for the gates used in this work.

A graphical model, which is equivalent to the circuit in Fig. 2.1, is shown in Fig. 2.3 (self loops are omitted for simplicity). As was pointed out by Boixo et al. [2017] this representation of tensor contractions is traditional in Bayesian network literature. Notice that provided a quantum circuit in a traditional form, one can easily build its probabilistic model representation. To do that, one has to replace all edges carrying non-equivalent single-qubit states with nodes, and all gates with cliques. The diagonal structure of CZ gate tensors leads to significant simplification of the resulting graphs. This is discussed in more detail in

Figure 2.3: Alternative representation (graphical model) of the circuit in Fig. 2.1. Gate tensors are shown in red, self-loops are omitted.

#### Chapter 3

## 2.3.2 Simulation of quantum circuits

Having set up the notation, let us proceed with a description of a basic procedure for the evaluation of tensor networks. This algorithm was developed in the context of probabilistic models under the names of bucket elimination [Dechter, 2013] or the variable elimination algorithms [Marsland, 2011].

As an example, let us consider the contraction of a simple tensor network:

$$\sum_{ijklmn} A_{ij} B_{jk} C_{ikl} D_{km} E_{ln} F_{mn} = \sigma \tag{2.5}$$

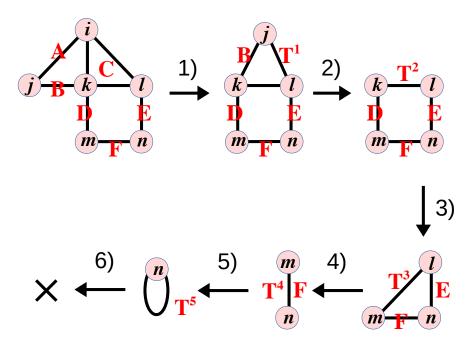

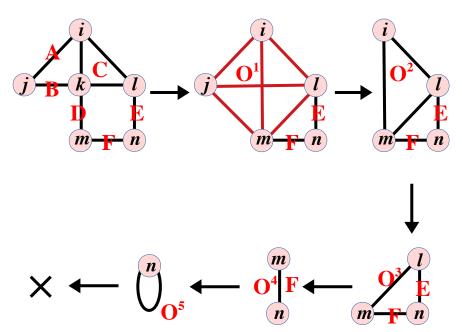

The graphical model of this network is shown in Fig. 2.4. We choose the order of indices as  $\pi = \begin{pmatrix} i & j & k & l & m & n \\ 1 & 2 & 3 & 4 & 5 & 6 \end{pmatrix}$ , e.g. i is first, j is second etc. In the bucket elimination procedure the indices are contracted one at a time in order fixed by  $\pi$ , until no indices is left. The sequence

Figure 2.4: Contraction of a tensor network from Eq. 2.5 in graphical form. The sequence of contractions  $\pi$  is the same as in Eq. 2.6. Labels of tensors are shown in red.

of the expressions evaluated in the algorithm is listed below. Assuming the dimensions of all indices is L, we also list numerical costs of the operations.

1)

$$\sum_{i} A_{ij}C_{ikl} = T_{jkl}^{1} \quad \mathcal{O}(L^{4})$$

2)  $\sum_{j} B_{jk}T_{jkl}^{1} = T_{kl}^{2} \quad \mathcal{O}(L^{3})$

3)  $\sum_{k} D_{km}T_{kl}^{2} = T_{ml}^{3} \quad \mathcal{O}(L^{3})$

4)  $\sum_{l} E_{ln}T_{ml}^{3} = T_{nm}^{4} \quad \mathcal{O}(L^{3})$

5)  $\sum_{m} T_{nm}^{4} = T_{n}^{5} \quad \mathcal{O}(L^{2})$

6)  $\sum_{n} T_{n}^{5} = \sigma \quad \mathcal{O}(L)$

The sequence of transformations of the graphical model corresponding to Eq. 2.6 is shown in Fig. 2.4 2) - 6).

At each step, the contracted variable is removed from the graph, and all its neighbors form a clique. This clique corresponds to the next intermediate in the sequence. Note that the order of the cliques formed at each step corresponds to the exponent of the scaling of numerical cost.

The computational cost of the tensor network contraction is highly dependent on the order of operations. To illustrate this let us consider an alternative order  $\tilde{\pi} = \begin{pmatrix} k & j & i & l & m & n \\ 1 & 2 & 3 & 4 & 5 & 6 \end{pmatrix}$  for evaluating the Eq. 2.5. The corresponding sequence of graphical models is shown in Fig. 2.5. Note that the size of the maximal clique corresponding to order  $\tilde{\pi}$  is four, which translates to the intermediate of order four and the overall scaling  $\mathcal{O}(L^5)$  of the numerical effort.

Figure 2.5: Alternative contraction of a tensor network in Eq. 2.5. The maximal clique of size 4 is highlighted in red. This sequence of contractions is not optimal.

Finding the elimination order of a graph is equivalent to the calculation of its tree decomposition; the size of the maximum clique of an order  $\pi$  is treewidth + 1. Tree decomposition is NP-hard for general graphs [Bodlaender, 1994], and a similar hardness result is known for the optimal tensor contraction problem [Chi-Chung et al., 1997]. However, several exact and

approximate algorithms for tree decomposition were developed in graph theory literature; for references, please see [Gogate and Dechter, 2004; Bodlaender et al., 2006; Kloks, 1994; Bodlaender, 1994; Kloks et al., 1993]. For our simulations, we used an exact algorithm of V. Gogate[Gogate and Dechter, 2004]. Having reviewed the procedure for calculation of a single amplitude, let us consider the case of multiple amplitudes, which is the main topic of this chapter.

## 2.4 Batch circuit simulation

## 2.4.1 Simulation of multiple amplitudes

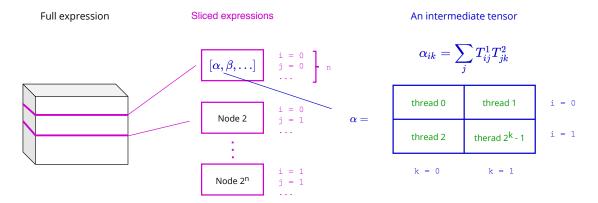

The procedure we used to calculate single amplitude can be easily extended to calculate any subtensor of the full amplitude tensor. Suppose we are interested in amplitudes of two bitstrings differing only in the value of the first qubit, e. g.  $x^0 = (0, s_2^d, \dots, s_n^d)$  and  $x^1 = (1, s_2^d, \dots, s_n^d)$ . Let us note that the expressions for the amplitudes of  $\sigma^0$  and  $\sigma^1$  differ only by the value of the state vector of the first qubit, which is  $|0\rangle$  and  $|1\rangle$  respectively. One could merge both expressions and introduce an additional variable  $s_1^{d+1}$  to index the result  $\sigma(s_1^{d+1})$  (which is a vector of size two). The same procedure can be implemented for any combination of output qubits; thus, any subtensor of the full amplitude tensor can be encoded. A graphical representation of the extended amplitude expression is shown in Fig. 2.6. We have to mention that the same procedure can be used not only to evaluate the probabilities of multiple output states, but also the evolution of multiple input states. This approach can be used to simulate the dynamics of mixed states, although we will not elaborate on this in the current chapter.

In order to evaluate multiple amplitudes, the resulting extended expressions have to be contracted only partially (the indices of the amplitude subtensors should not be summed over). Partial contraction can be achieved by stopping the bucket elimination algorithm [Dechter,

Figure 2.6: Evaluation of amplitude subsets.

Top - extended amplitude expression to evaluate all amplitudes of qubits 2, 3, 4; Bottom - resulting amplitude tensor.

2013; Marsland, 2011] when all necessary indices are eliminated and (possibly) merging the final set of tensors. Notice that the result of the evaluation of all amplitudes for c qubits will result in a tensor with  $2^c$  elements, which will be mirrored by a clique (a fully connected subgraph) with c nodes in our graphical notation (Fig. 2.6, bottom).

After selecting a subset of nodes to leave in the result, one still faces a problem of choosing an optimal order of variable elimination to implement partial contractions. Let us turn to the discussion of a possible solution.

## 2.4.2 Node ordering and chordal graphs

To properly introduce the procedure of finding elimination orders for partial contractions, let us first highlight the connection of elimination orders and chordal graphs. Chordal graphs (also called triangulated graphs) are the ones that do not have cycles of length higher than 3. Many problems that are hard on general graphs can be solved on chordal graphs in polynomial time (for example, the Maximum Clique problem[Gavril, 1972]). An extensive introduction to the properties of chordal graphs and related algorithms can be found in [Blair and Peyton, 1993].

We will employ chordal graphs because of their relation to node orderings. Consider the bucket elimination procedure described before, but without node removal. Specifically, given a graph G and a node order  $\pi$ , one would loop over the nodes according to  $\pi$  and for each node connect all of its neighbors who have higher order in  $\pi$ . It can be shown[Blair and Peyton, 1993] that this procedure will always produce a chordal graph. Indeed, if the initial graph had any cycle with four or more nodes, connecting the neighbors of any node in the cycle will introduce a chord (a link between nodes in the cycle), thus breaking a cycle into smaller, three node cycles. The resulting chordal graph is also called a fill-in graph in this context.

A formal algorithm for building a fill-in graph H given an initial graph G and an elimina-

Figure 2.7: Building a chordal graph from the elimination order The graph corresponds to the tensor network in Eq. 2.5. The nodes are labeled according to their order.

tion order  $\pi$  is listed in Alg. 1. A corresponding graphical representation of the algorithm is provided in Fig. 2.7. An important remark has to be made here. Any elimination order  $\pi$  will produce a chordal graph, but this does not imply that there is a one-to-one correspondence. Multiple orders can result in the same fill-in graph [Tarjan and Yannakakis, 1984]; we will employ this fact in the next section.

## Algorithm 1 Building chordal graph from the elimination order

```

Input: G = (V, E), \pi : V \to \mathcal{N}, \quad \pi = \{(v_i, i)\}_{i=1}^{|V|}

Output: H = (V, \tilde{E}), H is chordal

1: function Build Chordal Graph(G, \pi)

\tilde{E} \leftarrow E

2:

for i \in [1, ..., |V|] do

3:

v \leftarrow \pi^{-1}(i)

4:

U = \emptyset

5:

for w in neighbors(v) do

6:

if \pi(w) > i then

7:

U \leftarrow U \cup w

8:

end if

9:

10:

end for

for x, y in pairs(U) do

11:

\tilde{E} \leftarrow \tilde{E} \cup (x, y)

12:

end for

13:

end for

14:

15: end function

```

The size of the maximum clique in the fill-in graph equals treewidth by construction [Bodlaender et al., 2006]. The problem of searching the best elimination order for a graph G thus can be formulated in terms of the search of an optimal fill-in graph. Formally, given a graph G = (V, E) the task of finding an elimination order  $\pi$  with minimal treewidth is equivalent to finding a chordal graph  $H = (V, \tilde{E}), \ \tilde{E} \in E$ , such that the size of its maximum clique is minimized.

Provided a chordal graph H is found, any of its elimination orders that does not introduce

additional edges, and hence does not change the graph H, will have the same treewidth. Chordal graphs thus provide means of building equivalent (in terms of treewidth) elimination orders. In contrast with arbitrary graphs, finding elimination orders of chordal graphs can be done in linear time [Tarjan and Yannakakis, 1984]. We now turn to the description of the procedure of building of equivalent elimination orders of chordal graphs.

## 2.4.3 Finding restricted elimination orders

Let us now find an optimal elimination order for multiple amplitude evaluation, as described in Sec. 2.4.1. In essence, we want to find an order with minimal treewidth, such that some set of nodes will be at the end of this order. Putting it formally, for a graph G = (V, E) and a subset of nodes  $C \in V$  we want to find an order  $\pi$  with minimal treewidth, such that for any nodes  $v \in C$  and  $v \in V \setminus C$  the order of v is higher than the order of v:  $\pi(v) > \pi(w)$ .

Our idea is to calculate an optimal unrestricted elimination order  $\tilde{\pi}$  (not necessary having C at the end), and then to use the connection between the elimination orders and chordal graphs to transform it to the desired order  $\pi$ . Essentially, we employ the result of Bodlaender [Bodlaender et al., 2006], to devise a procedure for building  $\pi$ . Our approach is outlined below:

- 1. Check if C induces a clique in G. If G[C] is not a clique, turn G[C] into a fully connected subgraph. This step ensures that the condition stated in (Ref. [Bodlaender et al., 2006], Lemma 10) is satisfied: if C is a clique, then there always exists an elimination order with C at the end. A graph  $\tilde{G}$  is produced as a result of (possibly) turning C into a clique.

- 2. Find an elimination order  $\tilde{\pi}$  of  $\tilde{G}$  using an exact (NP-hard) or a heuristic algorithm. We use the branch and bound algorithm of Gogate[Gogate and Dechter, 2004] with the time limit of 60 seconds (to obtain an exact solution the algorithm has to be given a very long time).

- 3. Build a chordal graph H using Alg. 1.

- 4. Provided with a set C and a chordal graph H, construct a new order  $\pi$  with the help of the Restricted Maximum Cardinality Search (MCS) algorithm. The order  $\pi$  has same treewidth as the order  $\tilde{\pi}$  and nodes in C are placed at the end in  $\pi$ .

Essentially, in our approach, we transform an arbitrary solution to the Tree decomposition problem to the one that satisfies our restrictions (places all nodes in C to the end) and has the same quality (same treewidth). The last ingredient to complete the procedure is the Restricted Cardinality Search algorithm. We modified the original algorithm from Ref. [Tarjan and Yannakakis, 1984]. The resulting pseudocode is provided in Alg. 2.

## **Algorithm 2** Computing an elimination order with a set of nodes C at the end

```

Input: H = (V, E), H is chordal, C \in V, C is clique

Output: \pi: V \to \mathcal{N}, \ \pi = \{(v_i, i)\}_{i=1}^{|V|}

1: function RESTRICTED-MCS(H, C)

for v \in V do

2:

cardinality(v) \leftarrow 0

3:

4:

end for

for i \in [|V|, |V| - 1, \dots, 1] do

5:

if C \neq \emptyset then

6:

pick v \in C, C \leftarrow C \setminus \{v\}

7:

else

8:

pick v \in V with maximum cardinality

9:

V \leftarrow V \setminus \{v\}

10:

end if

11:

\pi \leftarrow \pi \cup (v,i)

12:

for w \in \text{neighbors}(v), w \notin \pi \text{ do}

13:

cardinality(w) \leftarrow cardinality(w) + 1

14:

end for

15:

end for

16:

17: end function

```

In the Alg. 2 each node v of the graph H is assigned a counter "cardinality", which holds the number of labeled neighbors of v. At each step, we label the next node with maximal cardinality, breaking ties arbitrarily. The order is built in a reversed form. In the beginning, nodes in C are labeled (to be last), and then the rule stated before is applied. Note that if at step i a node v is selected, then in the next steps all neighbors of v, which belong to the maximal clique K,  $v \in K$  will be labeled. Overall, the procedure in Alg. 2 is polynomial in the number of nodes |V|.

Let us now demonstrate the benefits of the proposed approach with numerical examples.

## 2.4.4 Numerical examples

The methods developed in previous sections were used to implement a quantum circuit simulator. As numerical examples we use the simulation of random quantum circuits from the work of Boixo et al. The qubits are arranged in a square grid of size  $k \times k$  and a set of gates  $\{X^{1/2}, Y^{1/2}, cZ, T, H\}$  is applied in a predefined pattern. This circuit choice can be implemented in superconducting quantum processors. [Chen et al., 2014] The reader is referred to [Boixo et al., 2017] to learn more details about the motivation of these random circuits. The dataset with random circuits of Boixo et al., which we used in this work, is available online [Boixo, 2019]. Here we are interested only in the numerical cost and the memory usage to evaluate amplitudes.

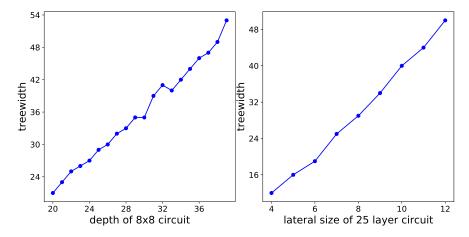

In Fig. 2.8, the dependence of treewidth  $\nu$  on the size and depth of the random circuits is shown. Let us recall that the number of floating-point operations scales as  $O(2^{\nu+1})$  and the required memory as  $O(2^{\nu})$ . The complexity of simulation grows exponentially with the volume of random quantum programs, which was the original motivation for considering them as a test bench for demonstrations of quantum supremacy [Boixo et al., 2018].

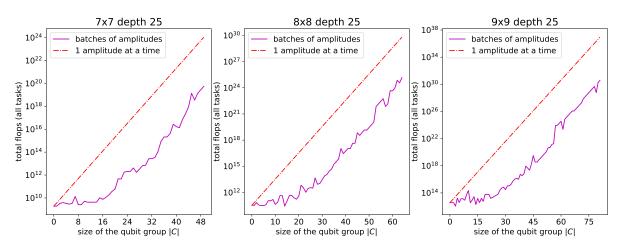

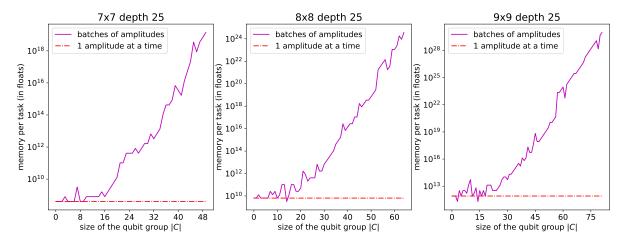

In Fig. 2.9, the advantage of batch simulation comparing to single amplitude at a time is shown. The steep growth of the flop cost is significantly ameliorated. We recall that a clique C is introduced into the computational graph when the evaluation of all amplitudes of |C| qubits is performed. While this clique is less than the treewidth of the computational graph, there is only a negligible increase in the computational cost. Batch simulation, however, requires copious amounts of memory, as shown in Fig. 2.10. The results we obtain illustrate a usual CPU/memory trade-off seen in numerical algorithms. Notice also that the curves for

Figure 2.8: Treewidth dependence on the size of a random quantum circuit. Left - dependence of treewidth on the depth of a random circuit, Right - dependence of treewidth on the number of qubits.

total amount of memory and flop are almost indistinguishable. This result is caused by the fact that during the evaluation of the amplitudes one needs to contract high order tensors over an index of size 2: the flop cost of the most expensive contraction equals the size of the largest tensor times 2.

Figure 2.9: Total flop requirements for the simulation of a typical random circuit of varying size. Estimated number of floating point operations for the simulation of the full subset of amplitudes of |C| qubits (there are  $2^{|C|}$  amplitudes). In case of one amplitude at a time simulation a combined cost of all tasks is drawn.

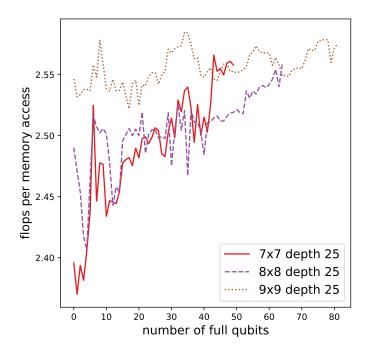

Lastly, we provide the dependence of the number of operations per memory access for circuits of different sizes in Fig. 2.11. In all cases, the values are in the range of O(L), where

Figure 2.10: Minimal memory requirement for the simulation of a typical random circuit of varying size

Shown is the predicted number of memory in floating point units per single task (simulation of either 1 amplitude or a batch of amplitudes). Notice the high similarity with Fig. 2.9: the ratio of flop to memory access is almost constant in logarithmic scale.

L=2 for qubits. This dependence demonstrates that despite a potential for massive parallelism [Chen et al., 2018b], the problem of tensor contraction is essentially memory bound, and an efficient algorithm has to very carefully overlap data transmission and computations. Comparing to the contraction of matrices, where extremely efficient algorithms were developed [Dongarra et al., 1988] using CPU cache and vectorized operations, a general tensor contraction is more challenging for optimization.

# 2.5 Conclusion and comparison

We introduced a novel way to optimize graphical model algorithms for quantum circuits simulation. Our approach allows the user to select between the amount of memory consumed and the speed of the calculation; thus, the code can be adapted to the available hardware. We emphasize that our approach is not restricted to quantum circuit simulation, but can be used to evaluate partial contractions of general tensor networks. To our best knowledge, this is a first of a kind method which evaluates partial contractions efficiently, e.g., its resource requirements depend only on the treewidth of the expression's graph.

Figure 2.11: Floating point to memory access ratio during the simulation of random circuits of varying size

Many more improvements to the tensor contraction strategy can be proposed. Here we explicitly avoided the discussion of parallel simulation, and defer it to a future work. Also, since the structure of modern computer memories combines devices with varying latency and size, some research is needed on the proper scheduling of the operations, especially in the parallel case.

#### CHAPTER 3

# DIAGONAL GATES APPROACH FOR OPTIMIZING QUANTUM CIRCUIT SIMULATION

This chapter is adapted from Lykov and Alexeev [2021].

#### 3.1 Abstract

In this work we present two techniques that increase the performance of tensor-network based quantum circuit simulations. The techniques are implemented in the QTensor package and benchmarked using Quantum Approximate Optimization Algorithm (QAOA) circuits. The techniques allowed us to increase the depth and size of QAOA circuits that can be simulated. In particular, we increased the QAOA depth from 2 to 5 and the size of a QAOA circuit from 180 to 244 qubits. Moreover, we increased the speed of simulations by up to 10 million times. Our work provides important insights into how various techniques can dramatically speed up the simulations of circuits.

## 3.2 Introduction

Several approaches have been employed to simulate quantum circuits. The major types include the state-vector evolution approach [De Raedt et al., 2007; Smelyanskiy et al., 2016; Häner and Steiger, 2017; Wu et al., 2019, 2018b,a], linear algebra open system simulation [Otten, 2020], and tensor network contractions [Markov and Shi, 2008; Pednault et al., 2017; Boixo et al., 2017; Lykov et al., 2020b]. All these simulators have various advantages and disadvantages. For example, the state-vector evolution approach, while being relatively easy to implement, has an exponential memory requirement with respect to the number of qubits in the circuit, which is a major bottleneck preventing quantum simulations beyond approximately 46 qubits on modern supercomputers.

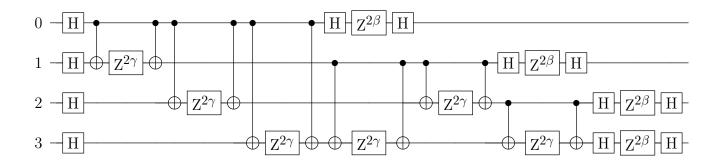

Figure 3.1: Quantum circuit that generates QAOA ansatz state for MaxCut problem on a 4-node complete graph. This widely used decomposition of QAOA into common set of basis gates is not optimal for the classical simulation of the output state.

In our opinion the most promising type of simulator is the tensor network contraction approach. It is especially efficient for simulating shallow-depth circuits. This approach can be sensitive to the connectivity of a quantum circuit and the types of gates. In this chapter we describe the tensor network simulator implementation and show two optimization techniques that enable dramatic speedup of simulations. We use quantum circuits from the Quantum Approximate Optimization Algorithm (QAOA) algorithm since it is a promising candidate for demonstrating quantum advantage and benchmarking quantum devices.

All simulations in our work used QTensor [Lykov, 2021], developed at Argonne National Laboratory. It is a quantum circuit simulator that uses a tensor network contraction approach with a special focus on the simulation of QAOA circuits. It supports simulating both probability amplitudes and energy expectation values.

In the following section we introduce the tensor network contraction approach and describe the QAOA quantum circuits. In particular, we show how the usage of the Feynman path formalism provides the possibility for optimization. We then describe the optimization techniques and the resulting speedup of simulations. The final section contains our conclusions and further directions of research.

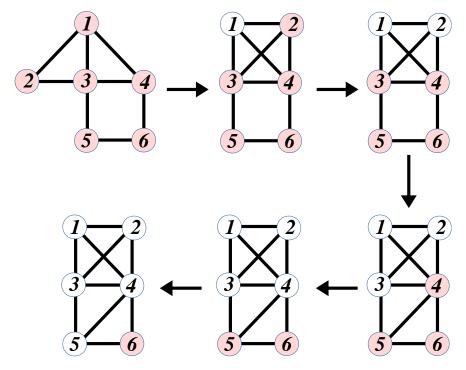

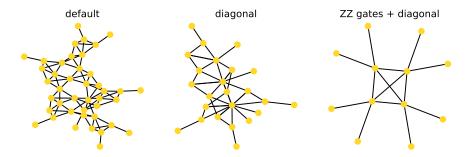

Figure 3.2: Line graphs of tensor networks for calculating QAOA ansatz state using different optimizations. "Default" and "diagonal" show line graphs of tensor network for the circuit shown in Figure 3.1, using a full-matrix gates and diagonal gates approach, respectively. "ZZ gates + diagonal" is obtained by using the diagonal gates approach on a simplified quantum circuit obtained by applying Equation 3.4. This figure demonstrates how improving the conversion of a quantum algorithm to a tensor network can reduce the complexity of the network, providing speedups for both finding contraction order and the contraction itself.

#### 3.3 QAOA algorithm

The QAOA algorithm, introduced by Farhi and Goldstone in 2016 [Farhi and Harrow, 2016], is a seminal hybrid quantum-classical algorithm for approximate optimization. The algorithm can be used to find approximate solutions to NP-complete combinatorial optimization problems. Here we will demonstrate how it works to solve the MaxCut problem and all benchmarking simulations are performed for MaxCut, but this work also applies to other types of tensor network simulations.

The goal of the MaxCut problem is to color all vertices of a given graph G=(V,E), such that the number of edges between the two resulting parts of the graph is maximized. The cost function for MaxCut is  $C=\frac{1}{2}\sum_{< jk>\in E} -Z_jZ_k+1$ , where  $Z_i$  is a label of each vertex. To solve this problem using QAOA, one has to find optimal parameters for the parametrized ansatz state  $|\gamma\beta\rangle$  such that the expectation value of the Hamiltonian cost function  $\langle\gamma\beta|\hat{H}|\gamma\beta\rangle$  is maximized. The ansatz state depends on two parameter vectors  $\gamma$  and  $\beta$ . The length of the parameter vector, denoted p, is an important parameter that defines the quality of the solution. For a QAOA depth p with MaxCut on graph G=(V,E), the ansatz state is equal

$$|\gamma\beta\rangle_p = \prod_{k=1}^p U_C(\gamma_k)U_B(\beta_k)|+\rangle,$$

(3.1)

where  $U_B(\beta) = e^{-i\beta \sum_{j \in V} X_j}$  and  $U_C(\gamma) = e^{-i\frac{\gamma}{2} \sum_{(i,j) \in E} (I - Z_i Z_j)}$ . Substituting  $U_B$  and  $U_C$  into (3.1) and discarding the global phase, we obtain

$$|\gamma\beta\rangle_p = \prod_{q=1}^p \left[ \prod_{ij\in E, k\in V} e^{i\gamma_q Z_i Z_j} e^{-i\beta_q X_k} \right] |+\rangle. \tag{3.2}$$

A quantum circuit that generates the ansatz state for MaxCut on a fully connected 4-node graph is shown in Figure 3.1. For a more detailed description of QAOA see [Farhi and Harrow, 2016].

The optimal  $\gamma$ ,  $\beta$  parameters correspond to the minimum of the Hamiltonian cost function expectation value, which can be calculated as  $E = \langle \gamma \beta | C | \gamma \beta \rangle$ . Note that C is a sum of |E| elements, where each element corresponds to an edge of the original graph on which we solve MaxCut. Hence, the expectation value is  $E = \sum_k E_k$ , where each element is a matrix element of a local operator that acts on two qubits. This locality gives room for efficient optimization by canceling all the conjugate gates that commute through that local operator. This optimization, called lightcone optimization, was introduced by Farhi and Goldstone in [Farhi and Harrow, 2016].